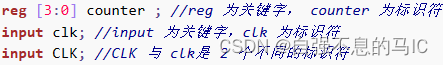

关键字和标识符

关键字:

-关键字是 Verilog 中预留的用于定义语言结构的特殊标识符。

-关键字全部小写

标识符:

-组成:字母、数字、下划线、美元$【开头:字母或下划线】

-分大小写

例子:

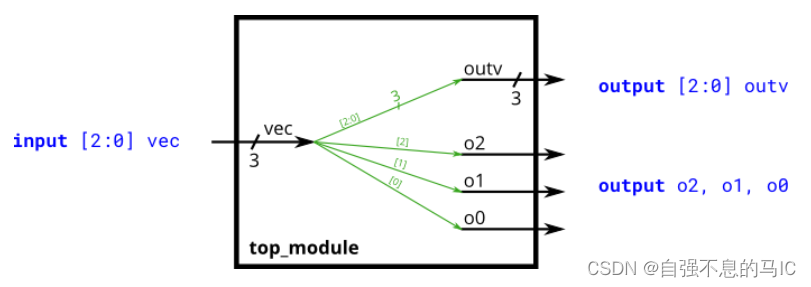

向量(vertor)

向量是一组 wire 信号的集合,通过赋予这一组信号的集合一个名称,以便于访问其中的 wire 信号,一般将向量视为位宽超过 1 位的 wire 信号。

input wire [3,-2] z; //6bit复数作位宽 -2代表倒数第二位数

reg [7:0] mem [255:0] //8位宽数组,每组包含256个元素[寻址范围0-256]例1:片选1个信号

例2:输出 16 位输入信号的高 8 位和低 8 位

高8位 [15:0] 低8位 [7:0]

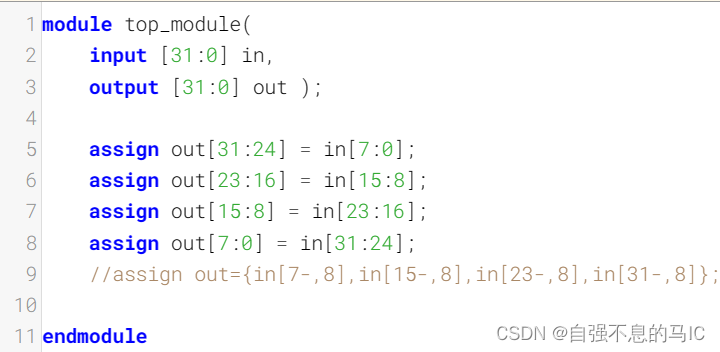

例3:大小端交换

例4: 模块有两个 3bit 宽的输入变量 a,b ,要求输出 a,b 逐位或的,a,b 逻辑或以及 a,b 按位取反的结果,其中 b 在高位 不懂

9942

9942

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?