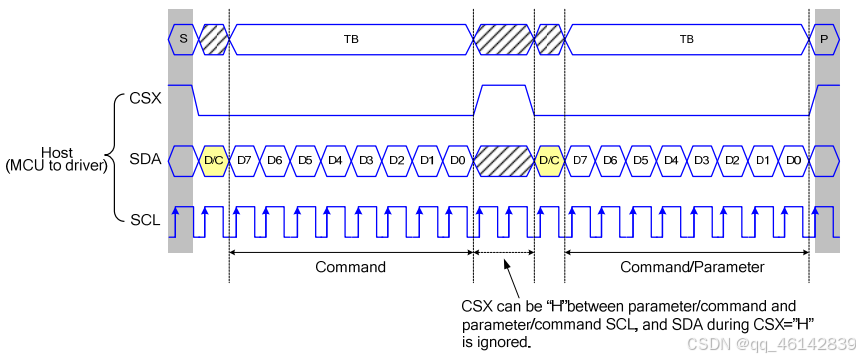

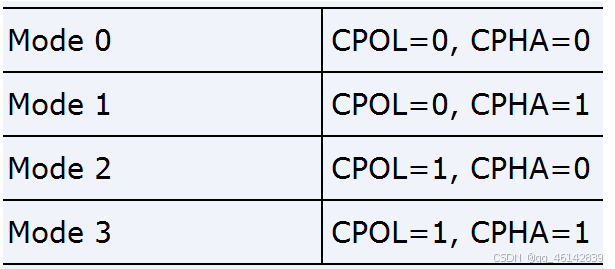

由数据手册可知,在CS(片选信号)下降沿之前,SCL(时钟线)可以是高电平也可以是低电平,此时SCL的状态是被忽略的。因此,SPI的时钟极性为高电平(CPOL=1),也可以为低电平(CPOL=0)。

当CS信号有效时(CS的下降沿),根据数据手册,采样都在SCL的上升沿发生。由此可得:

当CPOL=0时,SCL初始为低电平,此时采样应该发生在第一个边沿,即CPHA=0;

当CPOL=1时,SCL初始为高电平,此时采样应该发生在第二个边沿,即CPHA=1。

所以ST7789V可以支持两种模式,分别为mode0和mode3。(测试时发现mode2也能正常显示,mode1不能正常显示,这是什么原因?)

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?