描述

在数字芯片设计中,经常把实现特定功能的模块编写成函数,在需要的时候再在主模块中调用,以提高代码的复用性和提高设计的层次,分别后续的修改。

请用函数实现一个4bit数据大小端转换的功能。实现对两个不同的输入分别转换并输出。

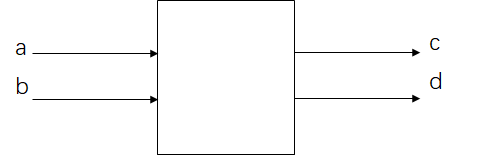

程序的接口信号图如下:

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述:

clk:系统时钟

rst_n:异步复位信号,低电平有效

a,b:4bit位宽的无符号数

输出描述:

c,d:8bit位宽的无符号数

解答:

分析:

这个模块实现两个数据的大小端转换,使用generate函数刚好解决这个问题。

代码如下:

`timescale 1ns/1ns

module function_mod(

input logic [3:0]a,

input logic [3:0]b,

output logic [3:0]c,

output logic [3:0]d

);

genvar i;

generate for (i=0;i<4;i=i+1) begin

assign c[i] = a[3-i];

assign d[i] = b[3-i];

end

endgenerate

endmodule

791

791

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?