1、CPU的功能:程序控制、操作控制、时间控制、数据处理;

程序控制:CPU通过执行指令来控制程序的执行顺序;

操作控制:一条指令功能的实现需要很多操作信号来完成,CPU 产生每条指令的操作信号并将操作信号送往不同的部件,控制相应的部件按指令的功能要求进行操作;

时间控制:CPU对各种操作进行时间上的控制;

数据处理:CPU 通过对数据进行算术运算及逻辑运算等方式进行加工处理,数据加工处理的结果被人们所利用。

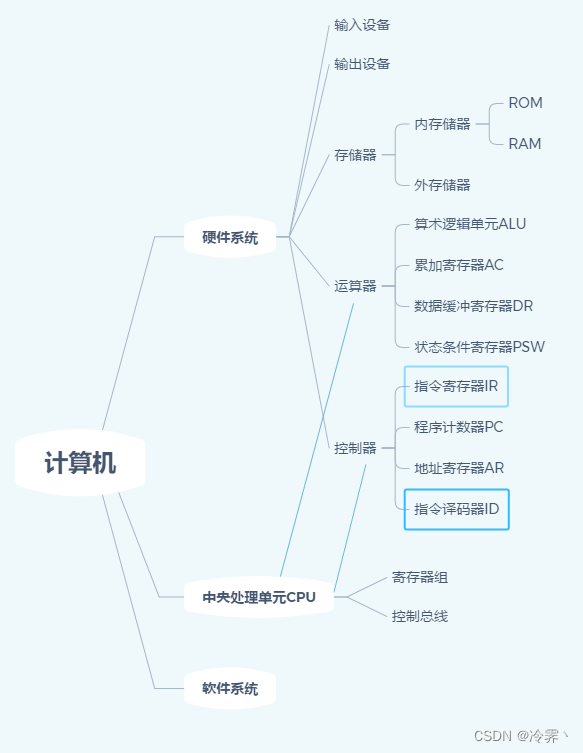

2、计算机系统组成

3、数据表示:原码、反码、补码、移码。(0正 1负)

4、移码:如果机器字长为N,偏移量为,则[X]移 =

+ [X]补 (X为纯整数);[X]移 = 1+X (X为纯小数)

5、IEEE754:符号位(1位,0正1负)+阶码(8位,+127)+尾数(23位,小数点在最高位之后,随后省略最高位)

6、浮点数加减:0操作数检查,对阶操作(小阶变大阶),尾数加减(阶码用双符号位,尾数用单符号位),结果规格化,舍入处理(判定溢出)。

7、常用校验码:奇偶校验吗(只能检错)、海明码(纠错加检错)、循环冗余校验码(CRC)。

8、计算机体系结构分类:单处理系统、并行处理与多处理系统、分布式处理系统。

9、指令集的发展:

CISC(复杂指令集计算机):增强原有指令的功能,用更为复杂的新指令取而代之;

RISC(精简指令集计算机):减少指令总数简化指令功能,优化编译降低复杂度。

10、指定控制方式:顺序方式、重叠方式、流水方式。

11、RISC中的流水线技术:超流水线技术,超标量技术,超长指令字技术。

12、并发性的解决:阵列处理机,并行处理机,多处理机。

13、主存与cache地址映射方式:

全相联映射:将主存一个块的地址与内容一起存入cache中,拷贝灵活但是比较器电路难设计实现;

直接映射:一个主存块只能拷贝到cache的特定行上去,硬件简单成本低但是容易冲突效率下降;

组相联映射:主存块放到哪个组是固定的,但是放到哪一行是灵活的,折中办法广泛采用。

14、虚拟存储器:

页式:页表硬件小,查表速度快但不利于存储保护;

段氏:界限分明便于程序的模块化设计,易于编译修改和保护,但主存利用率低,产生大量碎片,查表速度慢;

段页式:折中办法,广泛采用,但地址变换速度比较慢。

15、计算机与外设数据交换:无条件传送,查询方式传送,中断方式传送,直接存储器存取方式(DMA):CPU仅在过程开始和结束时有处理,过程中DMA占用系统总线传送数据。

16、多中断处理办法:多中断信号线法,中断软件查询法,菊花链法,总线仲裁法,中断向量表法。

17、总线分类:

内部总线:芯片的互连;

系统总线:CPU,内存,接口等的连接;

外部总线:数据交换。

18、信息安全5要素:机密性,完整性,可用性,可控性,可审查性。

19、加密技术:

对称加密(私人密钥加密):数据加密标准(DES)+ 三重DES + RC-5 + 国际数据加密算法(IDEA) + 高级加密标准(AES);

非对称加密(公开密钥加密,比如RSA算法):加密模型 + 认证模型。

20、PKI:一种遵循既定标准的密钥管理平台,能够为所有网络应用提供加密和数字签名等密码服务及所必需的密钥和证书管理体系,必须具有权威认证机构、数字证书库、密钥备份和恢复系统、证书作废系统、应用接口。

21、计算机可靠性:

可靠性:串联系统,并联系统

;

平均无故障时间:串联系统,并联系统

。

22、计算机系统性能评测常用方法:时钟频率,指令执行速度,等效指令速度法,数据处理速率(PDR)。

729

729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?