一、3-8译码器介绍

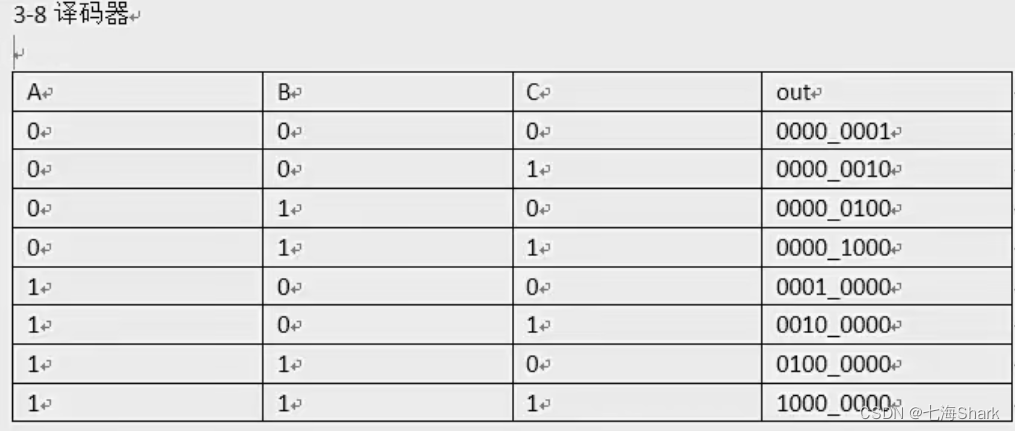

3-8译码器是三输入,八输出。当输入信号按二进制方式的表示值为N时,输出端标号为N的输出端输出高电平表示有信号产生,而其它则为低电平表示无信号产生。因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为高电平的情况下,能表示所有的输入组合。

真值表:

二、设计

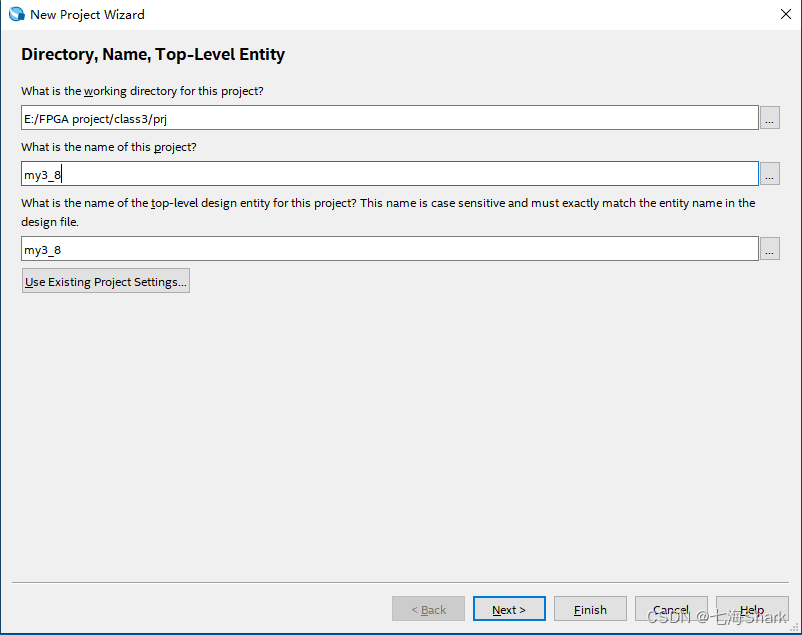

创建工程,注意项目名不能以数字开头

创建verilog文件,放置在rtl文件夹。根据真值表去编写文件

点击分析和综合,没有问题

三、验证

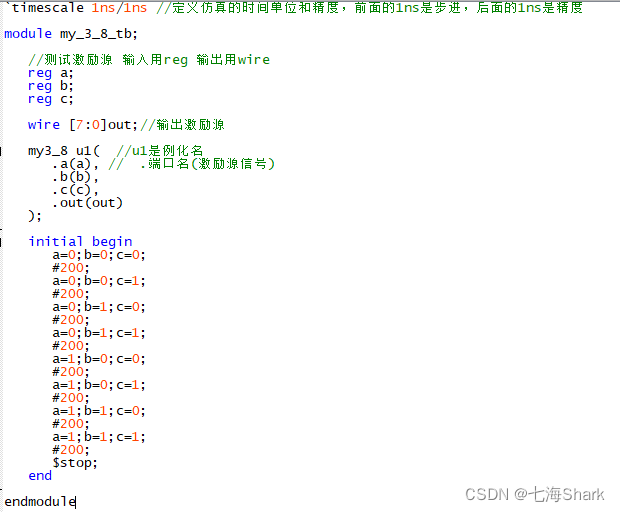

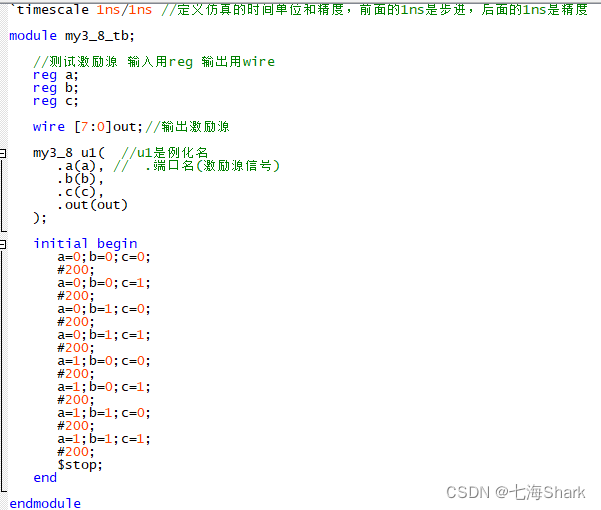

编写测试文件(testbench)

新建一个verilog文件,保存在testbench文件夹,命名为my3_8_tb.v

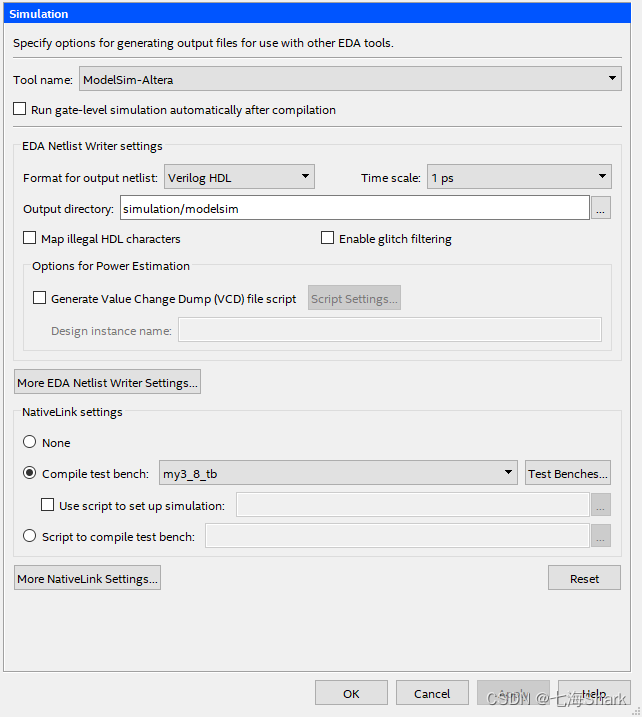

分析和综合也没问题,现在配置tb文件

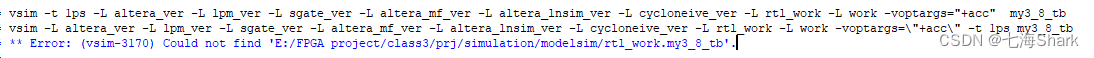

但是进行RTL仿真(前仿真)时,却出错了,不显示波形

Error: (vsim-3170) Could not find 'E:/FPGA project/class3/prj/simulation/modelsim/rtl_work.my3_8_tb'.

这是因为tb文件中的module后面接的名称与tb文件名不匹配,my后面多打了个下划线。改掉之后保存,再运行RTL仿真就没问题了。

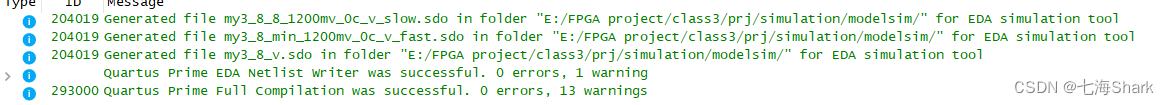

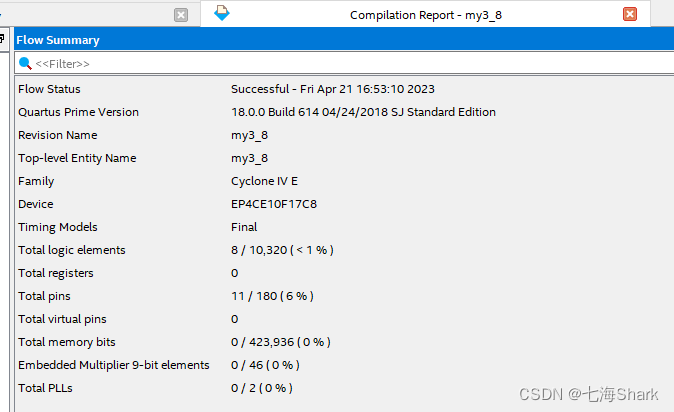

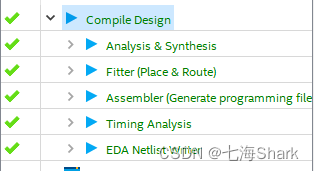

波形图很简单,不多解释。 现在进行全编译。

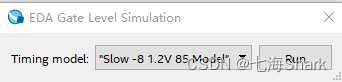

全编译没有问题,我们现在进行门级仿真(后仿真)

点击run就开始仿真了

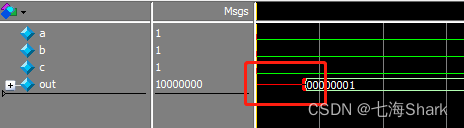

这个红线是未知态,因为out是需要输入才能产生的,存在延迟。后仿真是模拟实际情况的,必须要考虑延迟和过渡态。

这个就是过渡态,因为0000_0001变为0000_0010的时候,有两位进行翻转,而每一位的变化时间是不一致的,有的变得快,有的变得慢。图中的过渡态0000_0000,就是最低位先变化,第二位后变化的情况。虽然图里过渡态只有一种,但是过渡态是可以同时存在多种的,这是有危害的,应该想办法去避免。

从本篇文章开始进入正式的FPGA学习,3-8译码器原理很简单,用它来回顾一下之前学的设计流程是很好的。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?