分频时钟的工程应用

原理:在原来信号周期内一个周期加1,加到99总共100次,每当加到50次 新的时钟信号取1,加到99取0,这样,原来clk的100个周期是新信号的一个周期,频率减少了100倍;

/

//EDA工具平台:Vivado 2019.1 + ModelSim SE-64 10.5

//开发套件型号: STAR 入门FPGA开发套件

//版 权 申 明: 本例程由《深入浅出玩转FPGA》作者“特权同学”原创,

// 仅供特权同学相关FPGA开发套件学习使用,谢谢支持

//官方淘宝店铺: http://myfpga.taobao.com/

//微 信 公 众 号:“FPGA快乐学习”

// 欢迎关注,获取更多更新的FPGA学习资料

/

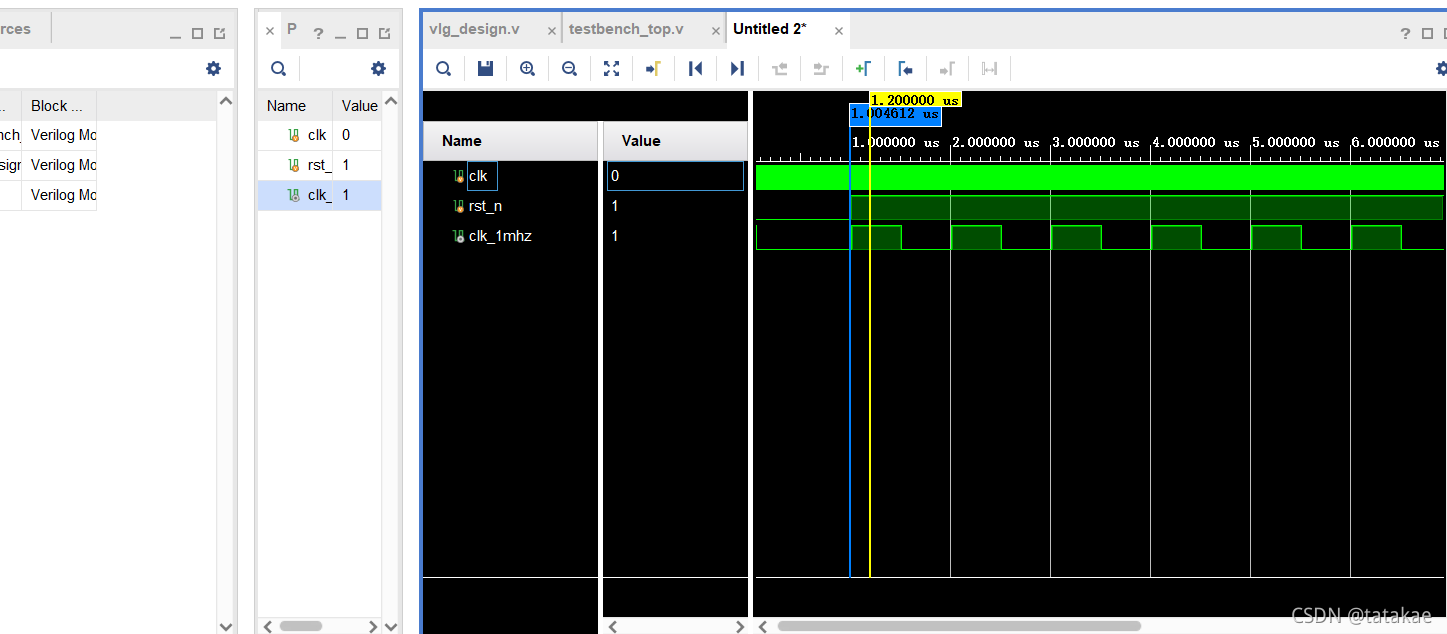

`timescale 1ns/1ps

module vlg_design(

input clk,

input rst_n,

output reg clk_1mhz

);

`define CNT_MAX 100

`define CNT_MAX_DIV2 `CNT_MAX/2

reg[7:0] cnt;

always @(posedge clk)

if(!rst_n) cnt <= 8'd0;

else if(cnt < (`CNT_MAX-1)) cnt <= cnt+1'b1;

else cnt <= 8'd0;

always @(posedge clk)

if(!rst_n) clk_1mhz <= 1'b0;

else if(cnt < `CNT_MAX_DIV2) clk_1mhz <= 1'b1;

else clk_1mhz <= 1'b0;

endmodule

testbench文件

/

//EDA工具平台:Vivado 2019.1 + ModelSim SE-64 10.5

//开发套件型号: STAR 入门FPGA开发套件

//版 权 申 明: 本例程由《深入浅出玩转FPGA》作者“特权同学”原创,

// 仅供特权同学相关FPGA开发套件学习使用,谢谢支持

//官方淘宝店铺: http://myfpga.taobao.com/

//微 信 公 众 号:“FPGA快乐学习”

// 欢迎关注,获取更多更新的FPGA学习资料

/

`timescale 1ns/1ps

module testbench_top();

//参数定义

`define CLK_PERIORD 10 //时钟周期设置为10ns(100MHz)

//接口申明

reg clk;

reg rst_n;

wire clk_1mhz;

//对被测试的设计进行例化

vlg_design uut_vlg_design(

.clk(clk),

.rst_n(rst_n),

.clk_1mhz(clk_1mhz)

);

//复位和时钟产生

//时钟和复位初始化、复位产生

initial begin

clk <= 0;

rst_n <= 0;

#1000;

rst_n <= 1;

end

//时钟产生

always #(`CLK_PERIORD/2) clk = ~clk;

//测试激励产生

initial begin

@(posedge rst_n); //等待复位完成

@(posedge clk);

repeat(10) begin

@(posedge clk);

end

#10_000;

$stop;

end

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?