基于FPGA的BISS@C、SSI、多摩川接口设计

一、BiSS接口

1.0 总线介绍

BiSS(Bidirectional Synchronous Serial Interface) C模式(单向)是一个快速同步串行接口。

采用RS422接口,波特率达到10Mbit/s;

采用LVDS接口, 波特率>10Mbit/s。

1.1 特点

每10uS传输超过64个比特,有效负载率大于80%。这反映出BiSS能承载高分辨率编码器数据。BISS 的延迟补偿技术能补偿传输线带来的信号延迟,采用两组 CRC 生成多项式分别对传感器数据与寄存器数据进行校验。

BISS协议帧还包括一位报警位和一位错误位,CRC 生成多项式可自定义。

6 位 CRC 能满足大多数应用,对于高安全场合(例如需要满足欧洲安全标准的场合),BISS可以使用 16 位 CRC。

BISS 支持从寄存器读出编码器参数,来配置数据通信。

凡是支持 BISS 标准 EDS 和 Profile 的编码器和控制系统都可以直接通信,无需修改任何程序。

1.2 帧结构

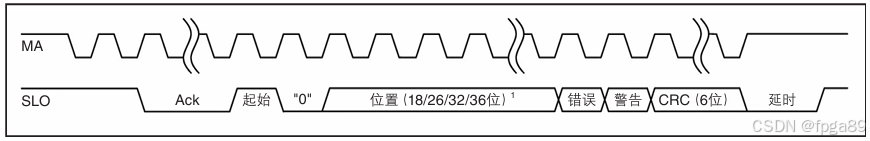

BiSS通信过程可以描述为如下几个状态的切换:

IDLE(空闲),Start Frame(帧开始),Tranmission(发送),Timeout(超时)。

MA是由DSP发出的时钟信号,用于驱动通信,SL是传感器发出来的数据信号。完成1个BiSS通信帧表示Master收到1帧数据。

MA 发送时钟信号,在 MA 第一个上升沿,Slave锁存传感器状态。在 MA 第二个上升沿,编码器将 SL 信号拉低,用于应答 Master 的通信请求。

BiSS规定每个通信帧发起时都要检测一次 line-delay,并加以修正。从而确保 BiSS 通信波特率可以达到 10Mbit/s。在 line-delay 期间,MA 持续输出脉冲。

当 SL 信号从常高拉低后维持一段时间。这段时间叫ACK,表示 Slave 响应了 MA 信号,正在进行数据准备。通常 ACK 维持 0.1us 到 8us之间,这与 Slave 数据是否准备就绪有关,对于特定的 Slave,其 ACK 的长度是基本上是固定的。

当 SCD 发出完成后,SL 维持 0.5~40us 的低电平,这个时间段被称为 Timeout,对于特定的应用,Timeout 由 Slave 厂商规定。

1.3 请求循环步骤

- 空 闲时,主设备 保持MA高电平。光栅通过保持SLO高电平指示已准备就绪。

- 主设备通过开始传输MA上的时钟脉冲发出位置数据采集请求。

- 光栅通过设定MA上第二个上升沿的SLO低电平进行响应。

错误 警告 CRC(6位) 延时 - “Ack”周期完成后,光栅将数据传输至主设备,并且与时钟同步,如上图所示。

- 传输完所有数据后,主设备停止时钟并设定MA高电平。

- 如果光栅未准备好进行下一个请求循环,那么它将设定SLO低电平(延时周期)。

- 当光栅准备好进行下一个请求循环时,它将通过设定SLO高电平向主设备发送准备就绪信号。

1.4 状态转换

always@(*)begin

case(s_c)

IDLE:begin

if(sli)

s_n = WAIT;

else

s_n = s_c;

end

WAIT:begin

if(~sli && cnt_ma == 'd18)

s_n = BACK;

else

s_n = s_c;

end

BACK:begin

if(sli && cnt_ma == 'd18)

s_n = BCDS;

else

s_n = s_c;

end

BCDS:begin

if(~sli && cnt_ma == 'd18)

s_n = POST;

else

s_n = s_c;

end

POST:begin

if(cnt_ma == 'd19 && cnt_data == 'd31)

s_n = BWER;

else

s_n = s_c;

end

BWER:begin

if(cnt_ma == 'd19 && flag_wer == 'd2)

s_n = BCRC;

else

s_n = s_c;

end

BCRC:begin

if(cnt_ma == 'd19 && (flag_crc == 'd5))

s_n = BTIM;

else

s_n = s_c;

end

BTIM:begin

if(cnt_delay == 'd1562)//delay 31.25 us

s_n = IDLE;

else

s_n = s_c;

end

default: s_n =IDLE ;

endcase

end

通过将采集数据的状态组合起来循环获取编码器的位置信息:

reg [39:0] udata_r;

reg udata_vldr;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

udata_r <= 'd0;

end

else if(cnt_ma == 'd18 && (s_c == POST || s_c == BWER || s_c == BCRC))begin

udata_r <= {

udata_r[38:0], sl_h};

end

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

udata_vldr <= 'd0;

end

else if(cnt_ma == 'd18 && (flag_crc == 'd5) && (s_c == BCRC))begin

udata_vldr <= 1'b1;

end

end

1.5 CRC校验

包含位置、错误和警告数据的CRC多项式为:x^6 + x^1 + x^0。CRC的起始值为0x00。传输 时头为 MSB,且为倒置传输。起始位和“0”位 已 从CRC计算中省略。

//-----------------------------------------------------------------------------

// CRC module for data[33:0] , crc[5:0]=1+x^1+x^6;

//-----------------------------------------------------------------------------

module crc(

input [33:0] data_in,

input crc_en,

output [5:0] crc_out,

input rst,

input clk);

reg [5:0] lfsr_q,lfsr_c;

assign crc_out = lfsr_q;

always @(*) begin

lfsr_c[0] = lfsr_q[1] ^ lfsr_q[4] ^ data_in[0] ^ data_in[5] ^ data_in[6] ^ data_in[10] ^ data_in[12] ^ data_in[15] ^ data_in[16] ^ data_in[17]

^ data_in[18] ^ data_in[20] ^ data_in[24] ^ data_in

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?