NandGame以与非门为核心,从组件最基本的逻辑门开始,教玩家直观、简洁的一步步搭建出自己的计算机架构的网站。同时还可以组装自己的元件,可以说是体系结构、嵌入式、计组同学入门的福音。可以从原理层面上完全平替某些985的电子电路实验课(本人做学校的CPU架构设计实验太痛苦了,期末整合元件运行还有一堆bug,绝大部分同学都是应付了事,要是早知此网站何必当初!)

类似NandGame的还有steam上的《图灵完备》。

一、逻辑门元件

与非门

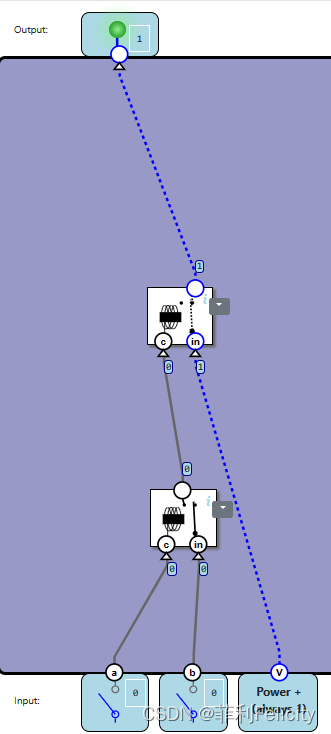

- 要求:通过两种继电器来创建一个与非门

- 解法:可以用逻辑表示两种继电器和与非门(&与 ~非)

relay(default on)(c, in)= ~c & in

relay(default off)(c, in)= c & in

nand(a, b) = ~(a & b) => ~(a & b) & 1 = relay(default on)(a & b, 1) => relay(default on)(relay(default off)(a, b), 1)

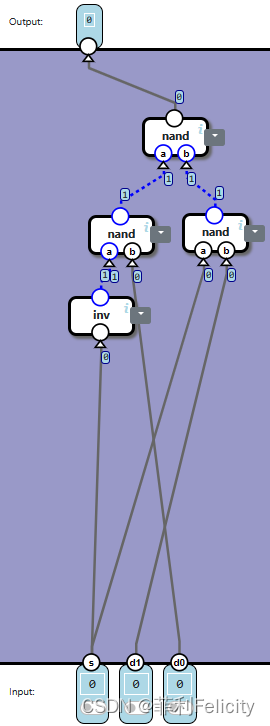

根据推导出的逻辑表达式得到下图:

非门

~x = nand(x, x),至少使用一个与非门,门延迟为1

与门

and(a, b) = ~nand(a,b),至少使用两个与非门,门延迟为2

或门

or(a, b) = nand(~a, ~b),至少使用三个与非门,门延迟为2

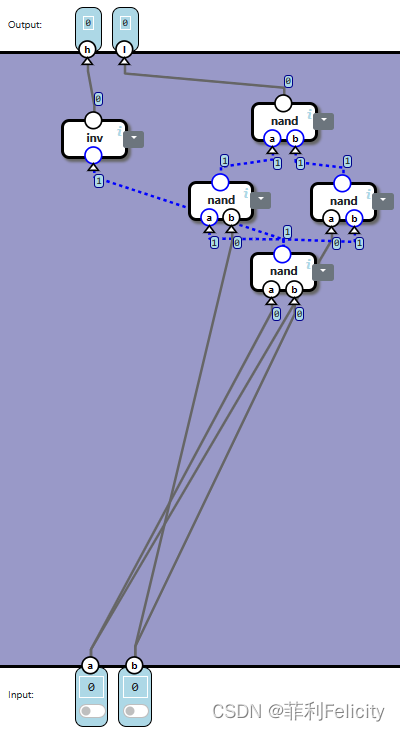

异或门

xor(a,b) = nand(nand(a, nand(a,b)), nand(b, nand(a,b)),注意到nand(a,b)可以被复用,因此一个或门至少使用四个与非门,门延迟为3

二、算术元件

半加器

将输入的两个比特相加,输出结果的低位l和高位h。

h = a & b

l = xor(a, b)

由上文可知, xor复用了一个nand(a, b),而a & b也包含nand(a, b)的部分,因此这两个可以合并复用,至少使用5个与非门,h门延迟为2,l门延迟为3。

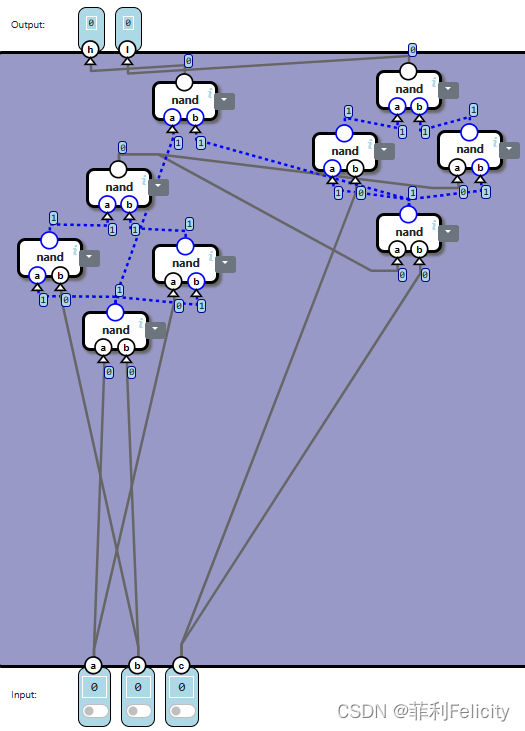

全加器

在半加器基础上引入了一个低一位的进位,本质上可以视为三个比特的相加。

h = or((xor(a, b))&c, a&b)

l = xor(xor(a, b), c)

至少使用9个与非门,h门延迟为2,l门延迟为6。

多位加法器(行波加法器)

用于实现多位数相加的一种方案,本质上是多个全加器串联组成的,执行顺序上是从低位到高位串行实现的。

自增

inc(X) = add(X, 1)

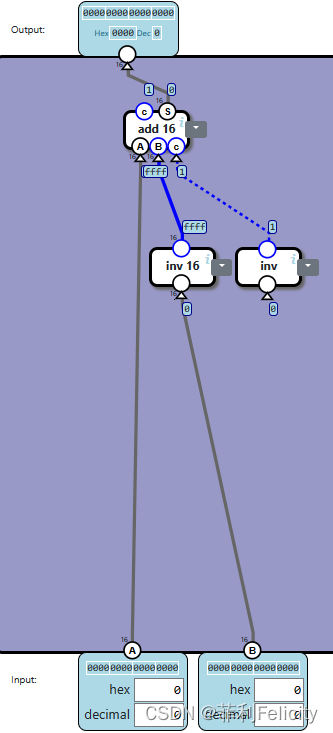

减法

实现多位数减法,A - B = A + 补码(B) = FA(A, ~B, 1),其中FA(a, b, c)是全加器,c为上一位的进位。

之所以不用inc(~B)实现补码,主要是充分利用全加器中的加法电路,并且减少串联逻辑门带来的延迟。

为0

判断一个n位数是否为0,将所有位用或运算符连接起来,最后取反即可。

需要注意逐位堆叠或门和二分堆叠或门使用的或门数量都是n-1个,但是二分堆叠的方式能减小延迟(逐位堆叠门延迟为n,二分堆叠门延迟为log(2, n) + 1)。

现实中不会用与非门来创建或门,通过二极管实现的或门和is_zero,可以认为没有延迟。

小于0

判断一个16位有符号数是否为负数,其实就是判断最高位(符号位)是否为1,题目中给出了一个splitter(分线器)用于将总线分成单比特的线。直接取最高位输出即可。

三、IO切换元件

2 to 1选择器(2 to 1 MUX/编码器)

根据s,选择两个输入(d0, d1)之一作为输出。

s = 0时,输出d0;s = 1时,输出d1。

MUX(s, d0, d1) = nand(nand(~s, d0), nand(s, d1))

至少使用四个与非门,门延迟为3。

扩展:2n to 1选择器的s是n位的,由1个2 to 1选择器和2个2n-1 to 1选择器组成,全部展开可知,一个2n to 1选择器需要共2n - 1个2 to 1选择器。以二叉树形式堆叠而成,如果按照上图的构造方式,一个2n to 1选择器的门延迟为3n。

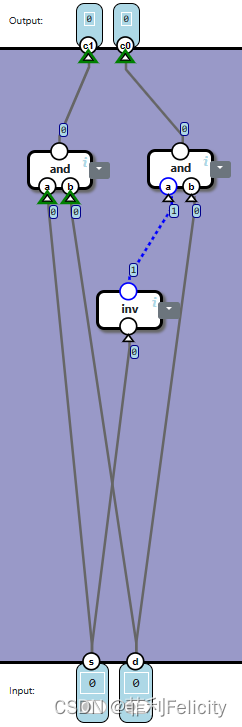

开关(1 to 2译码器)

根据s选择d从哪个口输出。

若s选择0,c0输出d;

若s选择1,c1输出d。

c1 = s & d

c0 = ~s & d

提交答案时提示,下图并非最少与非门的解(恳请大佬指教):

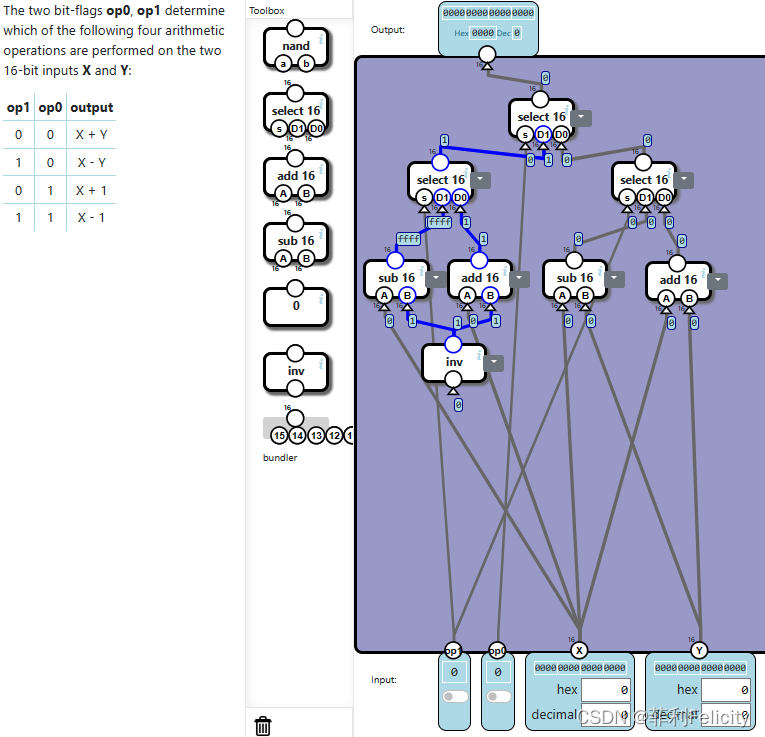

四、ALU

算术单元/逻辑单元

这两关本质上是相同的,都是将两个操作数在各种计算元件计算出结果,然后选择器根据输入的运算指令op(指令和运算的对应关系是人为定义的)输出相应计算元件的计算结果。这两个关卡分别都有四种计算元件,因此使用上文提到的2n to 1选择器的构建思路构建了4 to 1选择器。以下是逻辑单元的示例(算术单元基本相同)。

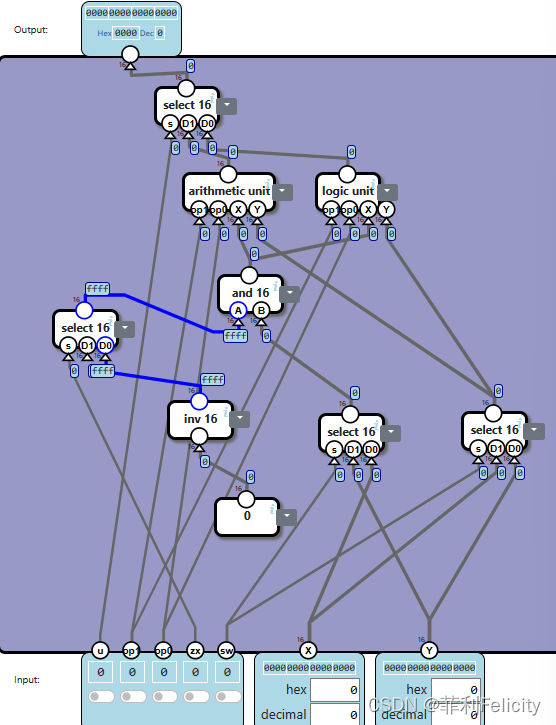

ALU

ALU是上述两个单元的整合,输入多了指令位u(一共8种指令,自然需要三位指令位),两个标志位zx(将左操作数置零)和sw(交换X和Y操作数)。

对于运算的合并,无非就是将指令位u、逻辑单元和算术单元的计算结果作为2 to 1选择器的输入。从整体来看,就是一个8种运算需要通过8 to 1选择器实现选择输出的过程。

重点在于标志位zx和sw的实现:

- 右操作数在sw为0时,是y;sw为1时,是x。自然想到可以用2 to 1选择器实现。

右操作数=select(sw, x, y) - 左操作数在sw为0时,是x;sw为1时,是y。自然想到可以用2 to 1选择器实现。然后处理zx逻辑:如果zx为1,则左操作数置零,否则保持原值,同样可以用2 to 1选择器实现。

左操作数=select(zw, 0, 0xffff) * select(sw, y, x)

该方案并未做到门最少化。

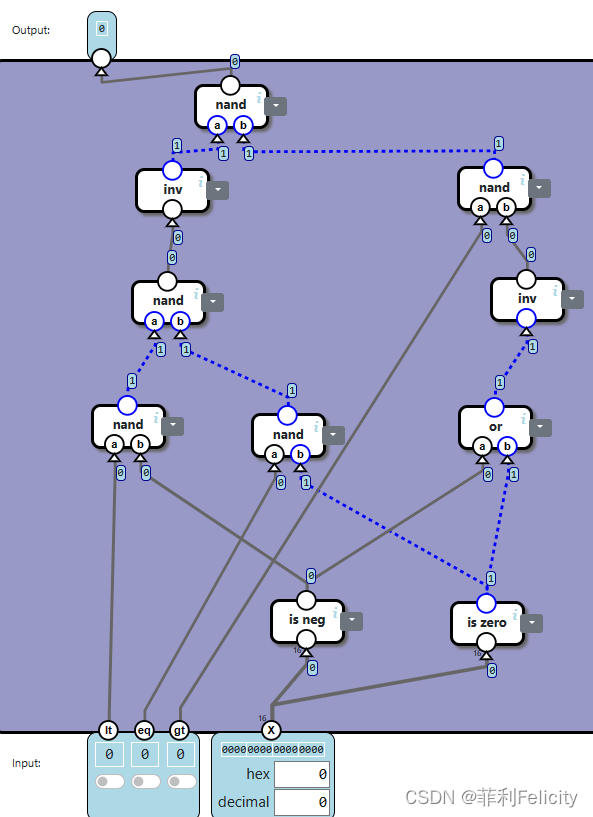

条件(分支逻辑)

使用is_neg和is_zero来实现gt(greater than) lt(less than) eq(equal to)三种分支逻辑。这些逻辑不难实现,关键在于如何简化到更少的与非门使用。

通过合并两个非门,得到最少与非门使用方案如下:

nand(~nand(nand(lt, -X), nand(eq, is_zero(X))), nand(gt, ~or(is_neg(X), is_zero(X))))),其中is_neg(X)和is_zero(X)被复用两次。

根据上文"为0"一节的分析,一个16位的is_zero需要15个或门和一个非门,共计46个与非门,最小门延迟为log(2, 16) + 1 = 5。需要注意的是,现实中或门基本不使用与非门实现,

因此对于该分支逻辑实现方案,共需56个与非门,门延迟为9。依然强调,二极管实现的或门和is_zero,可以认为没有延迟,这种情况下,门延迟为4。

总结

至此完成了NandGame的组合电路关卡。其中出现了CPU结构中的控制器所需组件:ALU、多路选择器、分支逻辑等。还出现了程序计数器(PC)所需的自增组件。

但要让各组件同步运行,并且能够实现存取数据和程序指令、按次序的推动整个通路的运行,离不开时序产生器(时钟)以及时序电路。

NandGame是一个通过直观教学帮助用户从逻辑门开始搭建计算机架构的网站,包括逻辑门、算术元件、选择器和分支逻辑等,对电子工程特别是体系结构和嵌入式领域的学生具有实用性,如替代传统实验课程中的CPU设计。

NandGame是一个通过直观教学帮助用户从逻辑门开始搭建计算机架构的网站,包括逻辑门、算术元件、选择器和分支逻辑等,对电子工程特别是体系结构和嵌入式领域的学生具有实用性,如替代传统实验课程中的CPU设计。

1411

1411

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?