1.前言

其实在此之前我是学习verilog语言的,本以为以后工作都只会遇到或者用到verilog,但怎么也没有想到会遇到vhdl这个硬茬子,而且还是整个工程。

刚拿到工程,本以为只是单纯verilog,没想到一打开工程文件,这不妥妥的vhdl吗?乍一看,工程目录下的年份居然是2014年,好家伙八年前的东西,而且所有目录下的年份基本没有改变,是有多久没更新了,这不玩我吗?但这是交给我的任务,干不了只能卷铺盖走人了,没办法只能硬着头皮干。

起初我就在想现在开发平台都那么完善了,并且vhdl和verilog都是硬件描述语言,应该相差不会很大,所以就在想有没有什么平台或者软件直接将两者语言互换,结果我一搜还真有一款叫做 X-HDL的软件,可以随意互换两者语言。好了,现在有了这款软件就没有必要再讲这篇文章了,再见!

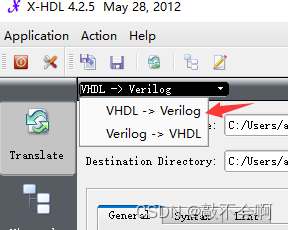

等等,当我怀着无比激动的心情下载了这款名叫X-HDL的软件,就长下面这样色儿的

心想不愧是网络时代啊,要啥有啥!然后就按照安装步骤将它安装好,点击打开,咦?怎么没有反应,是我安装错了?没有吧!然后等待了差不多一分钟左右,居然可以用!进到软件里面后突然眼前一亮,哇!感觉像是打开了新世界的大门,激动的心颤抖的手,话不多说,直接开整!我按照步骤把vhdl工程代码所在路径添加了进去,然后选择翻译后生成verilog语言的保存路径,之后又点击左上角语言互换。

好家伙,功能这么强大,心想这不捡到宝了吗?以后不得起飞?想怎么变就怎么变?正当我开心之余,点击Translate,念上咒语“如玉如玉,按我心意,快快显灵!”耶?翻译失败?怎么能够?我是按照步骤来的呀?不行,肯定是我哪个步骤错了,是不是翻译源文件和保存文件路径有中文啥的?我又重新起了一个文件,再翻译!耶?还是失败!这么玩的吗?后来我试很多次,多种方法,说啥vhdl代码里面注释不能有中文、按照步骤来不会出错等等,还是不得行。然后我看了各个介绍这款软件的博客里面的评论,我嘞个去!不看不知道,一看吓一跳呀!这都啥呀?评论区全是翻译失败的。给大家伙看看

为什么?为什么要给我刚刚燃起的希望浇灭了呀?后来我还是不相信,我命由我不由天!又试着安装重启等等一系列操作,最终结果都是翻译失败。失败得很彻底,直到我发现软件工具栏上面的版本日期2012年5月28,什么?!这玩意儿比我这个工程代码年份还要久远,也是没有更新过,那不奇怪了。现在电脑基本都是windows10了,版本不兼容也是常态,即使下载也不一定能用。我就好奇了,这么好的东西怎么就荒废了呢?可惜了可惜了,如果是跟着代码发展步伐一起更新到现在还能用,是多少像我这样多一事不如少一事的人的福音呀!

2.学习vhdl

经历了翻译失败的挫折,直到现在都还没走出来的我,终于硬着头皮到处找怎样把vhdl翻译成verilog,除了一大堆介绍这个x-hdl软件的,其他的都是寥寥无几。

走投无路只能开始接触vhdl了,靠人不如靠己,撸起袖子干,自学vhdl!于是当我打开哔哩哔哩想像当年学习verilog一样跟着视频学习,结果。。。。不是吧,连视频都没有几个,怎么搞?难度加大了呀!找来找去找到了窦衡教授讲解的考研课程(EDA技术),前面几个课程是讲解EDA技术,后面都是vhdl,而且语法内容讲得都很细,虽然视频有点年代感了。有兴趣的同学可以去学习学习。

跟着推荐我又找到几本对于学习vhdl的相关书籍《VHDL数字电路设计教程》、《VHDL实用教程 潘松》、《[VHDL入门.解惑.经典实例.经验总结].黄任》、《 VHDL与数字电路设计 卢毅 赖杰》,这些都是对于vhdl介绍比较全面的书籍,而且非常难找,有需要的同学可以在下面的下载链接里下载

链接:https://pan.baidu.com/s/1EAdVCg-ZLk_bEg07ut7xKw?pwd=vhdl

提取码:vhdl

当时正准备着手学习vhdl,想着在公司里学又太浪费上班时间,下班回去学嘛,累一天回去都没啥精神只想躺尸。但是好巧不巧三月底碰上了疫情,被封在家里整整两个月时间,正好利用了这段时间自学了vhdl,由于大部分资源都是文字上的,很少有实操,所以学习起来很吃力,两个月的结果也只是皮毛上的东西。

正常上班后由于浪费了之前两个月的时间,要开始赶进度了,于是我就着手开始翻译,把vhdl工程转为verilog,很多人看到这里很不能理解,为什么自己都学习了vhdl,干脆直接用vhdl源代码去维护源工程就行了,干嘛还得大费周章去转换它?我也有想过这样拿来直接用,但是考虑到两种情况,不得不迫使我去转换它。第一个就是现目前vhdl资源太少,基本被verilog取代了,况且verilog使用的人多了资源也就多,需要改动或者加功能网上一搜就是一大堆,而vhdl要改动的话相对于来说很困难。第二个就是考虑到以后可能不止我一个人会用到这个工程,万一他不熟悉vhdl的话又要和我一样重蹈覆辙了。

3.着手转换

注:着手转换的前提是要会一点vhdl基础哦

vhdl相对于verilog来说比较严谨,所以vhdl在国内的使用方面偏向于军工研发方面,而一般的研发公司都普遍使用verilog,不仅因为verilog语言使用起来方便、不拘束,而且还利于维护。

vhdl和verilog编译调试后的工程都是大同小异。并且现在modelsim软件可以让vhdl和verilog混合仿真,仿真结果都一样,所以能直接手撕代码的大佬可以直接看vhdl的仿真结果来写verilog代码,而看代码转换代码的方式只适合我这种小菜鸡,但可能后期编译报错会很多,所以还得再参考vhdl的仿真结果来修改。

拿到工程,直接用ise打开(因为我这个芯片型号是赛灵思sprantan6系列的,所以用ise集成开发环境),找到顶层文件top.vhd后点击文件下面工具栏里的【Synthesize - XST】里的创建RTL视图【View RTL Schematic】生成RTL视图,然后根据top.vhd顶层文件里的元件声明和RTL视图里面的各个端口结合起来定义verilog代码的端口。为什么要两个一起参考呢,因为vhdl中元件端口例化需要先声明在例化。而verilog相对灵活不需要这么严谨,所以结合二者方便verilog顶层文件的例化,而参考RTL视图来例化模块更好的确保不会漏掉任何一个端口。

在转换过程中理解最重要,其次就是各种语法等的用法。咱们就跟着代码步骤来,逐一转换。

顶层模块转换问题

先看vhdl顶层代码

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

library UNISIM;

use UNISIM.VComponents.all;

entity FPGA_TOP is

port(

OSC_CLK : in std_logic;

FPGA_RST : in std_logic;

CMOS_PCLK_X : in std_logic;

CMOS_HREF_X : in std_logic;

CMOS_VSYNC_X : in std_logic;

CMOS_D_X : in std_logic_vector( 7 downto 0);

CMOS_XCLK_X : out std_logic;

CMOS_FSIN_X : out std_logic;

CMOS_PWDN_X : out std_logic; 前面的库调用可以不用管,verilog中不需要调用库,直接定义端口,这里看到下面端口定义有区别,是因为我结合RTL视图把缺少的端口补充上去了,vhdl中也有定义,只不过是另起了一个人定义模块,verilog中则不需要这么复杂,咱们直接看着端口,直接定义,具体是wire型还是reg型也可参考RTL视图定义。

module fpga_top (

input wire osc_clk ,

input wire fpga_rst ,

input wire coms_pclk_x ,

input wire coms_pclk_y ,

output wire camera_pclk ,

output wire coms_xclk ,

output wire pclk_x ,

output wire pclk_y ,

output wire sys_clk ,

output wire sys_rst ,

signal信号定义

1.外部信号

外部信号有in out inout buffer四种类型。在entity(实体)中定义。Buffer是可反馈的输出端口。

2.内部信号

1.内部信号可在结构体,包体,块语句中定义

2.内部信号定义格式

Signal 变量名称 :数据类型 := 初值;

Signal 变量名称 :数据类型;

Signal 变量名称 :数据类型 范围;

signal s_sys_clk : std_logic ;

signal s_cammera_pclk : std_logic ;

signal s_cmos_xclk : std_logic ;

signal s_sys_rst : std_logic ;

signal s_pclk_x : std_logic ;

signal s_pclk_y : std_logic ;

signal s_cpu_cammera_d : std_logic_vector( 7 downto 0);这里直接转换定义为寄存型

reg s_sys_clk ;

reg s_camera_pclk ;

reg s_coms_xclk ;

reg s_sys_rst ;

reg s_pclk_x ;

reg s_pclk_y ;

reg [7:0] s_cpu_camera_d ; 例化模块直接例化

OSC_CLK => OSC_CLK ,

FPGA_RST => FPGA_RST ,

SYS_CLK => s_sys_clk , .osc_clk (osc_clk ),

.fpga_rst (fpga_rst ),

.sys_clk (s_sys_clk ),为了后期好理解,所以这里把vhdl中的大写全部转换为小写(vhdl中不分大小写)。

例化模块后面可能会遇到少部分赋值语句,例如我遇到的这种情况

M1_INT <= s_m1_int;

M2_INT <= s_m2_int;

M3_INT <= s_m3_int;

M4_INT <= s_m4_int;“<=”赋值符号在这里用法类似于verilog里的assign,所以直接转换

assign m1_int = s_m1_int;

assign m2_int = s_m2_int;

assign m3_int = s_m3_int;

assign m4_int = s_m4_int;顶层文件转换到这里就转换完成了,较目前来说遇到的问题不是很多,如果有遇到语法上或者赋值啥的其他问题的话,欢迎在评论区交流,咱们一起探讨。后面逐一转换中出现的问题将会在之后的文章慢慢讲解。

371

371

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?