环境:Vivado 17.4

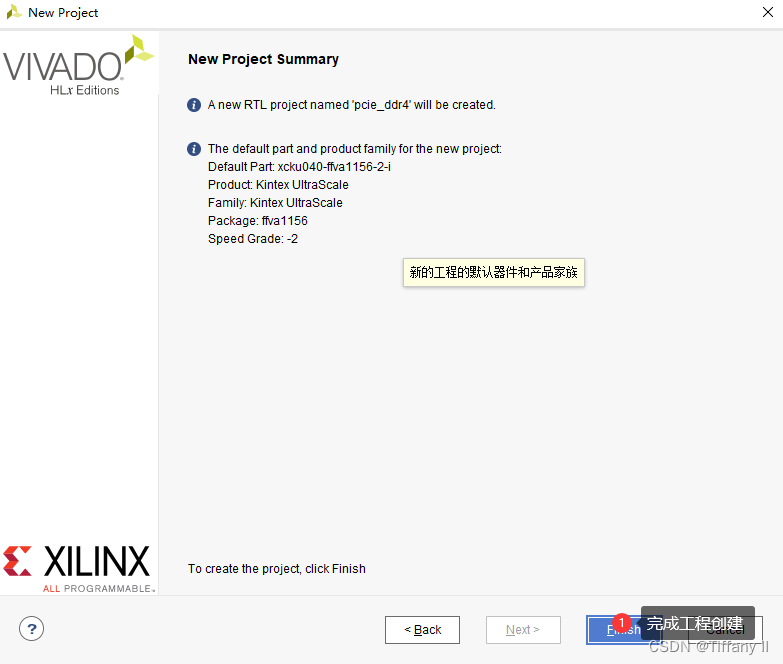

一、创建工程文件夹pcie_ddr4

根据个人所需选择器件库,创建好空的工程文件夹。

二、创建IP工程

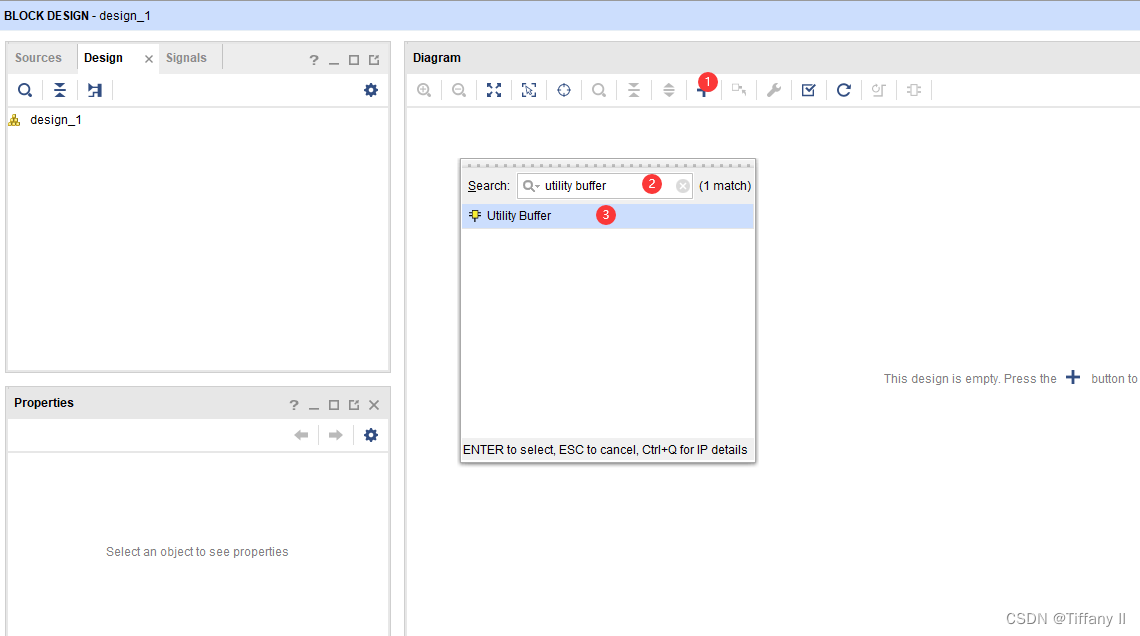

1、新建design

2、添加IP模块

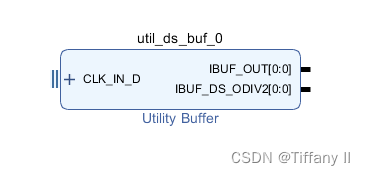

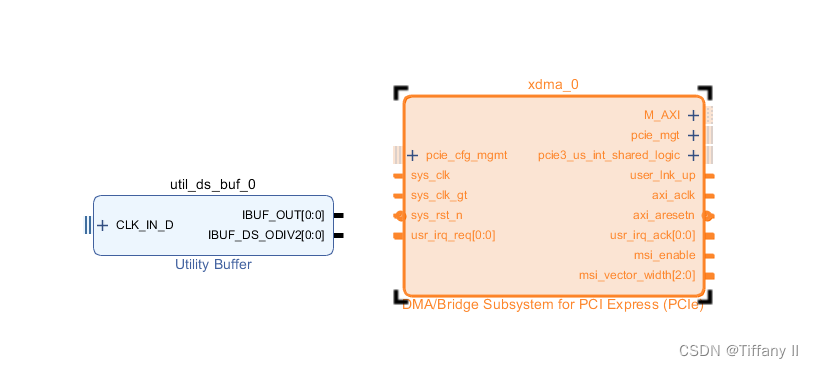

添加第一个IP:utility buffer

双击模块进入配置,选择差分时钟;

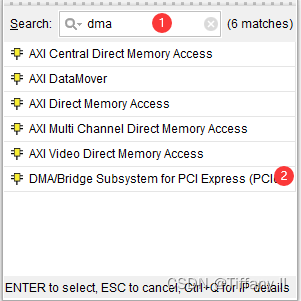

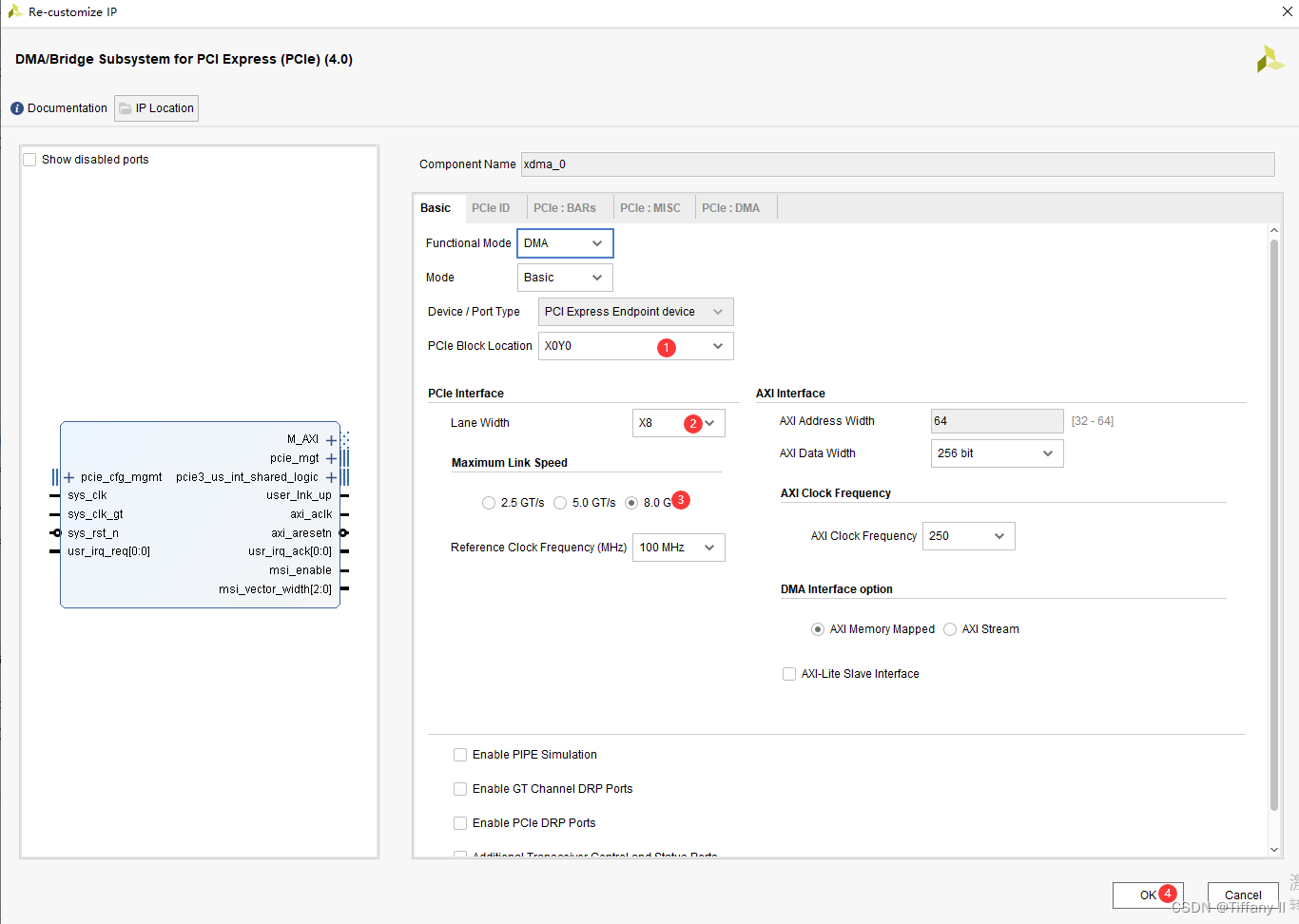

第二个IP,直接搜索DMA ,双击添加;

添加之后同样双击模块,进入配置:

配置完成。

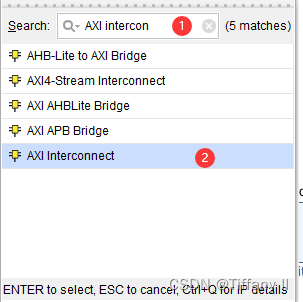

第三个IP:AXI Interconnect,双击模块进入配置,将主从接口都设置为1。

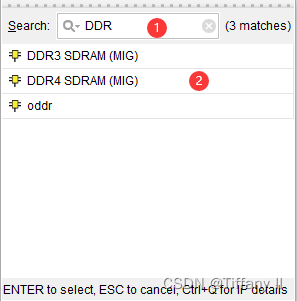

第四个IP:同样添加DDR4,这里默认设置就好。

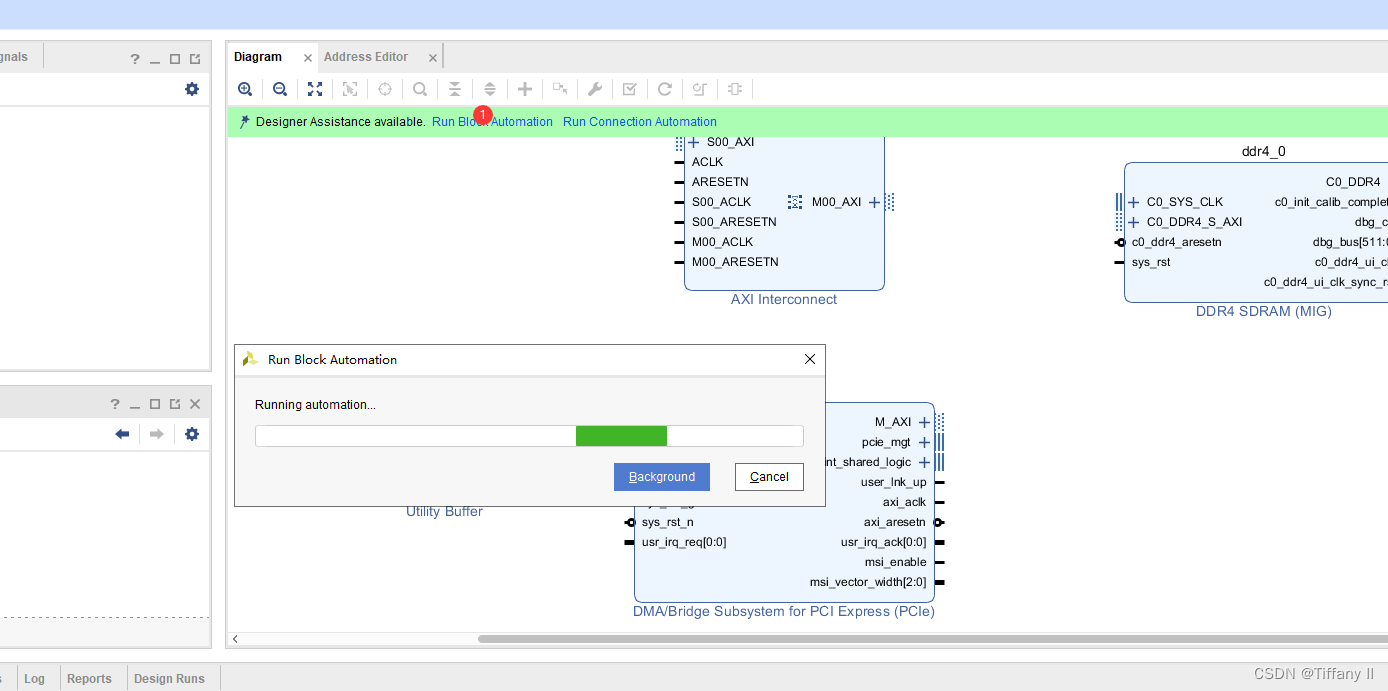

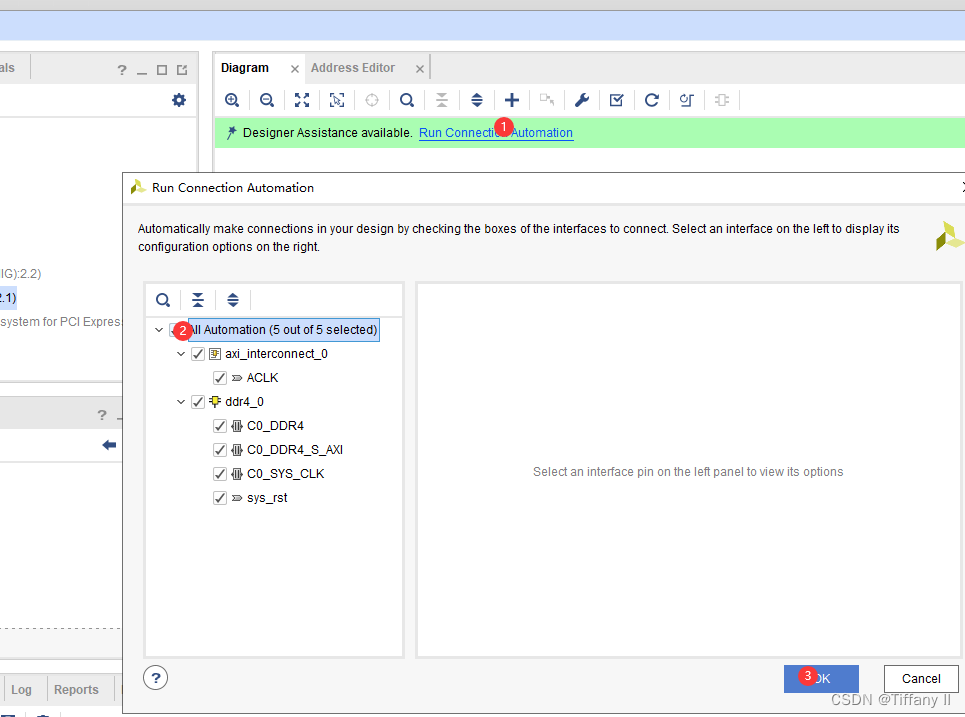

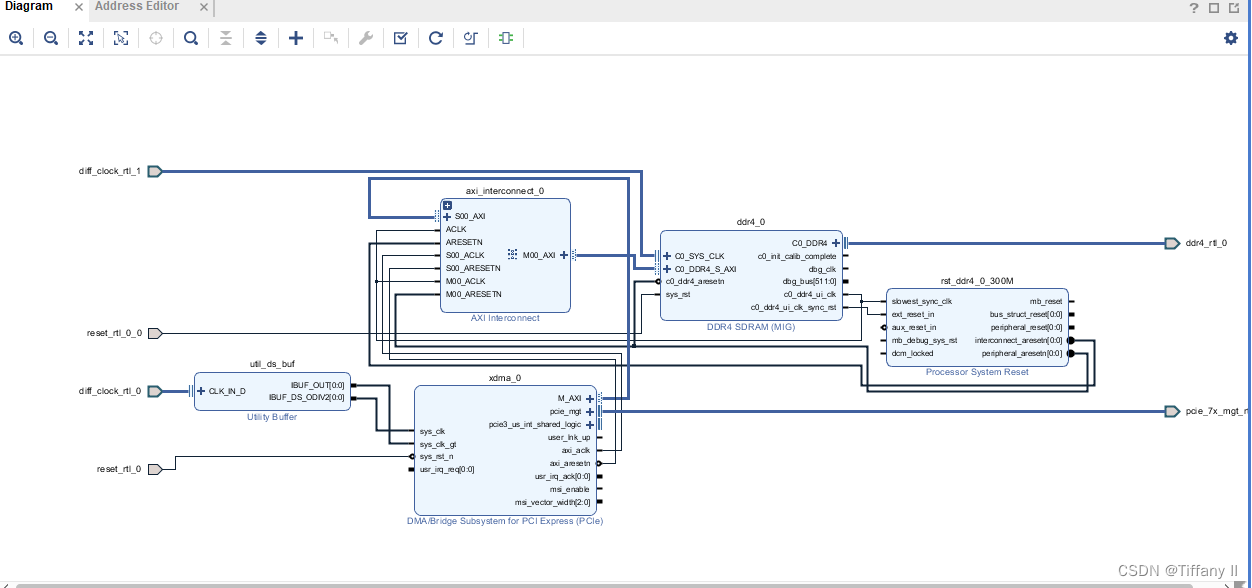

接下来进行连线:

自动连线完成后,按F6进行检查。没有错误之后进行下一步。

三、模块设计完成

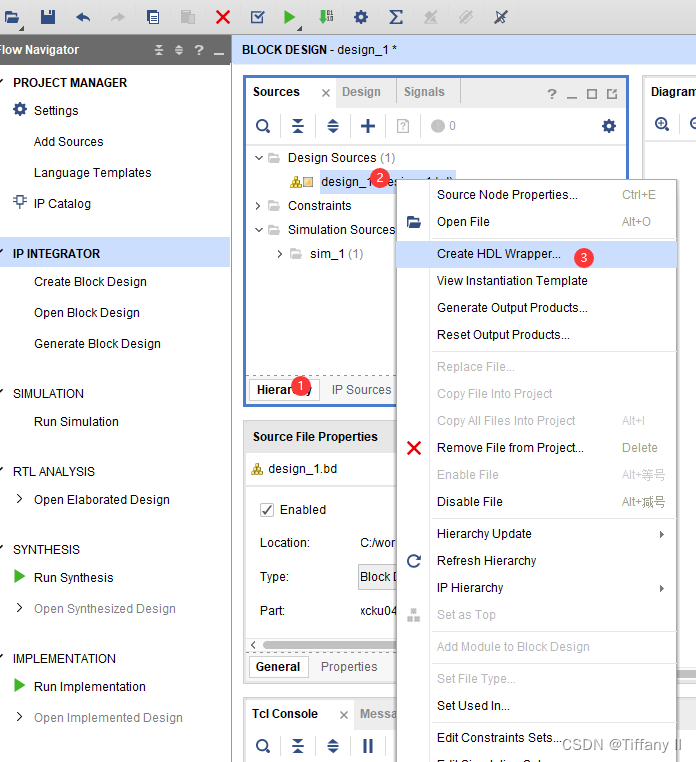

生成可编译的HDL。

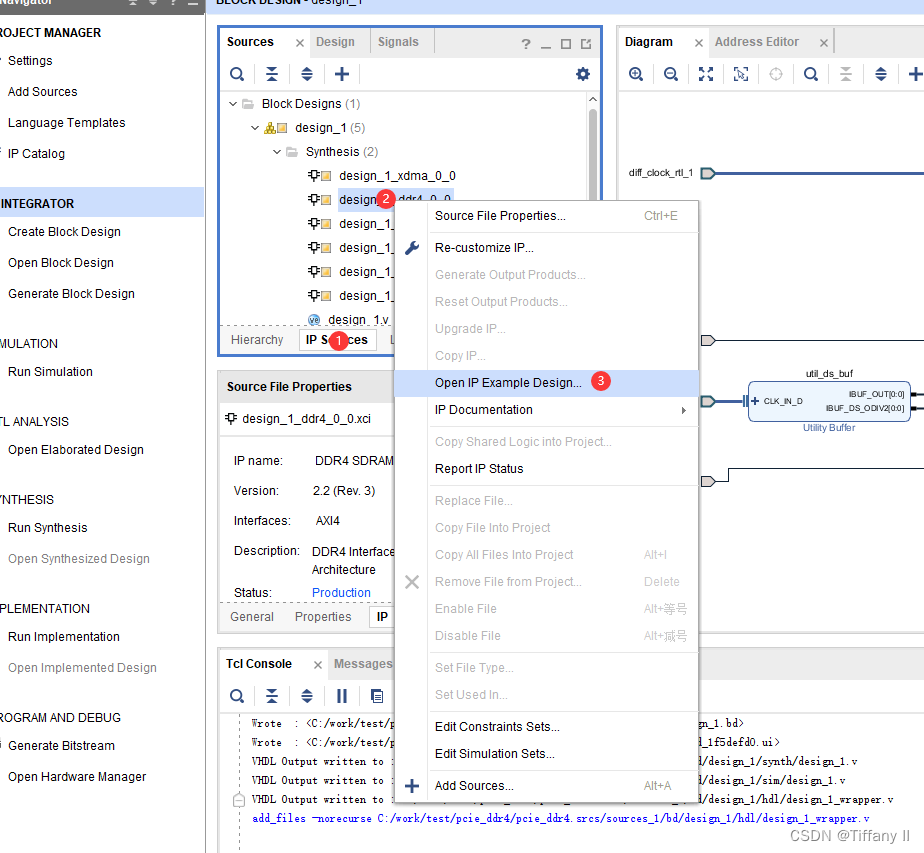

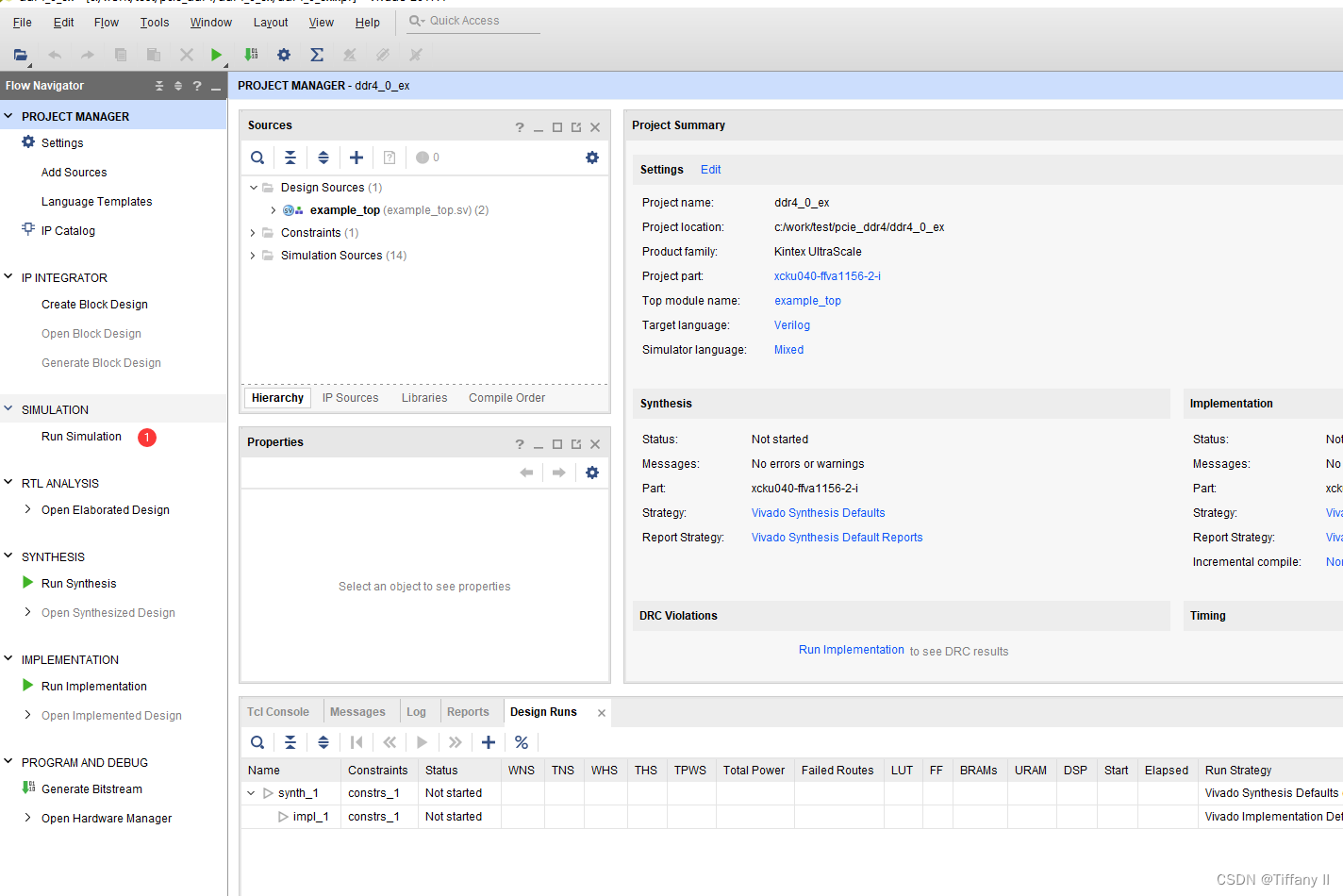

Create HDL Wrapper之后;进入design_ddr4中验证IP功能:生成的文件选择工程文件夹目录下。

之后会进入一个新的窗口:点击仿真。

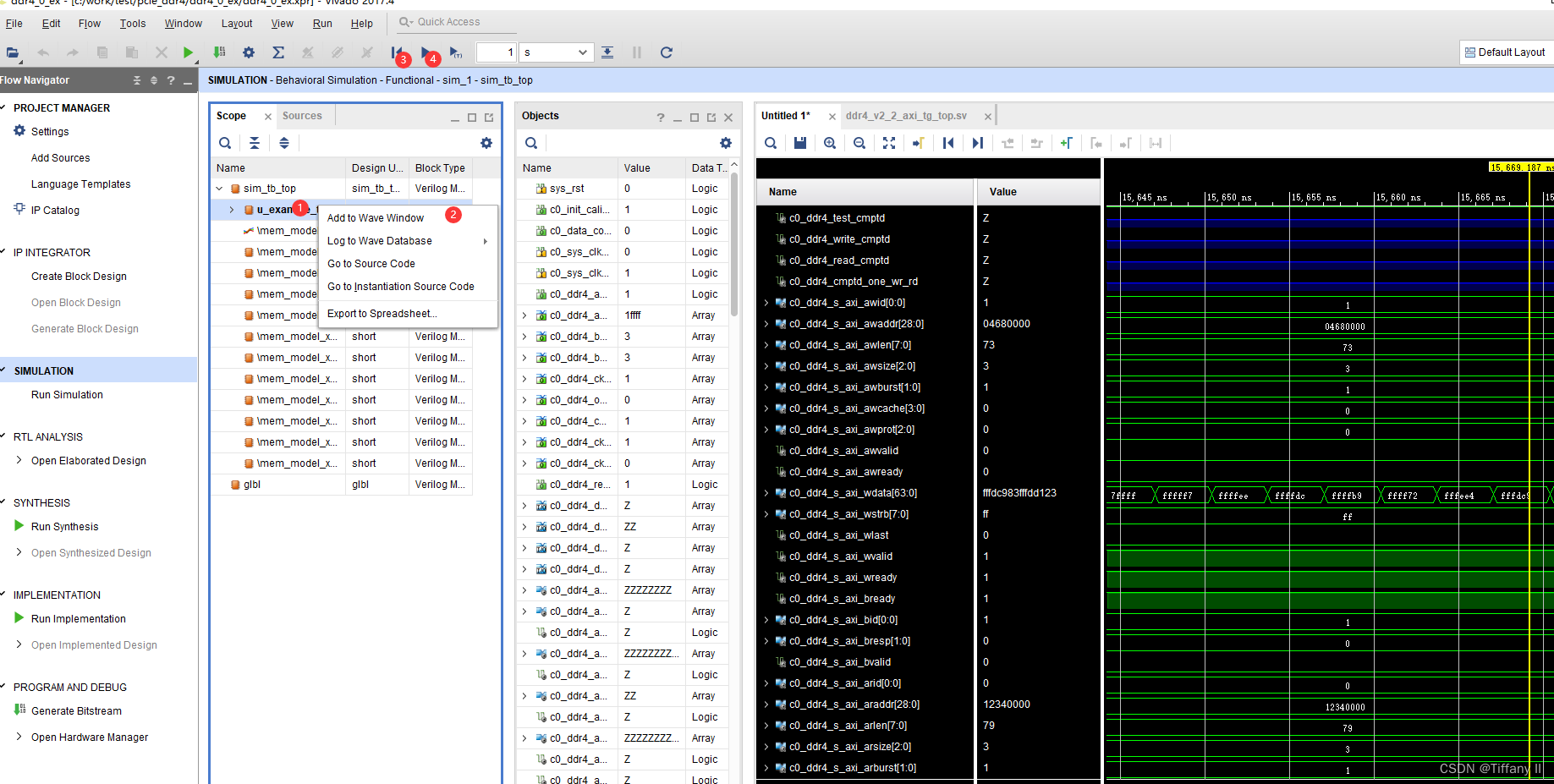

四、仿真

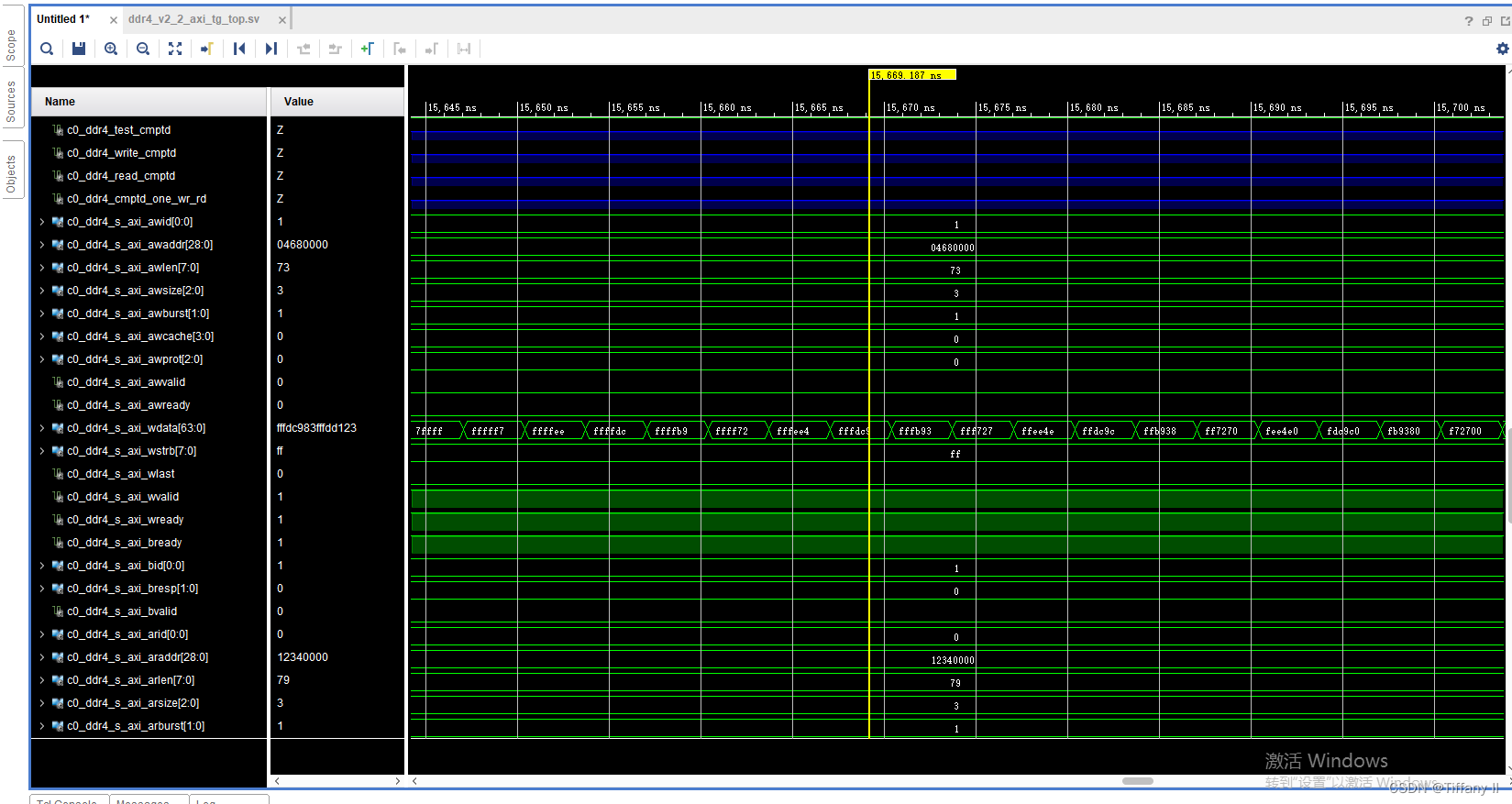

添加波形,自定义仿真时间,重置之后得到波形:

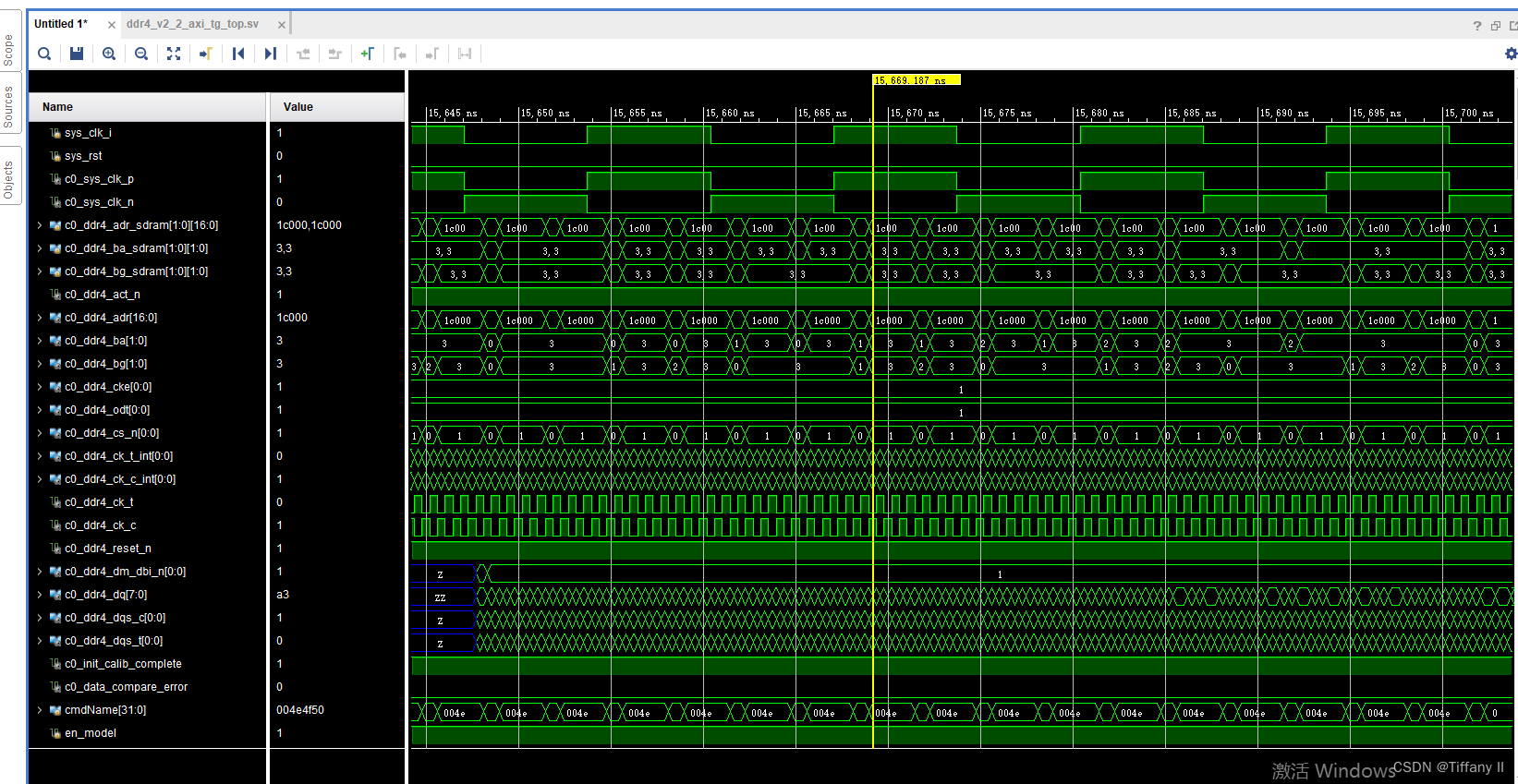

对通过PCIe数据传输的DDR4存储器仿真结果:

对通过PCIe数据传输的DDR4存储器仿真结果:

在不同地址成功写入用户数据,具体见波形。

速率待测。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?