一些小项目:

基本UART;

基于IIC通信的EEPROM读写控制;

基于SPI通信的M25P16 FLASH读写控制;

基于单总线的温度预警(DS18B20);

SDRAM读写控制;

摄像头ov5640的实现。

1.串口通信协议的优缺点

单总线(优点:线路简单,硬件开销少,成本低,便于总线扩展和维护)

1.同步还是异步 看数据传输有无时钟,同步有,异步无

2.全双工还是半双工 看数据总线,,,发送和接收的总线数

3.传输速度:SPI_几十Mbps,i2c_3.4Mbps,UART_2Mbps,单总线_最慢

2.UART

通用异步收发器,全双工,异步通信

空闲位高“1”

起始位0:1位 + 数据位:8位(5.6.7.8.9) + 奇偶校验位(0) :1位 + 停止位:1位 共11位

波特率:每秒传输二进制码的位数。115200下传输1bit需要434次计数(晶振),9600下传输1bit需要5208次

接收端代码实现:通过比特率、波特率计数器来确定数据传输的速率;延时一个时间周期来接收数据,设置接收开始的标志信号判断什么时候数据接收,将数据串并转换实现数据传输。

发送端代码实现:通过比特率、波特率计数器来确定数据传输的速率;设置发送开始的标志信号判断什么时候开始发送,并转串发送数据,设置busy信号防止数据错误。

奇偶校验:偶校验:数据中有奇数个1,校验位就是1;有偶数个1,校验位就是0.

3.基于IIC通信的EEPROM读写控制

Inter-Interated Cireuit 集成电路总线,同步通信,半双工

协议层面是怎么开始收发数据的:

在SCL为高电平期间,SDA由高到低跳变。 在SCL低电平期间传输数据,高电平进行数据采样,一个SCL脉冲传输一位。完成数据位之后,就在脉冲9的时候由接收端反馈应答信号,0表示应答,1表示非应答。

IIC怎么判断有无应答或者怎么停止收发数据:

时钟高电平时,拉高SDA,下一个时钟脉冲期间,若数据总线SDA被拉低,SDA=0,则应答,继续传输数据;若数据总线SDA保持不变,则发停止位,停止传输数据。

设计代码:

250分频的系统时钟,保证占空比为50%,设计4位操作符,三段式的状态机(IDLE-START-WRITE(READ)-RACK(SACK)-STOP),作以时钟总线和数据总线的约束,防止亚稳态,将输入输出的数据寄存,再设计总线输出数据使能控制IIC是否进行通信。

EEPROM读写数据帧:

写:起始位、写控制字节+写地址+数据+停止位

读:起始位、写控制字节+读地址+起始位、读控制字节+数据+停止位

EEPROM读写控制代码:

Electrically Erasable Programmable Read-Only Memmory 电可擦可编程只读存储器

特点:掉电后存储的数据不丢失

将输入输出的数据暂存到读、写fifo中,三段式状态机(IDLE-WR_REQ(RD_REQ)-WAIT_WR(WAIT_RD)-DONE),判断字节,读和写的字节是不同的,根据读、写过程确定输出,设计TASK封装一位请求、四位命令和8位数据,根据状态机跳转条件约束读地址和写地址。

4.基于SPI协议的M25P16 FLASH芯片单字节读写

Serial Peripheral Interface

串行外设接口:全双工,同步通信,一主多从,四种模式,出厂即设定不允许修改。

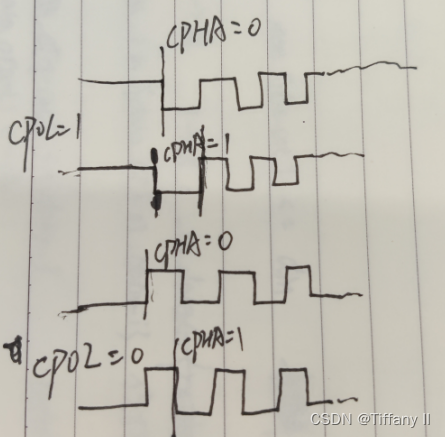

mode 0 :CPOL=0,CPHA=0;SCL处于低电平,数据采样在第一个边沿,上升沿采样,下降沿发送;

mode 1 : CPOL=0,CPHA=1;SCL处于低电平,数据发送在第一个边沿,下降沿采样,上升沿发送;

mode 2:CPOL=1,CPHA=0;SCL处于高电平,数据采集在第一个边沿,下降沿采集,上升沿发送;

mode 3:CPOL=1,CPHA=1;SCL处于高电平,数据发送在第一个边沿,上升沿采集,下降沿发送。

协议层面是怎么开始收发数据的\收发数据的过程:

SPI主机和从机都有一个串行移位寄存器,SPI只有主从模式,外设的写操作和操作同步进行,写一个数据就会接收到一个数据。以MSB的形式传输。

1.拉低对应Slave的信号线,表示与该设备通信;

2.主机通过发送SCLK时钟信号(根据工作模式确定高低电平有效)来告诉从机接收或者发送;

3.主机将要发送的数据写到数据缓存区Memory,缓存区经过移位寄存器,通过MOSI信号线将字节一位一位的传送给从机;同时从机MISO接口接收到的数据经过移位寄存器一位一位的移到接收缓存区;

4.从机也将自己串行移位寄存器中的内容通过MISO信号返回给主机;同时MOSI信号线接受主机发送的数据,这样,两个移位寄存器中的内容就被交换。

代码设计:

状态机(IDLE-READY-TRANS),将需要传输的数据寄存到串行移位寄存器,通过请求信号来控制进入准备传输的状态,向MISO或MOSI中非阻塞赋值数据字节。

FLASH读、写过程:

设计选择器来控制字节的长度,复用:在传输过程中计数。

读:七状态状态机:IDLE-读ID命令-读ID-读数据命令-读地址-读数据-读完成,设计选择器来判断当前操作下的字节长度,命令、数据一个字节,ID、地址三个字节,设置寄存器的最大读1000次,延时为5ms,读过程中,将各个字节寄存到输出寄存器中,串转并之后统一输出。

写:主五状态读写命令状态机:IDLE-写使能命令-擦除指令-读状态寄存器指令-页编程指令,从操作状态机:IDLE-发送命令-发送地址-数据-延时,设计过程中,写使能、擦除、发读状态寄存器指令、页编程第一次传输一定是命令,发完写使能命令之后延时等待;发完擦除命令,先发完地址,等待延时再发数据,发完PP命令后,发完地址之后接收数据,数据传输完要等待延时,设计选择器控制输出字节的长度,设计标识符flag标志不同阶段,再把数据和地址寄存,其中设计了传输请求标志,在从机发送操作命令时有效,提醒主机准备发送数据。

5.SDRAM

同步动态随机存储器,空间存储量大、读写速度快、价格相对便宜;由于SDRAM内部利用电容存储数据,为保证数据不丢失,需要持续对各存储电容进行刷新操作。

初始化-自动刷新-读-写

页突发读写过程:

发送激活指令,行激活(同时在bank总线输出想要写入数据的bank地址,在地址总线输出写入数据的行地址);发送激活指令后需要等待一定时间,在此期间需要发送空指令;等待结束后发送写\读指令,在bank总线输出想要写入数据的bank地址,在地址总线输出要读取\写入数据的列首地址,列读写(在数据总线输出要写入SDRAM的第一个数据),每个周期都输入空指令,数据总线一直输出想要输出的数据,所有数据传输完之后的下一个时钟周期输出突发终止指令,结束这次突发;发送预充电指令是对所有bank进行预充电,A10拉高即选中所有bank,此期间同样要发送空指令。

为什么要引入FIFO模块?

首先fifo能解决多bit数据跨时钟域同步的问题,其次,在存在SDRAM操作冲突时可以将数据寄存到fifo以防止数据被覆盖或者丢失;通过引入SDRAM的操作实际上变成对fifo的操作,而fifo的控制时序又相对简单,能大大简化操作。

SDRAM的代码设计思路:

用户将写入SDRAM的数据寄存到写fifo的写端中,待SDRAM响应写请求之后,从写fifo中读取数据作为数据源写入SDRAM;用户发起读请求,待SDRAM响应读请求,从SDRAM中读取的数据被写入读fifo,用户侧通过avalon的master映射接口,将读fifo的数据读出。所以需要例化2个双端口异步fifo模块,分别作为读模块与写模块;读、写响应信号均为异步信号,需要打拍采取下降沿;不仅如此,设置读写优先级仲裁和操作标志来约束什么时候读、写。

仲裁机制:每当写fifo模块中的用户数据量大于突发长度时,就先进行SDRAM写入操作;每当读fifo模块中数据量小于突发长度时,就进行SDRAM读取操作;

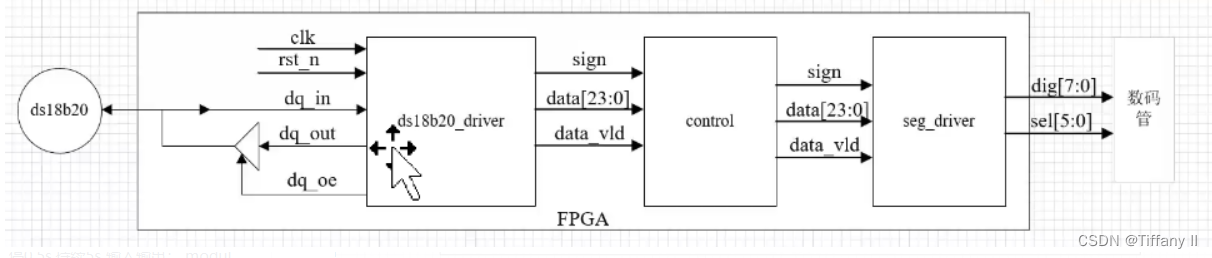

6.基于单总线的温度预警(DS18B20)

1-wire ==> DQ,半双工,异步通信

CRC校验

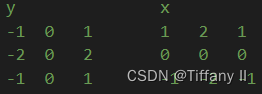

传感器里面的负值怎么处理:补码,取反加1可得到二进制,乘以精度就得到实际温度

7.ov5640

原理过程:摄像头采集图像,对图像一帧一帧的进行处理,1280x720的分辨率;一帧图片的第一个像素点作为包头,最后一个像素点作为包尾,将图片转换成RGB的数据,灰度化图片,将RGB像素点二值化,再通过sobel流水线算子消除梯度方向上的影响(边缘检测),通过FIFO接收并作缓存数据,在FPGA中通过IIC接口配置ov5640寄存器;调用PLLIP核生成时钟,设计的行同步(40)和场同步(5)脉冲,将经算子的转换灰度数据从SDRAM调出,转换为RGB格式,输出到显示屏。

高斯滤波:原图像上的某些噪声点在经过周围像素点加权求和后会被剔除掉;

sobel:用于边缘检测,通过卷积操作,四级流水线设计,一级缓存3列,二级求和,三级计算x,y方向梯度绝对值,四级计算梯度。

二值化:0是黑,255是白。

这里为什么要加一个buffer,为了增强VGA的驱动能力,增加信号的路径延时。

1654

1654

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?