项目需求:要求使用Aurora协议,采集光口传输四通道传输的数据。

环境:Vivado 2017.4

器件:Kintex-7 xc7k325tffg676-2

一、创建新的空工程

对应器件选型来创建Aurora_test的工程。

略。

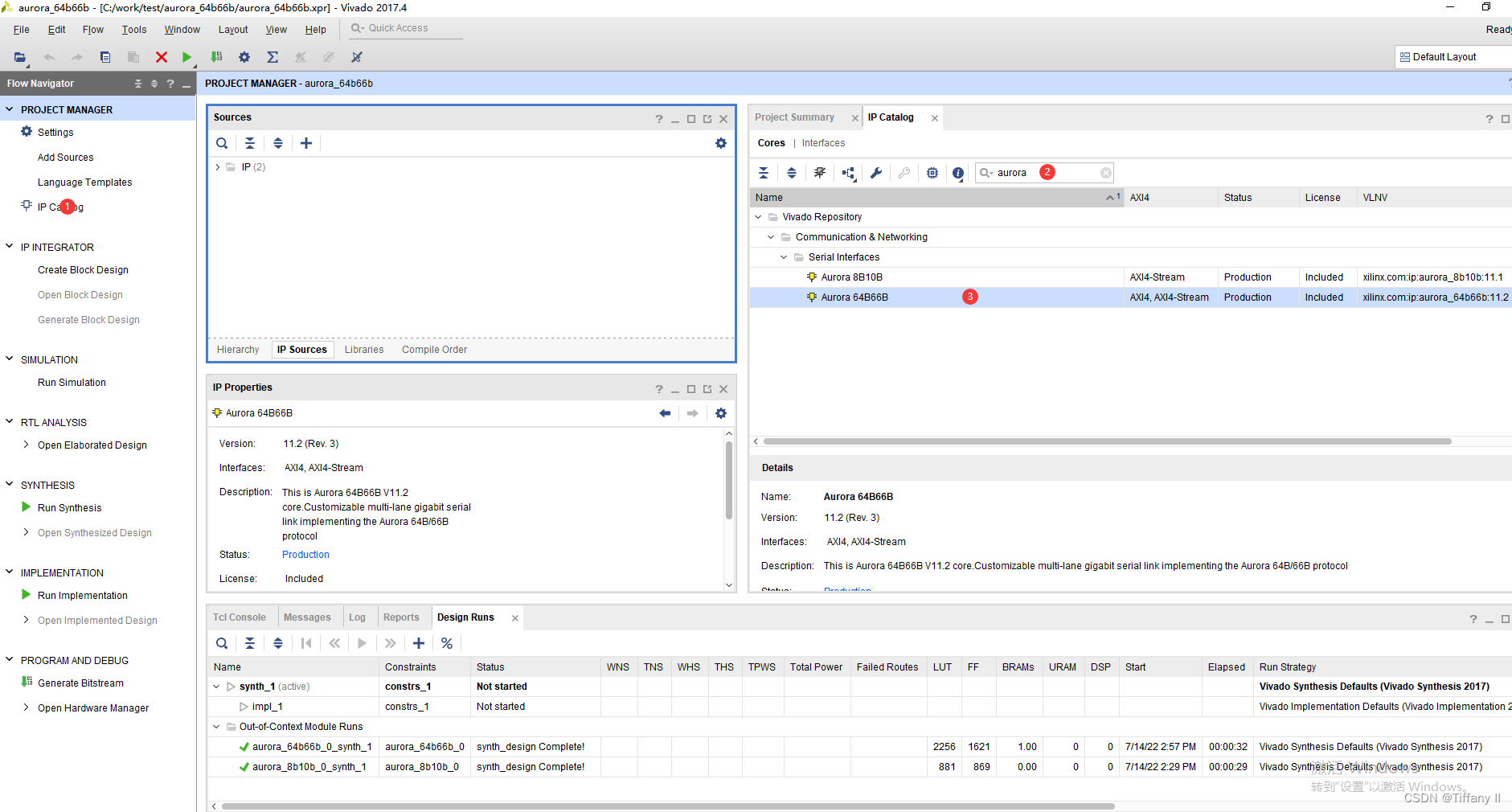

二、添加IP core

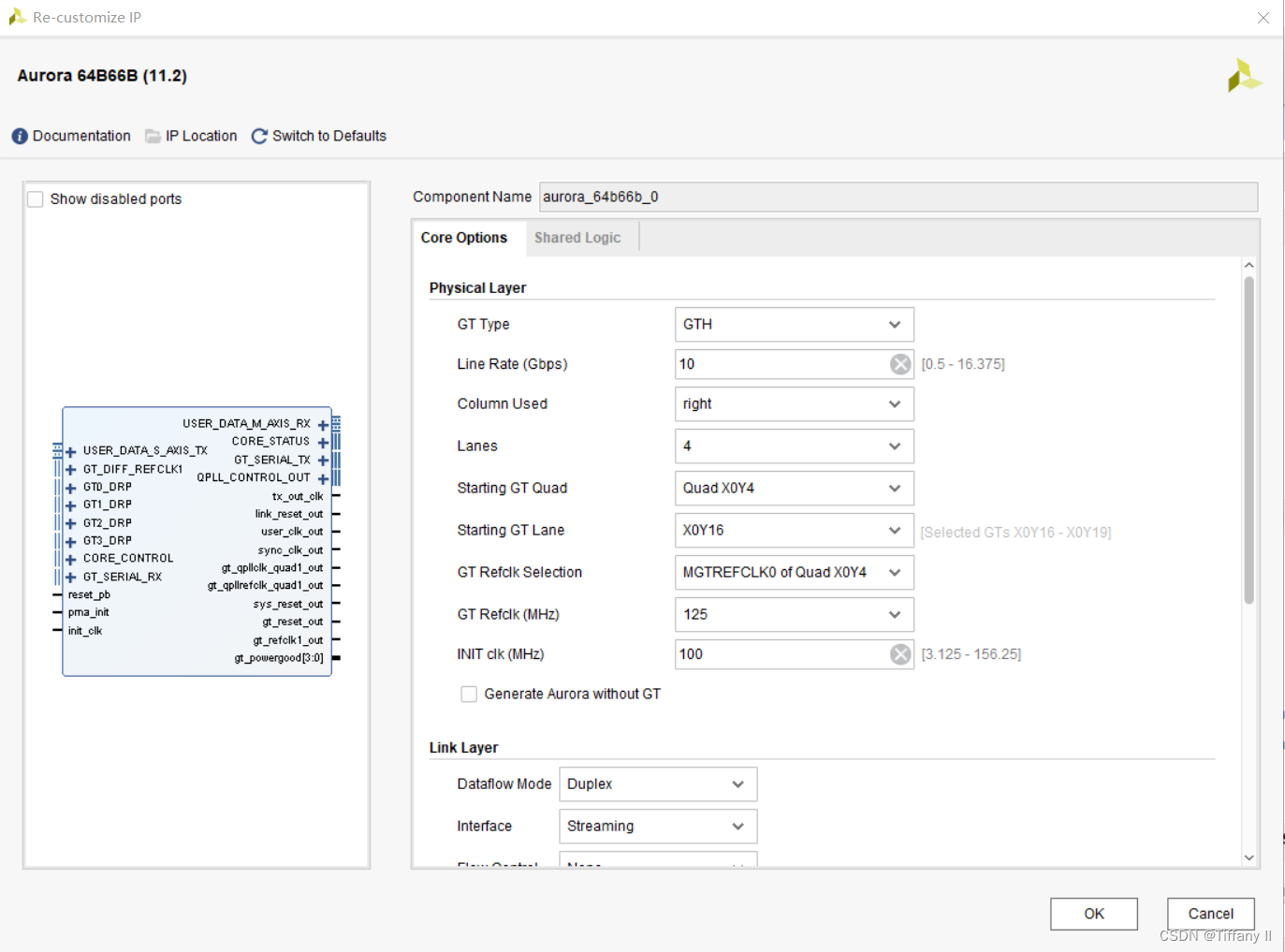

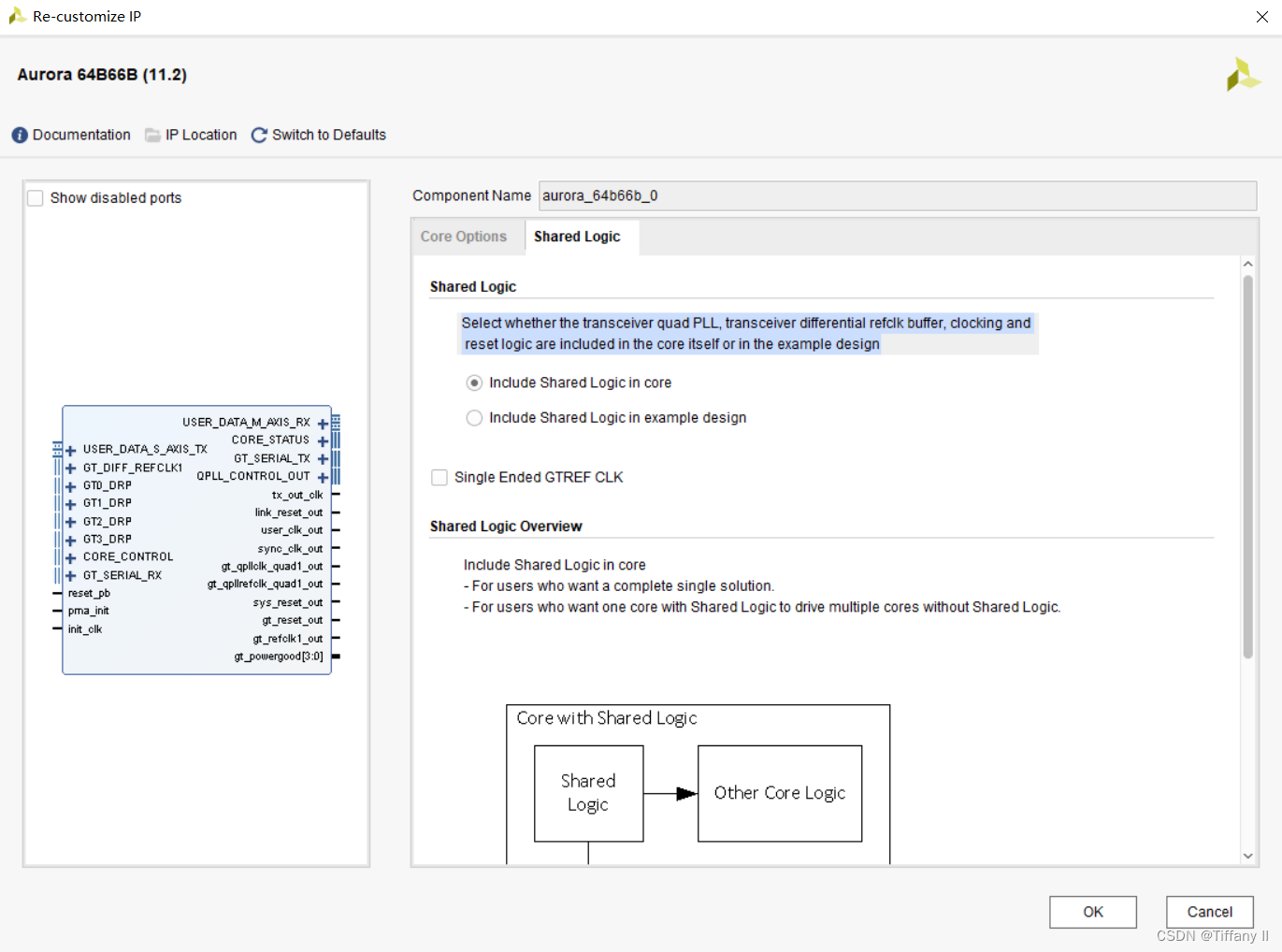

三、配置IP

xilinx官方文档pg074有对应每一个选项下的介绍,采用简单粗暴的stearming式传输。

四、IP核例化

`timescale 1ns / 1ps

module Aurora_test

(

sys_clk_p ,

sys_clk_n ,

sys_rst_n

GTH_MCLK0_P ,

GTH_MCLK0_N ,

txp ,

txn ,

rxp ,

rxn )

input wire sys_rst_p ;

input wire sys_clk_n ;

input wire sys_clk_n ;

input wire GTH_MCLK0_P ;

input wire GTH_MCLK0_N ;

output wire [3:0] txp ;

output wire [3:0] txn ;

input wire [3:0] rxp ;

input wire [3:0] rxn ;

reg [31:0] s_axi_tx_tdata ;

reg s_axi_tx_tvalid ;

wire s_axi_tx_tready ;

wire [255:0] m_axi_rx_tdata ;//to ddr4 to pcie

wire m_axi_rx_tvalid ;

wire hard_err ;

wire soft_err ;

wire channel_up ;

wire lane_up ;

wire reset ;

wire gt_reset ;//user_rst

wire [ 3:0] loopback ;

wire drpclk_in ;

wire [ 8:0] drpaddr_in ;

wire drpen_in ;

wire [15:0] drpdi_in ;

wire drprdy_out ;

wire [15:0] drpdo_out ;

wire drpwe_in ;

wire tx_lock ;

wire tx_resetdone_out ;

wire rx_resetdone_out ;

wire link_reset_out ;

wire init_clk_in ;

wire user_clk_out ;//user_clk to wirte ddr4

wire pll_not_locked_out ;

wire sys_reset_out ;

wire gt_reset_out ;

wire gt_refclk1_out ;

wire gt0_pll0refclklost_out;

wire quad1_common_lock_out;

wire gt0_pll0outclk_out ;

wire gt0_pll1outclk_out ;

wire gt0_pll0outrefclk_out;

wire gt0_pll1outrefclk_out;

wire locked ;

reg [10:0] gt_reset_cnt ;

reg start_flag ;

reg [31:0] data_cnt ;

reg [11:0] err_cnt ;

wire mmcm_not_locked_out ;

reg channel_up_r ;

reg lane_up_r ;

reg [23:0] pma_init_cnt ;

assign reset = (pma_init_cnt== 24'hFFFFFF) ? 0:1;

//assign sys_rst_n = ~gt_reset;

assign gt_reset = (pma_init_cnt>= 24'h8FFFFF) ? 0:1;

always @(posedge user_clk_out) begin

if(~sys_rst_n)begin

pma_init_cnt <= 24'b0;

end

else if(pma_init_cnt< 24'hFFFFFF)

pma_init_cnt <= pma_init_cnt + 1'b1;

else if(pma_init_cnt>= 24'hFFFFFF)

pma_init_cnt <= pma_init_cnt;

else

pma_init_cnt <= pma_init_cnt;

end

/*************ip 例化****************/

aurora_64b66b_0 inst_aurora

(

.s_axi_tx_tdata (s_axi_tx_tdata),

.s_axi_tx_tvalid (s_axi_tx_tvalid),

.s_axi_tx_tready (s_axi_tx_tready),

.m_axi_rx_tdata (m_axi_rx_tdata),

.m_axi_rx_tvalid (m_axi_rx_tvalid),

.rxp (rxp),

.rxn (rxn),

.txp (txp),

.txn (txn),

.hard_err (hard_err),

.soft_err (soft_err),

.channel_up (channel_up),

.lane_up (lane_up),

.user_clk_out (user_clk_out),//dushuju

.sync_clk_out (),

.reset_pb (reset),

.gt_rxcdrovrden_in (1'b0),

.power_down (1'b0),

.loopback (loopback),

.pma_init (gt_reset), //gt_reset

.gt0_drpdo (), //output

.gt0_drprdy (), //output

.gt0_drpaddr (9'b0), //

.gt0_drpdi (16'b0),

.gt0_drpen (1'b0),

.gt0_drpwe (1'b0),

.init_clk (clk100m), //参考时钟

.link_reset_out (link_reset_out),

.gt_pll_lock (),

.gt_refclk1_p (GTH_MCLK0_P),

.gt_refclk1_n (GTH_MCLK0_N),

.gt_refclk1_out (),

.gt_powergood (),

.gt_qpllclk_quad1_out (),

.gt_qpllrefclk_quad1_out (),

.gt_qplllock_quad1_out (),

.gt_qpllrefclklost_quad1_out (),

.sys_reset_out (),

.mmcm_not_locked_out (),

.gt_reset_out (),

.tx_out_clk ()

);

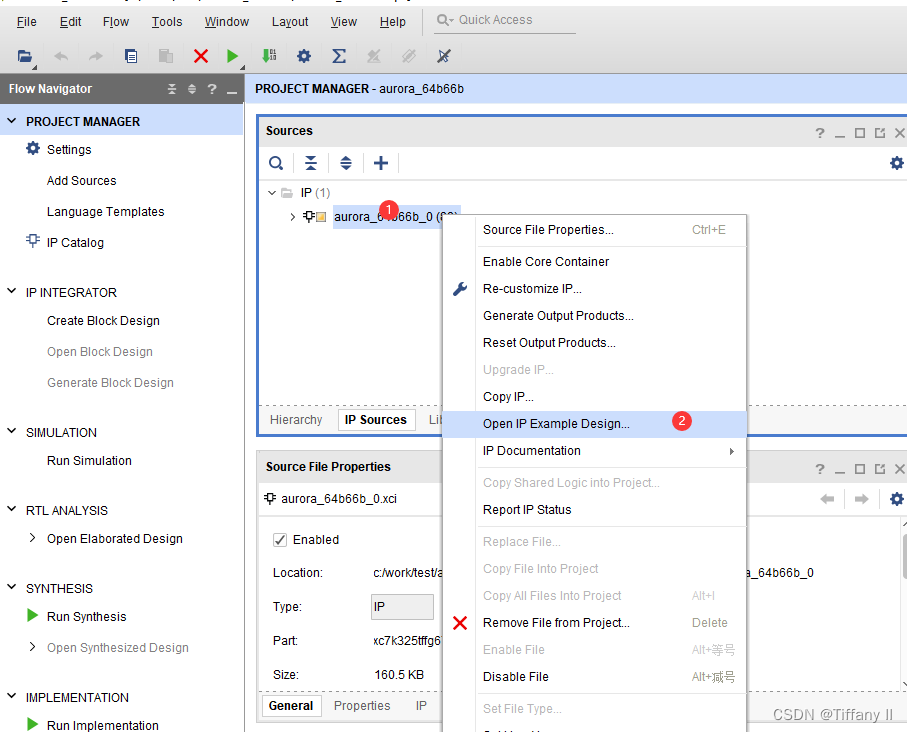

五、IP core仿真

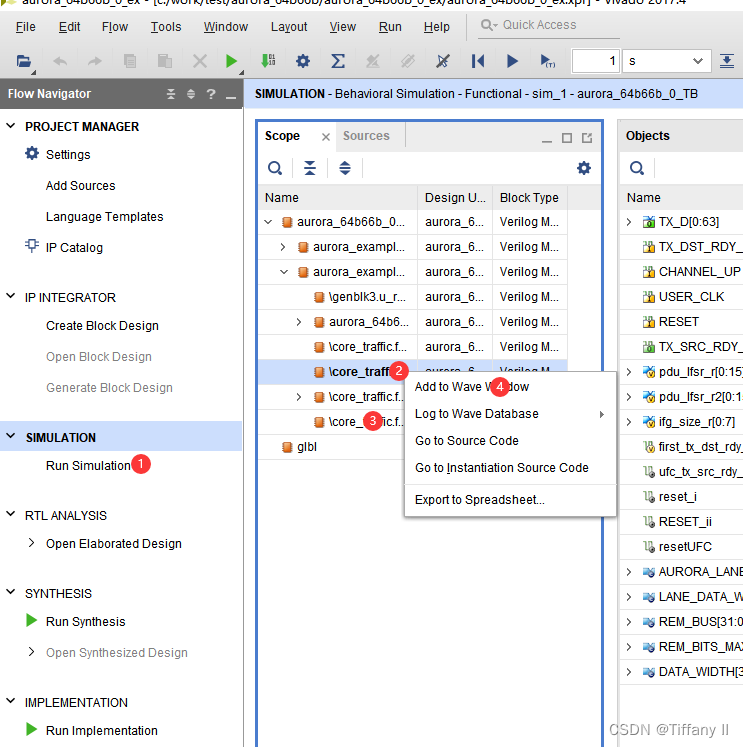

右击添加的IP ,打开IP的Example Design。 Run simulation之后,等待仿真完毕,添加这两个例化信号:

Run simulation之后,等待仿真完毕,添加这两个例化信号:

重新仿真一次,我的仿真过程有点慢不知道是什么原因,等待一段时间之后,IP的仿真波形如下:

找到TX_D和RX_D,这两个信号代表着在PL端传输的数据,添加两根参考线,可以得到TX_D一个数据传输所用的时间6.44ns。

六、仿真速率的计算

1s传输多少个字节:1s ÷ 6.44ns = 155,279,503.1055901 个

一个字节根据协议在数据通道传输是66位:

用上面的字节数在乘上66 bit = 10,248,447,204.96894 bps ≈ 10.25Gbps

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?