一、1位二进制数全加器

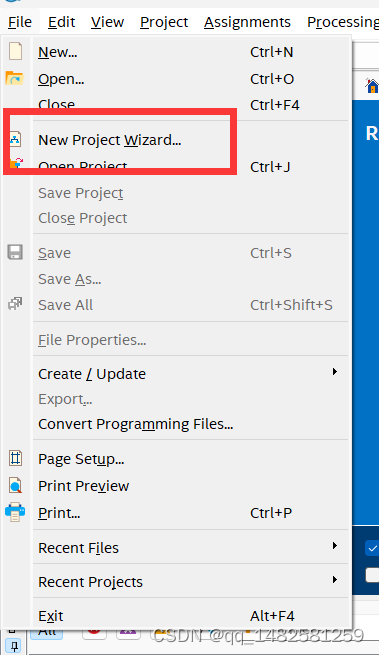

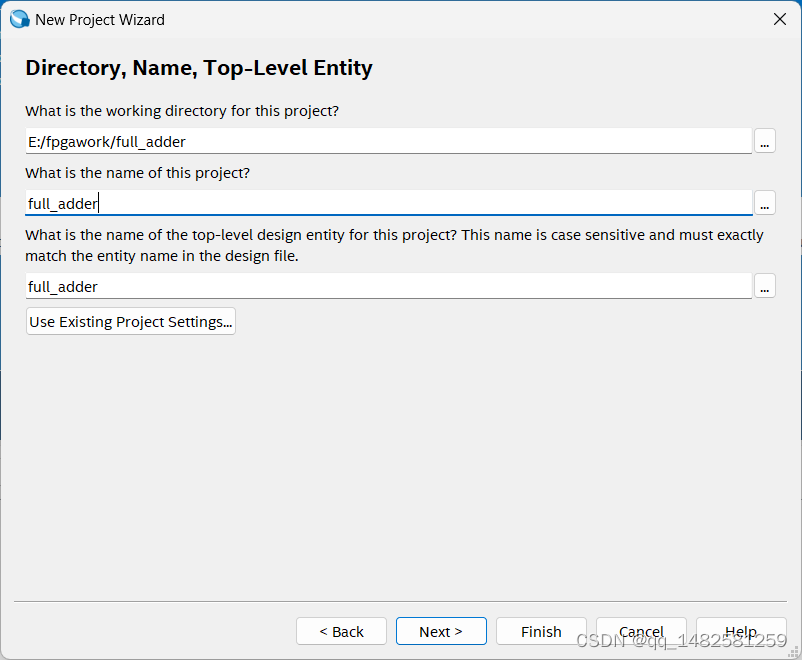

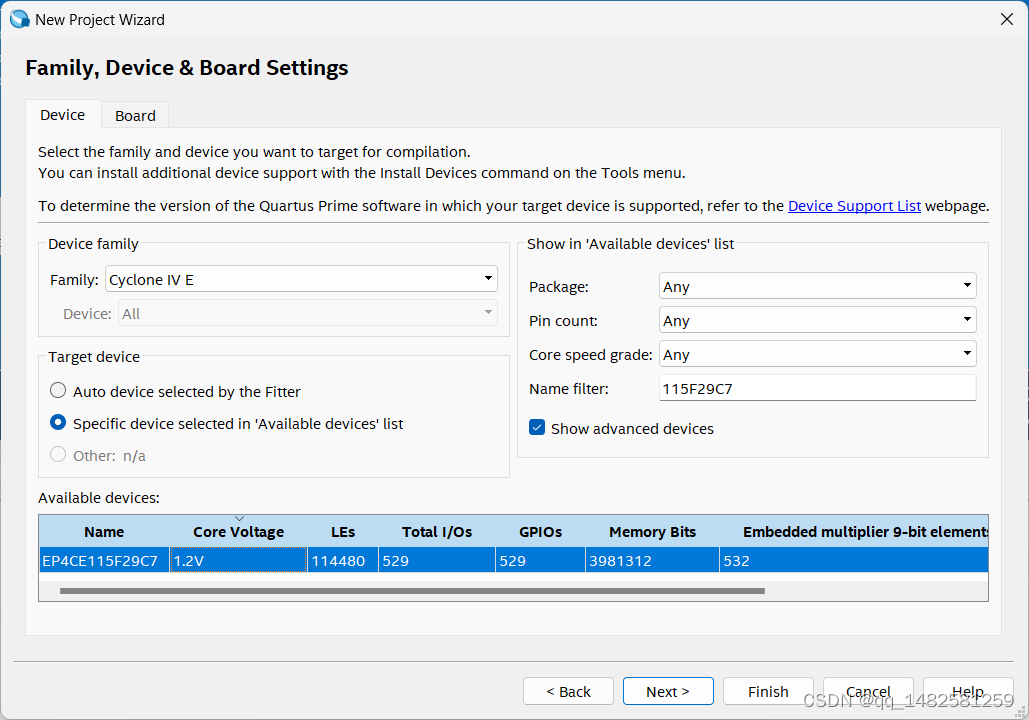

创建工程

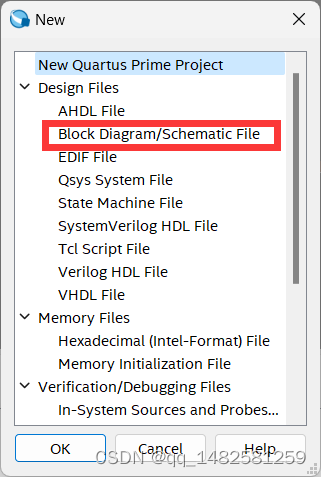

创建好后,点击FIle,new

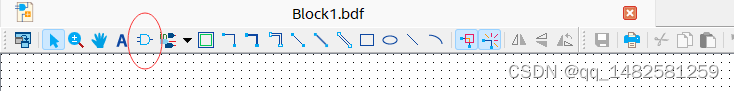

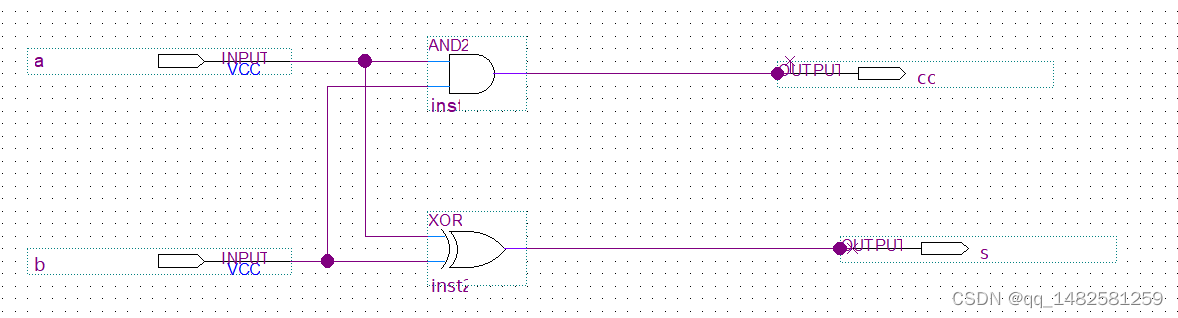

(1)选择元件,and2和xor,按如下连线(半加器)

编译后查看电路图

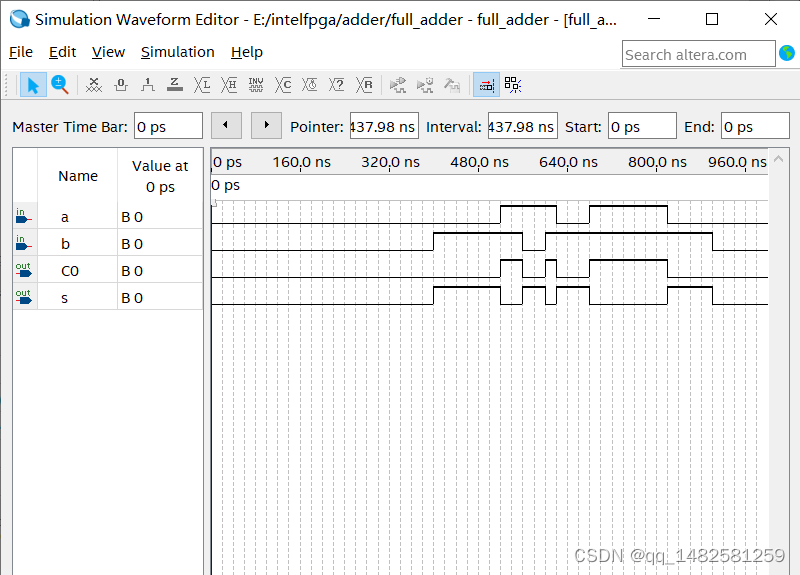

仿真结果

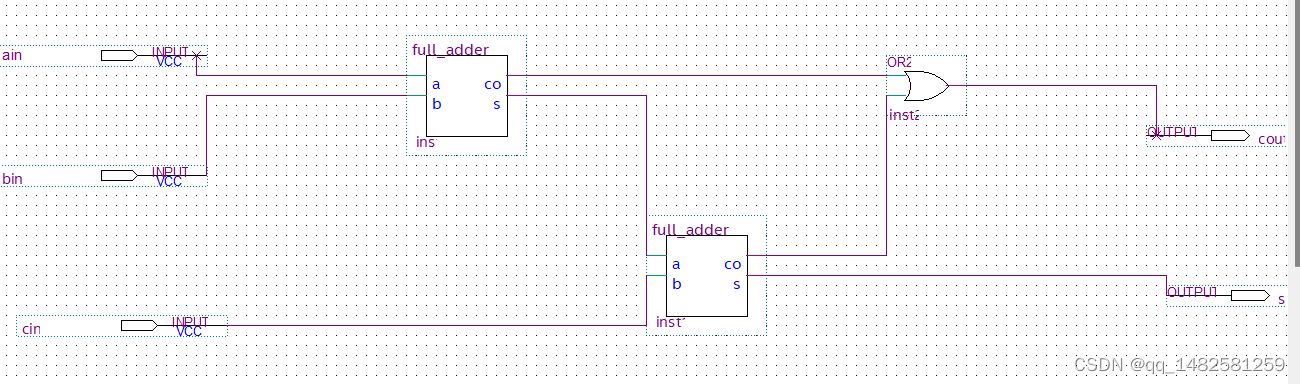

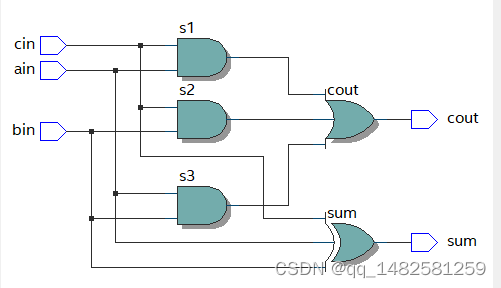

(2)全加器原理图

编译后查看仿真结果

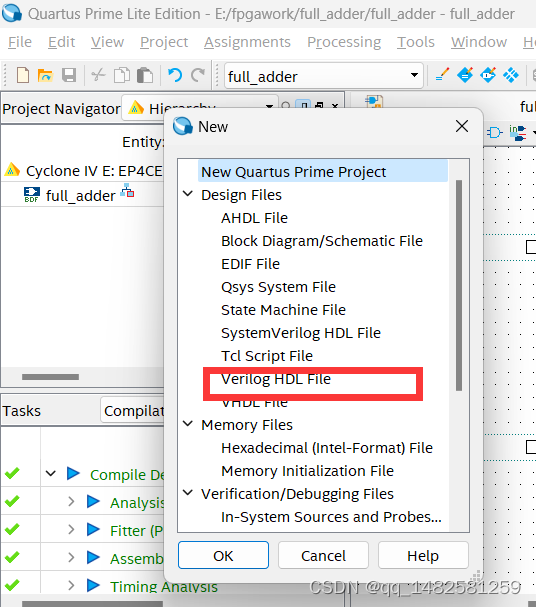

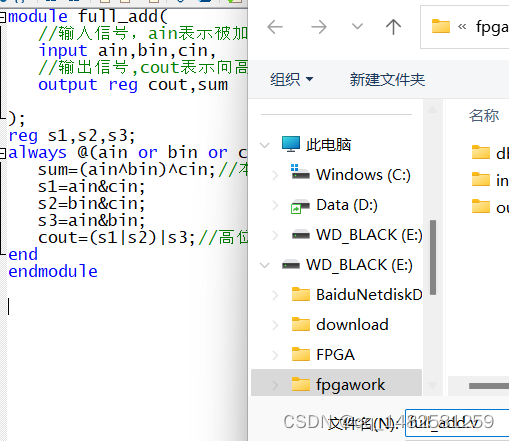

(3)通过verilog语言实现

代码

module full_add(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

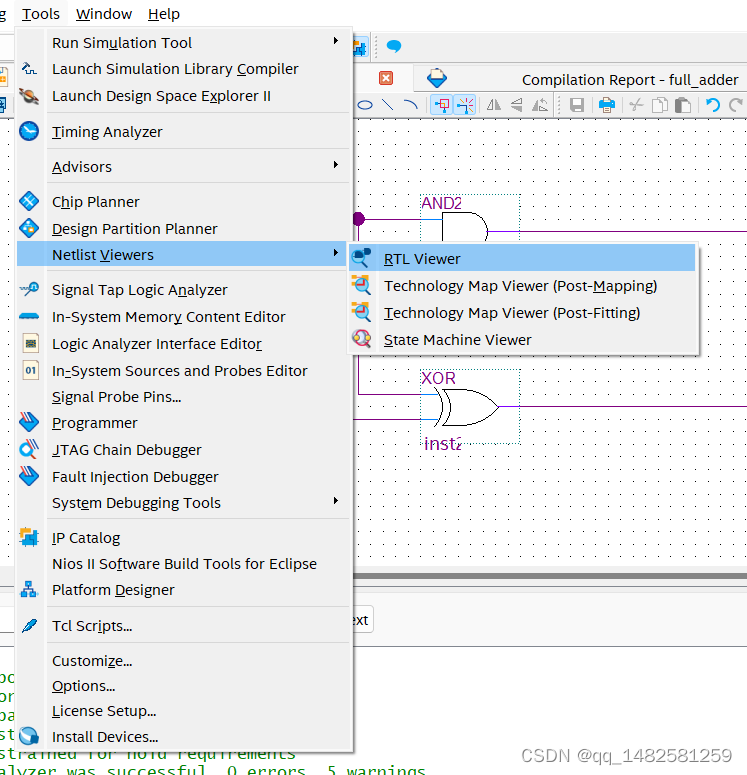

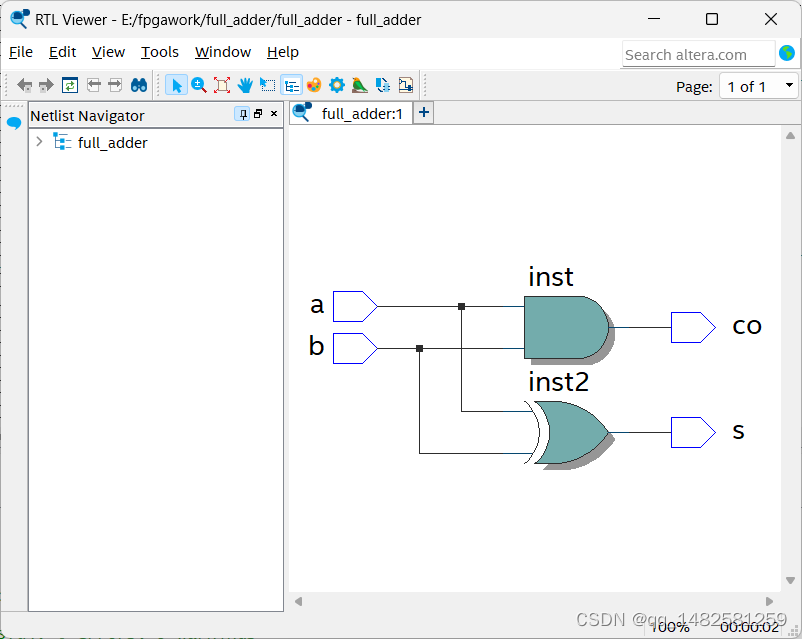

保持工程名一致,编译后查看原理图,没换工程的话,记得设为顶层

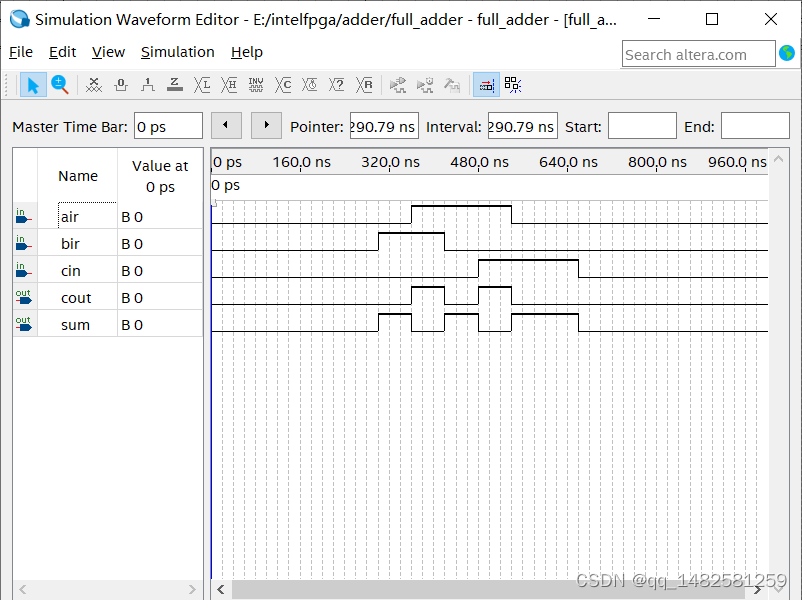

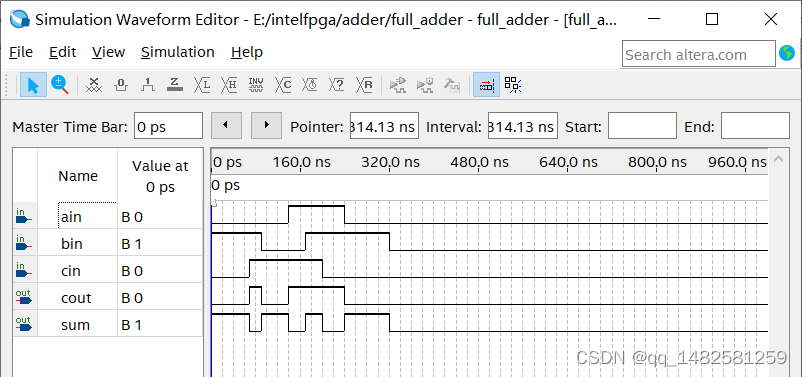

查看仿真结果

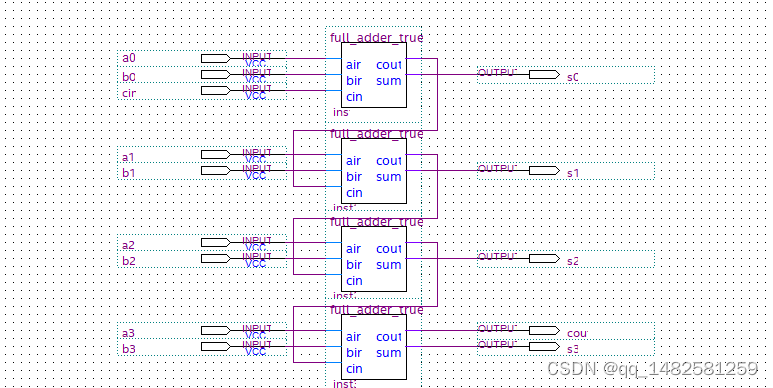

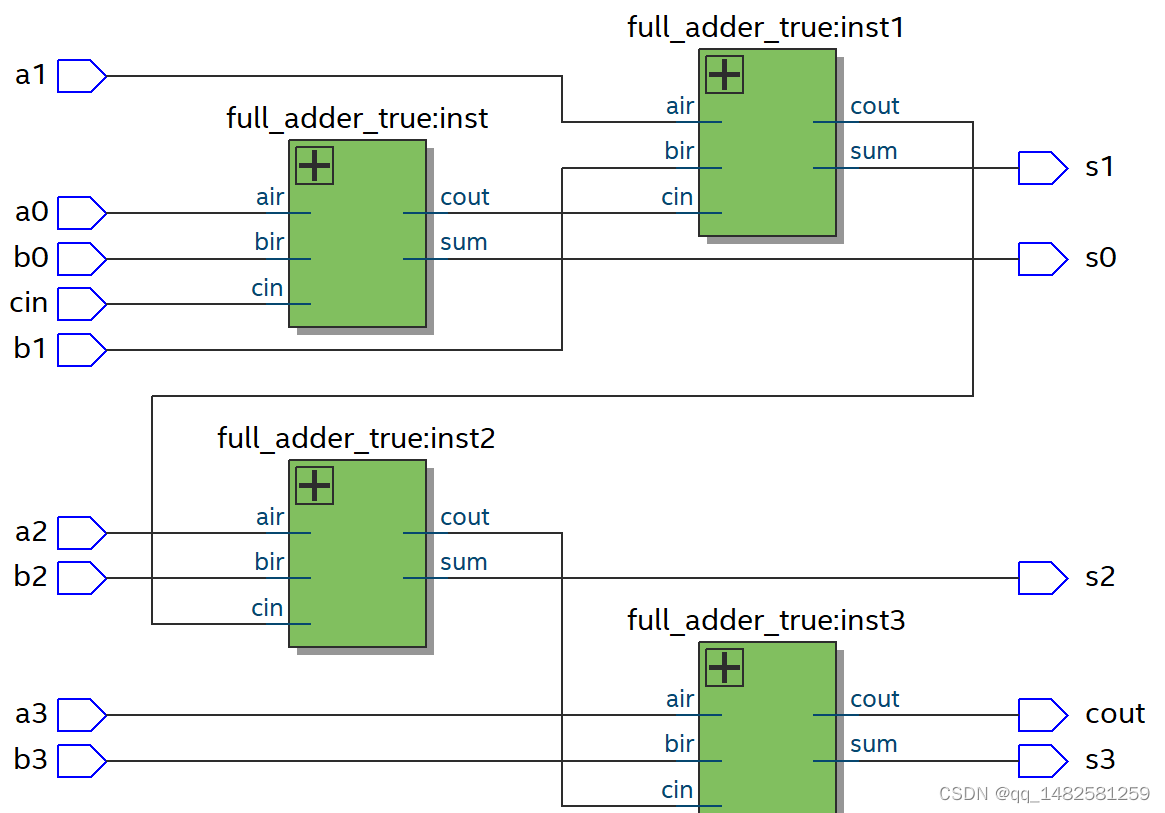

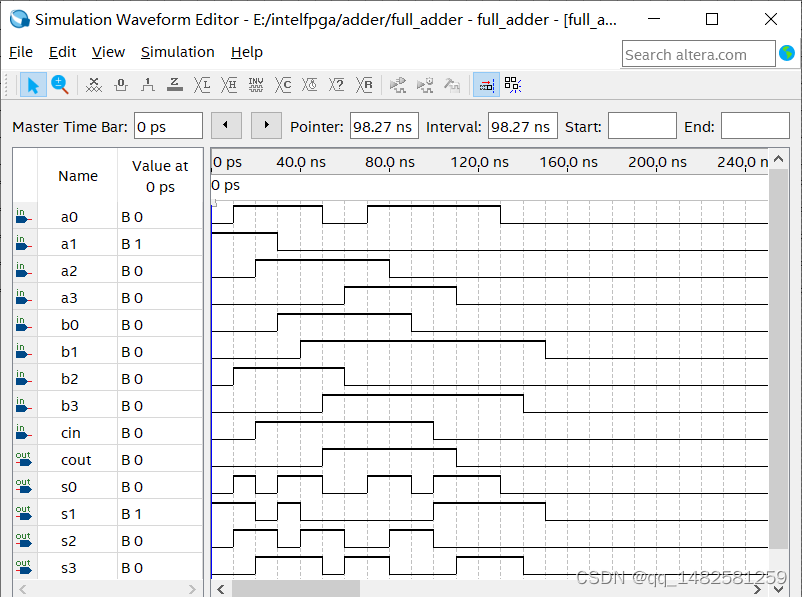

二、四位全加器

把前面设计的一位全加器保存为元件

四位全加器调用

电路图

仿真结果

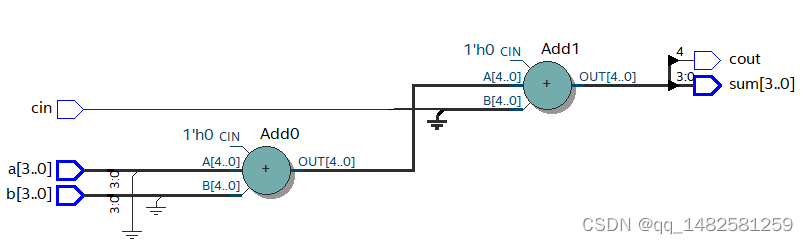

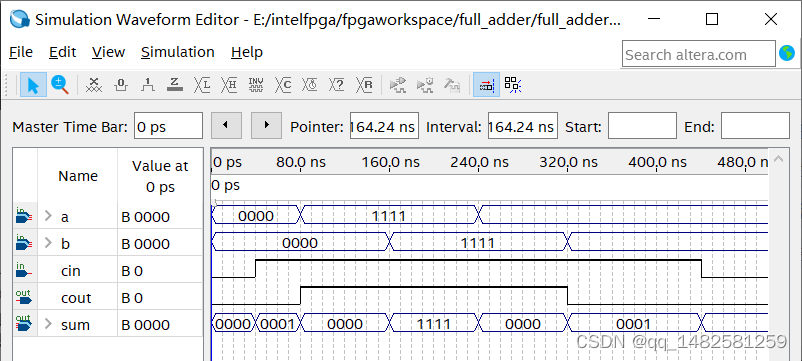

Verilog语言实现

module four_adder(

input[3:0] a,b,

input cin,

output[3:0] sum,

output cout

);

assign{cout,sum} = a+b+cin;

endmodule

仿真结果

三、总结

分别通过原理图和verilog语言实现半加器和一位全加器,并且通过将一位全加器设置为元件来调用实现四位全加器。了解了FPGA开发的一些基础知识。

四、参考链接

https://blog.csdn.net/cjhz2333/article/details/129766541?spm=1001.2014.3001.5502

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?