一、实验器材

DE2-E115 FPGA开发板 + Quartus + Modelsim

学习并掌握HC_SR04模块的使用

二、实验原理

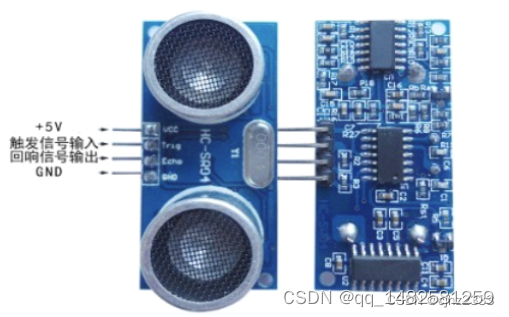

HC-SR04引脚

VCC: 电源引脚,超声波模块工作电压为5伏。

Trig: 是Trigger(触发)这个单词的缩写,该引脚用于触发超声波脉冲。

Echo: 该引脚会在高电平和低电平之间转换,当检测到障碍物时,在高电平保持的时间就表示信号发射出去并反射回来的时间。

GND: 接地引脚。

工作原理

模块测距工作原理:

(1) 主控设备给 Trig 脚提供一个 10us 的脉冲信号。

(2) HC-SR04 接收到信号,开始发送超声波,并把 Echo置为高电平,然后准备接收返回的超声波。

(3) HC-SR04 接收到返回的超声波,把 Echo 置为低电平。

(4) Echo 高电平持续的时间就是超声波从发射到返回的时间间隔。

我们知道距离=速度x时间,要求出超声波模块到障碍物之间的距离,我们就需要知道速度和时间。速度就是340m/s,也就是声音在空气中传播的速度,转换城cm/μs单位就是0.034 cm/μs。时间的话,由于我们得到的是信号从发射到返回的时间值,所以需要除以2。

最终得到的计算公式为:距离 = 0.034 cm/μs * 时间(μs) / 2

三、模块设计

测距模块代码

/*================================================*\

Filename ﹕

Author ﹕

Description ﹕超声波触发测距模块

波形周期300ms,前10us高电平

Called by ﹕

Revision History ﹕ mm/dd/202x

Revision 1.0

Email﹕

Company﹕

\*================================================*/

module hc_sr_trig(

input wire clk_us , //system clock 1MHz

input wire Rst_n , //reset ,low valid

output wire trig //触发测距信号

);

//Parameter Declarations

parameter CYCLE_MAX = 19'd300_000;

//Interrnal wire/reg declarations

reg [18:00] cnt ; //Counter

wire add_cnt ; //Counter Enable

wire end_cnt ; //Counter Reset

//Logic Description

always @(posedge clk_us or negedge Rst_n)begin

if(!Rst_n)begin

cnt <= 'd0;

end

else if(add_cnt)begin

if(end_cnt)begin

cnt <= 'd0;

end

else begin

cnt <= cnt + 1'b1;

end

end

else begin

cnt <= cnt;

end

end

assign add_cnt = 1'b1;

assign end_cnt = add_cnt && cnt >= CYCLE_MAX - 9'd1;

assign trig = cnt < 15 ? 1'b1 : 1'b0;

endmodule

时钟模块

/*================================================*\

Filename ﹕

Author ﹕

Description ﹕产生周期为1us的时钟信号

Called by ﹕

Revision History ﹕ mm/dd/202x

Revision 1.0

Email﹕

Company﹕

\*================================================*/

module clk_div(

input wire Clk , //system clock 50MHz

input wire Rst_n , //reset ,low valid

output wire clk_us //

);

//Parameter Declarations

parameter CNT_MAX = 19'd50;//1us的计数值为 50 * Tclk(20ns)

//Interrnal wire/reg declarations

reg [5:00] cnt ; //Counter

wire add_cnt ; //Counter Enable

wire end_cnt ; //Counter Reset

//Logic Description

always @(posedge Clk or negedge Rst_n)begin

if(!Rst_n)begin

cnt <= 'd0;

end

else if(add_cnt)begin

if(end_cnt)begin

cnt <= 'd0;

end

else begin

cnt <= cnt + 1'b1;

end

end

else begin

cnt <= cnt;

end

end

assign add_cnt = 1'b1;

assign end_cnt = add_cnt && cnt >= CNT_MAX - 19'd1;

assign clk_us = end_cnt;

endmodule

ECHO引脚与TRIG引脚

/*================================================*\

Filename ﹕

Author ﹕

Description ﹕超声波检测距离模块

本模块理论测试距离 2cm~510cm

输出结果保留两位小数

Called by ﹕

Revision History ﹕ mm/dd/202x

Revision 1.0

Email﹕

Company﹕

\*================================================*/

module hc_sr_echo(

input wire Clk , //clock 50MHz

input wire clk_us , //system clock 1MHz

input wire Rst_n , //reset ,low valid

input wire echo , //

output wire [18:00] data_o //检测距离,保留3位小数,*1000实现

);

/* S(um) = 17 * t --> x.abc cm */

//Parameter Declarations

parameter T_MAX = 16'd60_000;//510cm 对应计数值

//Interrnal wire/reg declarations

reg r1_echo,r2_echo; //边沿检测

wire echo_pos,echo_neg; //

reg [15:00] cnt ; //Counter

wire add_cnt ; //Counter Enable

wire end_cnt ; //Counter Reset

reg [18:00] data_r ;

//Logic Description

//如果使用clk_us 检测边沿,延时2us,差值过大

always @(posedge Clk or negedge Rst_n)begin

if(!Rst_n)begin

r1_echo <= 1'b0;

r2_echo <= 1'b0;

end

else begin

r1_echo <= echo;

r2_echo <= r1_echo;

end

end

assign echo_pos = r1_echo & ~r2_echo;

assign echo_neg = ~r1_echo & r2_echo;

always @(posedge clk_us or negedge Rst_n)begin

if(!Rst_n)begin

cnt <= 'd0;

end

else if(add_cnt)begin

if(end_cnt)begin

cnt <= cnt;

end

else begin

cnt <= cnt + 1'b1;

end

end

else begin //echo 低电平 归零

cnt <= 'd0;

end

end

assign add_cnt = echo;

assign end_cnt = add_cnt && cnt >= T_MAX - 1; //超出最大测量范围则保持不变,极限

always @(posedge Clk or negedge Rst_n)begin

if(!Rst_n)begin

data_r <= 'd2;

end

else if(echo_neg)begin

data_r <= (cnt << 4) + cnt;

end

else begin

data_r <= data_r;

end

end //always end

assign data_o = data_r >> 1;

endmodule

/*================================================*\

Filename ﹕

Author ﹕

Description ﹕超声波触发测距模块

波形周期300ms,前10us高电平

Called by ﹕

Revision History ﹕ mm/dd/202x

Revision 1.0

Email﹕

Company﹕

\*================================================*/

module hc_sr_trig(

input wire clk_us , //system clock 1MHz

input wire Rst_n , //reset ,low valid

output wire trig //触发测距信号

);

//Parameter Declarations

parameter CYCLE_MAX = 19'd300_000;

//Interrnal wire/reg declarations

reg [18:00] cnt ; //Counter

wire add_cnt ; //Counter Enable

wire end_cnt ; //Counter Reset

//Logic Description

always @(posedge clk_us or negedge Rst_n)begin

if(!Rst_n)begin

cnt <= 'd0;

end

else if(add_cnt)begin

if(end_cnt)begin

cnt <= 'd0;

end

else begin

cnt <= cnt + 1'b1;

end

end

else begin

cnt <= cnt;

end

end

assign add_cnt = 1'b1;

assign end_cnt = add_cnt && cnt >= CYCLE_MAX - 9'd1;

assign trig = cnt < 15 ? 1'b1 : 1'b0;

endmodule

顶层文件

/*================================================*\

Filename ﹕tb_hc_sr.v

Author ﹕Adolph

Description ﹕超声波驱动测试文件

Called by ﹕

Revision History ﹕ mm/dd/202x

Revision 1.0

Email﹕

Company﹕

\*================================================*/

`timescale 1ns/1ns //仿真系统时间尺度定义

`define clk_period 20 //时钟周期参数定义

module tb_hc_sr();

//激励信号定义

reg Clk ;

reg Rst_n ;

reg echo; //

//响应信号定义

wire trig ;

wire [6:0] hex1 ;

wire [6:0] hex2 ;

wire [6:0] hex3 ;

wire [6:0] hex4 ;

wire [6:0] hex5 ;

wire [6:0] hex6 ;

wire [6:0] hex7 ;

wire [6:0] hex8 ;

//实例化

HC_SR04_TOP HC_SR04_TOP(

/*input */.Clk (Clk ), //system clock 50MHz

/*input */.Rst_n (Rst_n ), //reset ,low valid

/*input */.echo (echo ), //

/*output */.trig (trig ), //触发测距信号

/*output [6:0] */.hex1 (hex1 ), // -共阳极,低电平有效

/*output [6:0] */.hex2 (hex2 ), // -

/*output [6:0] */.hex3 (hex3 ), // -

/*output [6:0] */.hex4 (hex4 ), //连接符

/*output [6:0] */.hex5 (hex5 ), //cm -

/*output [6:0] */.hex6 (hex6 ), //cm -

/*output [6:0] */.hex7 (hex7 ), //cm -

/*output [6:0] */.hex8 (hex8 ) //熄灭

);

//产生时钟

initial Clk = 1'b0;

always #(`clk_period / 2) Clk = ~Clk;

//产生激励

initial begin

Rst_n = 1'b0;

echo = 1'b0;

#(`clk_period * 20 + 3);

Rst_n = 1'b1;

#(`clk_period * 20);

wait(HC_SR04_TOP.hc_sr_driver.hc_sr_trig.cnt == 240);

echo = 1'b1;//测试超声波信号发送完成,echo拉高

#(50 * `clk_period * 2500 + 7);

echo = 1'b0;

#(`clk_period * 200);

$stop(2);

end

endmodule

然后编译,进行烧录。

总结

测距功能基本实现,如果使用平面物体近距离测试则误差不大,对于远距离测距则误差较大如果采用更好的滤波方式,那么数据的采集可能更精准。

826

826

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?