一 IIC协议

1.1 iic介绍

1.2 iic传输速率

标准:100kbit/s,

快速:400kbit/s,

高速:3.4Mbit/s。

在读写EEPROM实验中,速率为(50Mbit/s)/250=200Kbit/s

1.3 iic特点 (物理层)

(1) 它是一个支持多设备的总线(支持多主机多从机)。

(2) IIC总线只使用两条总线线路,一条双向串行数据线(SDA) 一条串行时钟线(SCL)。数据线即用来表示数据,时钟线用于数据收发同步。

(3) 每个连接到IIC总线的设备都有一个独立的地址,主机可以利用设备独立地址访问不同设备。

(4) IIC总线通过上拉电阻接到电源。当IIC设备空闲时,设备会输出高阻态,当所有设备都空闲,都输出高阻态时,由上拉电阻把IIC总线拉成高电平。

(5) IIC总线具有仲裁机制。

1.4 iic时序

空闲状态:

I2C总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级场效应管均处在截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。

起始信号:

由主机产生,在SCL保持高电平期间,SDA的电平被拉低,称为 I2C总线总线的起始信号,标志着一次数据传输开始。起始信号由主机主动建立的,在建立该信号之前I2C总线必须处于空闲状态。

数据传输:

以字节为单位进行串行传输数据,每传输1bit数据都需要一个时钟周期,即20 * 250ns,在时钟线为低电平的时候进行传输数据,高电平的时候保持不变,进行采样。在时钟信号线SCL为低电平时,将需要写入的数据提前给到数据信号线SDA,方便时钟信号线SCL为高电平时,准确获取到数据信号线SDA上的数据。

当sda、scl为低电平时,发送端开始发送数据,当接收完8bit数据会通过数据线反馈一个应答信号ACK ,应答信号低电平有效,表示已经接收到了该字节;当反馈为高电平时,表示接收该字节失败,在反馈期间 ,即接收端 在第九个时钟脉冲之前将SDA拉低,确保在该时钟周期保持低电平。另外发送多字节数据会在 有效应答后scl低电平期间继续发送数据,知道发送完所有字节数据,反馈一个NACK高电平,在scl高电平期间采样,此时表示发送数据完成,结束发送。进入停止位。

应答信号:

12C总线上的所有数据都是以字节传送的,发送端每发送一个字节,就必须在第9个SCL脉冲期间释放SDA,由接收端反馈一个应答信号。应答信号为低电平时,称为有效应答位(ACK),表示接收端成功接收了该字节;应答信号为高电平时,称为非应答位(NACK),表示接收端接收该字节失败。对于反馈有效应答位ACK的要求是,接收端在第9个时钟脉冲之前的低电平期间将SDA拉低,并且确保在该时钟周期的高电平期间保持低电平。如果接收端是主控端,则在它收到最后一个字节后,发送一个NACK信号,以通知被控发送端结束数据发送,并释放SDA线,以便主控接收器发送停止信号。

停止信号:

在SCL保持高电平期间,SDA被释放,返回高电平,称为I2C总线的停止信号,标志着一次数据传输的终止。停止信号由主机主动建立的,建立 该信号之后,I2C总线将返回空闲状态。

二 SCCB协议

2.1 SCCB介绍

2.2 数据传输

在SCCB协议中,一个基本传输单元称作一个相(phase),一个相包含总共9比特,前8比特为数据,它的响应信号ACK被称为一个传输单元的第9位,分为Don’t care和 NA(No ACK)。Don’t care位由从机产生;NA位由主机产生,由于SCCB不支持多字节的读写,NA位必须为高电平。sCCB没有重复起始的概念,因此在 SCCB的读周期中,当主机发送完片内寄存器地址后,必须发送总线停止条件。不然在发送读命令时,从机将不能产生 Don’t care 响应信号。

当写数据到从机被定义为写传输,当从机中读数据被定义为读传输,每一个传输都要有开始位(start)和结束位(sotp);完整的数据传输包括两个或三个阶段,每一个阶段包含9位数据,其中高8位为所要传输的数据,最低位根据器件读写情况有不同的取值:

每一个阶段组成:8位数据+don’t care/NA

如果是主机发送数据,即进行写操作,第9位就为don’t care;如果是从机发送数据,即为读操作,第九位就为NA。

dont care:

摄像头发送数据给主机,不在乎发送0或者1,

NA:

主机给从机发送停止位,sda为高电平

2.3 写操作

三相写传输或者四相写

ID Addr : 表示从机的器件地址 以及 一位读写控制位 7位器件地址 + 1位写控制位 0

Sub Addr :表示从机的寄存器地址

Write Data :主机给从机写的一字节的数据

X : 从机反馈don‘t care,不在乎0或者1

特别注意 :ov5640摄像头的器件地址有两个字节,因此写操作是四相写传输,先 起始位+器件地址+字节高地址+字节字节+一字节数据

2.4 读操作

读操作分两个阶段:

第一阶段 :

写:两相写传输或者三相写

ID Addr : 表示从机的器件地址 以及 一位读写控制位 7位器件地址 + 1位写控制位 0

Sub Addr :表示从机的寄存器地址

X : 从机反馈don‘t care,不在乎0或者1

第二阶段 :

ID Addr : 表示从机的器件地址 以及 一位读写控制位 7位器件地址 + 1位读控制位 1

Read Data :从机发送给主机的八位数据

X : 从机反馈don‘t care,不在乎0或者1

NA :主机应答从机发送数据,为高电平

三 EEPROM

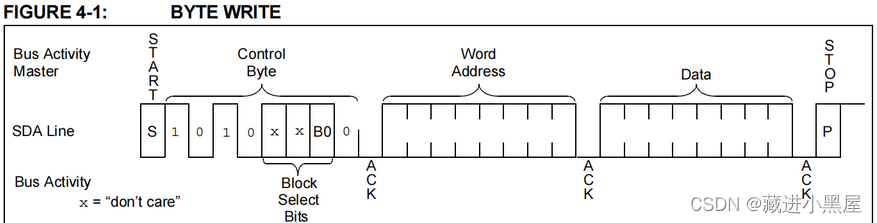

3.1 写操作时序

写操作,发起始位->写写控制字->接收ACK->写字节地址->接收ACK->写数据接收ACK->发停止位。

写控制字:

{7’b101000,1’b0}

单字节写:一次只写一个字节。

页写:一次可以写16个字节。

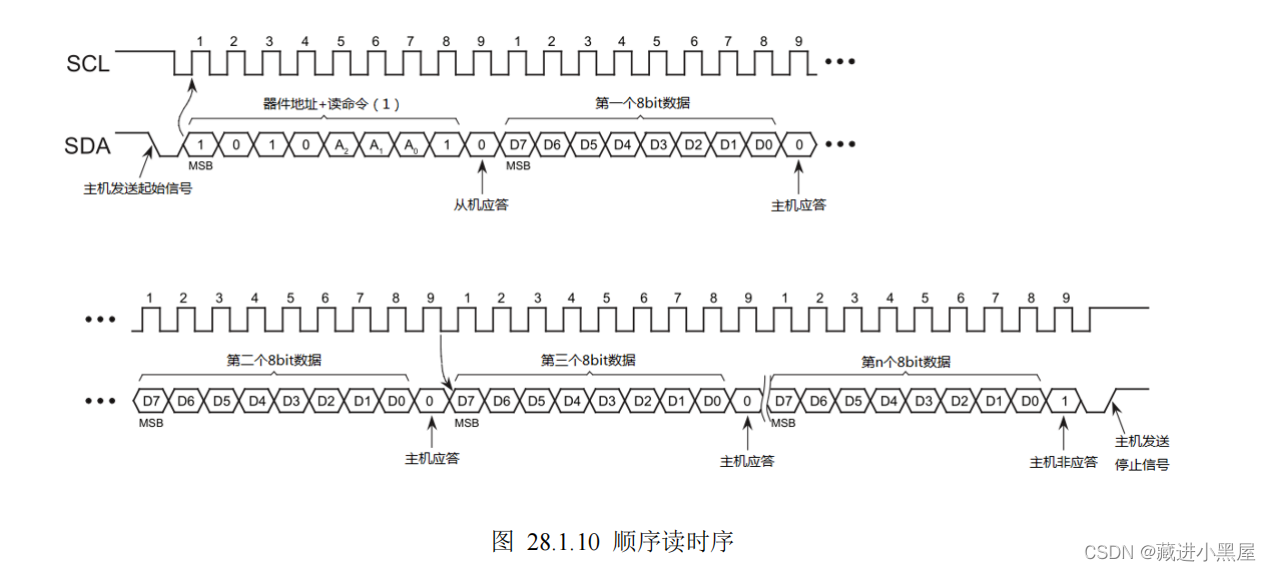

3.2 读操作时序

从当前地址读:

发起始位->写控制字->接收ACK->写读地址->接收读数据->发NACK->发停止位。

随机读:

随机读,发起始位->写控制字->写读地址->接收ACK->发起始位->写读控制字->接收读数据->发NACK->发停止位。

顺序读:

顺序读,发起始位->写控制字->写读地址->接收ACK->发起始位->写读控制字->接收读数据->发ACK->接收读数据->发NACK->发停止位。

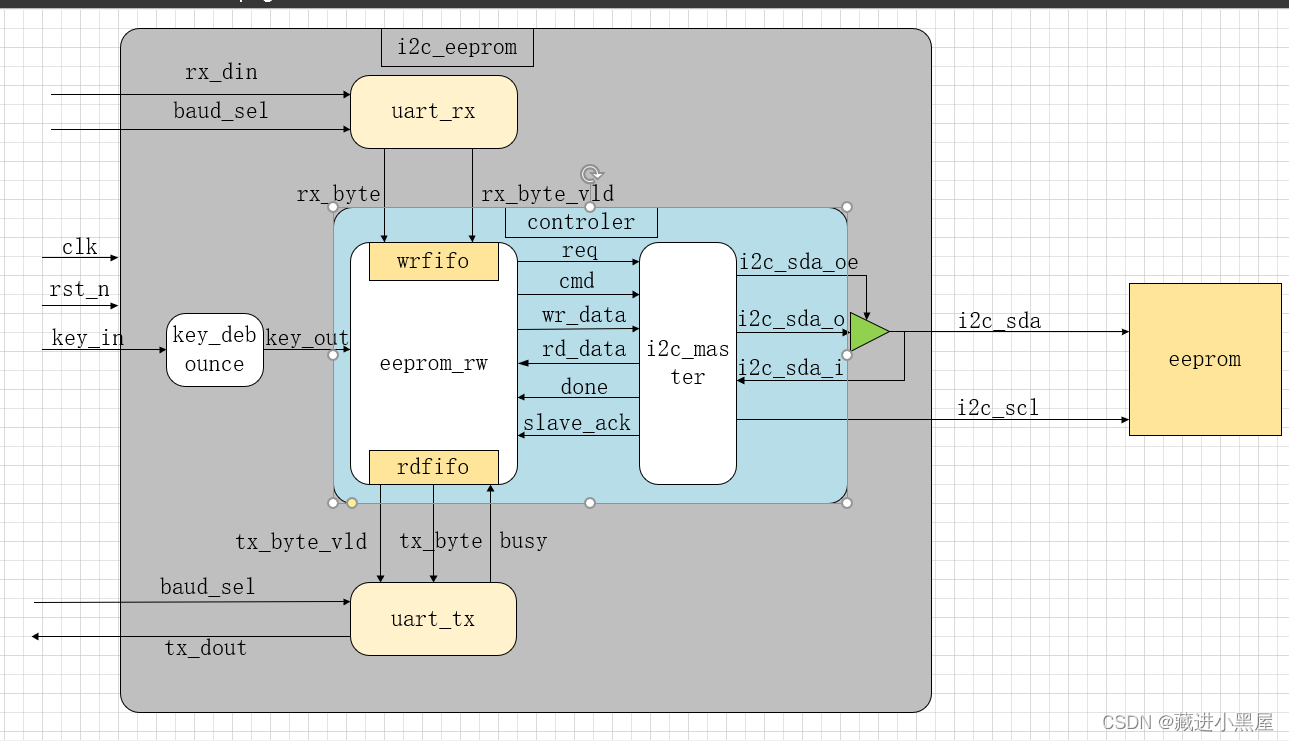

四 设计方案

4.1 I2C数据传输状态图

4.2 EEPROM 读写控制状态输出

4.3 系统框图

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?