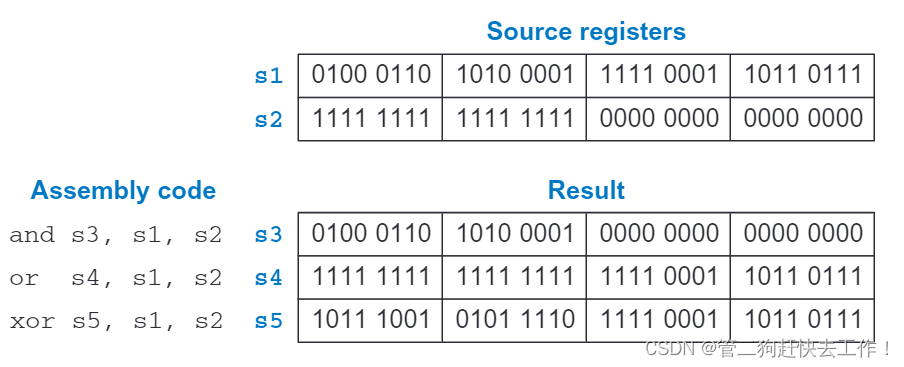

RISC-V的逻辑指令是用于对两个寄存器或一个寄存器和一个立即数进行按位的逻辑运算,并将结果存放在另一个寄存器中的指令。按位的逻辑运算就是把两个操作数的每一位分别进行相应的逻辑运算,得到一个新的位。RISC-V的逻辑指令有以下几种:

- and:按位与运算,只有当两个操作数的对应位都为1时,结果位才为1,否则为0。

- or:按位或运算,只有当两个操作数的对应位都为0时,结果位才为0,否则为1。

- xor:按位异或运算,只有当两个操作数的对应位不相同时,结果位才为1,否则为0。

- not:按位非运算,将一个操作数的每一位取反,即0变为1,1变为0。

这些逻辑指令都有两种格式,一种是R-Format,用于对两个寄存器进行逻辑运算;另一种是I-Format,用于对一个寄存器和一个立即数进行逻辑运算。R-Format的指令格式如下:

| 类型 | opcode | rd | funct3 | rs1 | rs2 | funct7 |

|---|---|---|---|---|---|---|

| R-Format | 0110011 | 5位 | 3位 | 5位 | 5位 | 7位 |

其中,opcode是指令的操作码,rd是目的寄存器,funct3是功能码,rs1和rs2是源寄存器,funct7是扩展功能码。不同的逻辑指令有不同的功能码和扩展功能码。例如,and指令的funct3和funct7都是0000000;or指令的funct3是0010000,funct7是0000000;xor指令的funct3是0100000,funct7是0000000。

I-Format的指令格式如下:

| 类型 | opcode | rd | funct3 | rs1 | imm |

|---|---|---|---|---|---|

| I-Format | 0010011 | 5位 | 3位 | 5位 | 12位 |

其中,opcode是指令的操作码,rd是目的寄存器,funct3是功能码,rs1是源寄存器,imm是立即数。不同的逻辑指令有不同的功能码。例如,andi指令的funct3是111;ori指令的funct3是110;xori指令的funct3是100。

下面给出一些使用RISC-V逻辑指令的案例:

- and指令可以用于清除或屏蔽某些位,即将某些位强制为0。例如,要清除x5寄存器中低8位,并将结果放在x6中,可以使用andi x6,x5,0xFF00。这里的立即数0xFF00是一个12位的二进制数,其低8位为0,高4位为1。

- or指令可以用于合并两个寄存器中的位域。例如,要将x7寄存器中高16位和x8寄存器中低16位合并,并将结果放在x9中,可以使用slli x10,x7,16; ori x9,x10,x8。这里先将x7左移16位得到x10,再将x10和x8按位或得到x9。

- xor指令可以用于判断两个寄存器中是否有相同的位。例如,要检查x11和x12是否有相同的第4位,并将结果放在x13中(如果相同则为1,否则为0),可以使用xor x13,x11,x12; srai x13,x13,3; andi x13,x13,1。这里先将x11和x12按位异或得到x13,再将x13右移3位得到第4位,再将x13和1按位与得到结果。

- not指令可以用于取反一个寄存器中的所有位。例如,要将x14中的所有位取反,并将结果放在x15中,可以使用xori x15,x14,-1。这里的立即数-1是一个12位的二进制数,其所有位都为1。与所有1进行异或操作就相当于取反。

在下图中给出部分案例供参考 :

6372

6372

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?