实验一:

教材书《数字逻辑基础与Verilog设计》P112.图4.28-4选1多路选择器

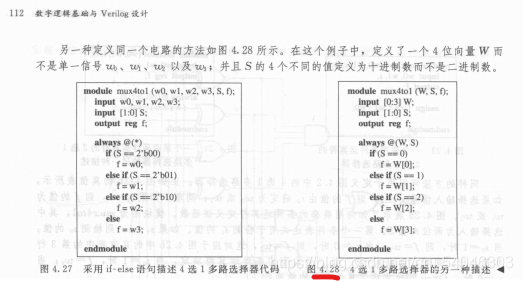

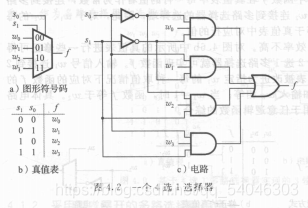

4选1多路选择器的另一种描述(可以采用If-else语句描述4选1多路选择器)

本例定义了一个4位向量w而不是单一信号w0,w1,w2以及w3;并且s的4个不同的值定义为十进制数而不是二进制数。

实验设计代码:

module mux4to1(w,s,f);

input [0:3]w;

input [1:0]s;

output reg f;

always@(w,s)

if(s==0)

f=w[0];

else if (s==1)

f=w[1];

else if (s==2)

f=w[2];

else

f=w[3];

endmodule

测试代码:

module tb_mux4to1;

reg [0:3] w;

reg [1:0] s;

wire f;

mux4to1 mymux4t01(w,s,f);

always # 10 w[0] =~ w[0];

always # 20 w[1] =~ w[1];

always # 40 w[2] =~ w[2];

always # 80 w[3] =~ w[3];

initial

begin

s = 1'b0; w = 4'h0;

#160 $stop;

end

always #10 s = s+1;

endmodule

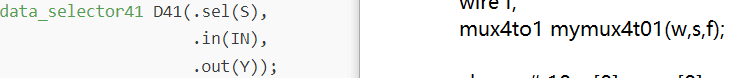

左图按名字写的,右图按顺序写的

要验证这个四选一的多路选择器的代码,即给输入赋值然后验证输出对不对,先给w,s赋值,然后根据仿真出来的波形图来可以验证f的值,所以我们需要写一个测试代码来验证仿真出来的波形图的正确性。

编写测试代码时注意这里的 模块实例化,其语法结构为:

模块名称即已经定义好了的其它模块的模块名,实例名称是在本模块内定义的新名称。端口连接是在当前模块中把实例化的模块所包含的端口进行连接,有两种连接方式,即按顺序连接和按名称连接。

按顺序连接对初学者来说比较直观和简便,它要求连接到实例的信号,必须与模块声明时目标端口在端口列表中的位置保持一致。

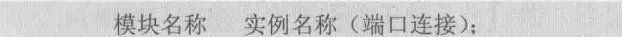

另外,要遵循图2-2所示的连接规则,把实例化的模块的输入端口所连接的信号定义为reg,把实例化模块的输出端口所连接的信号定义为wire,若实例化模块中有双向端口,所连接的信号也要定义为wire,这是必须遵守的语法要求!

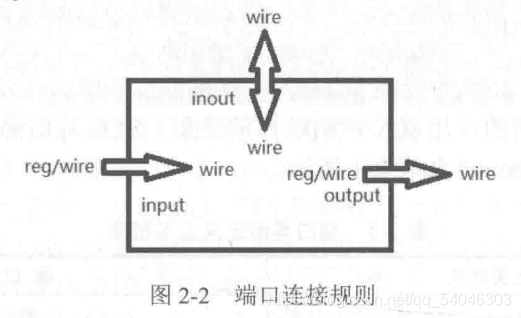

eg:按顺序连接实例化端口

此代码共有两个模块,第二个模块是四选一数据选择器,只给出了模块定义和端口声明部分,内部的逻辑门调用没有给出。第一个模块是一个测试模块Test,模块中调用了四选一数据选择器,重新命名为mymux,连接顺序按照下面模块MUX4x1定义的顺序依次连接。

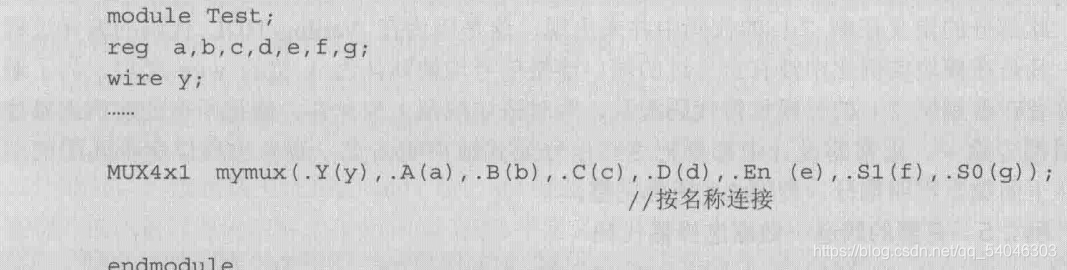

eg:按名称连接实例化端口

该例子特地把端口顺序调整得与原 MUX4x1 中端口列表的顺序列表不同,把En_信号放到了第6位而不是在最后。同时,为了显示连接信号的名称与原定义端口名称无关,这里采用了无意义的字母abcdefg作为Test模块中的连接线。

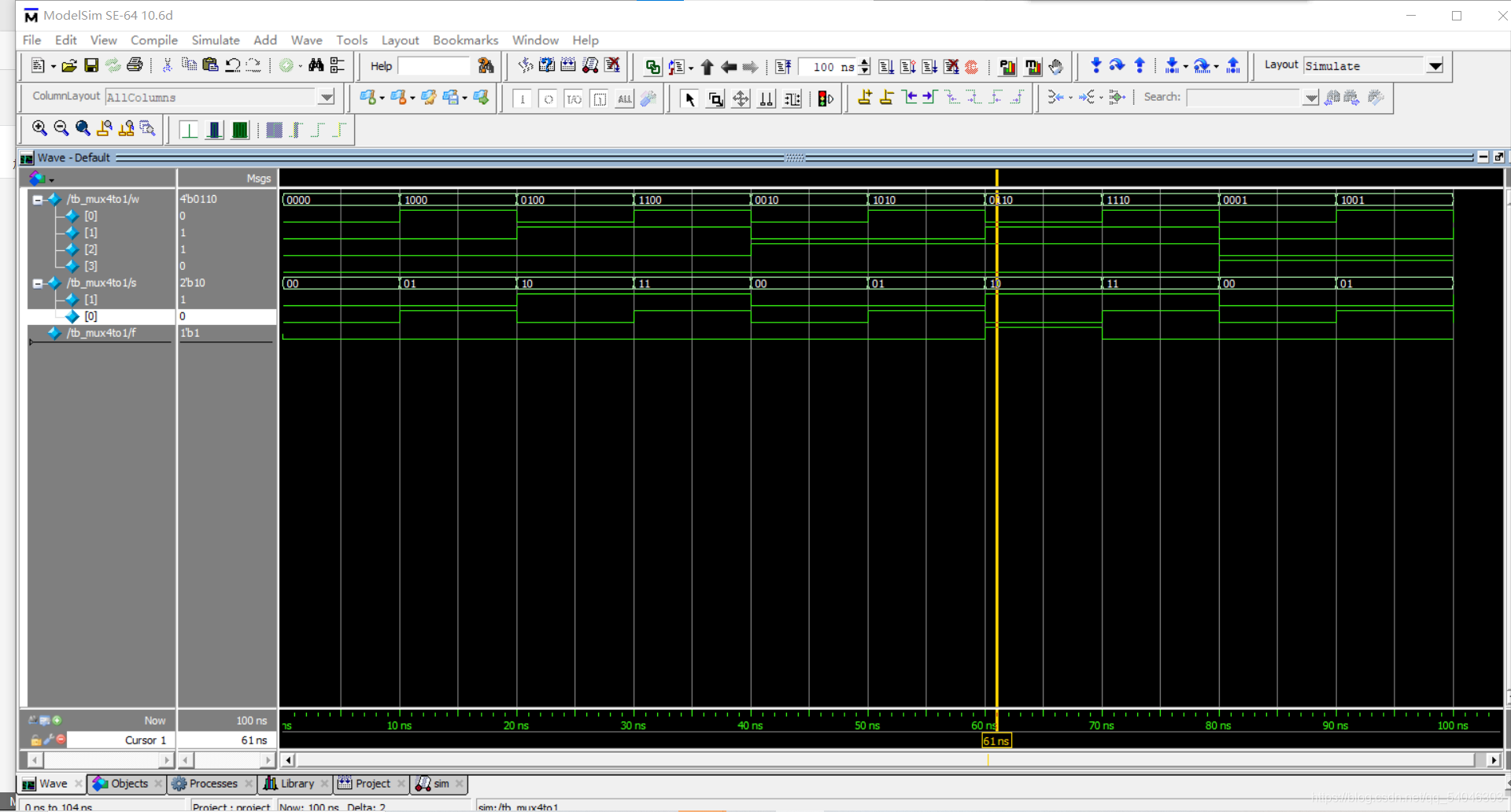

实验结果截图:

仿真出来可以看到,当s为00时,f=w[0],对应的波形相同,s为01时, f=w[1],s为10时,f=w[2],s为11时,f=w[3].

实验视频:

4选1多路选择器

3126

3126

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?