目录

1 T触发器

1.1 T触发器简介

在某一些应用场景中,需要这样的一种逻辑功能触发器,当控制信号T=1时每来一个时钟信号状态就翻转一次。T触发器是数字电路中的一种基本电子元件,主要用于控制信号的翻转和频率分频。

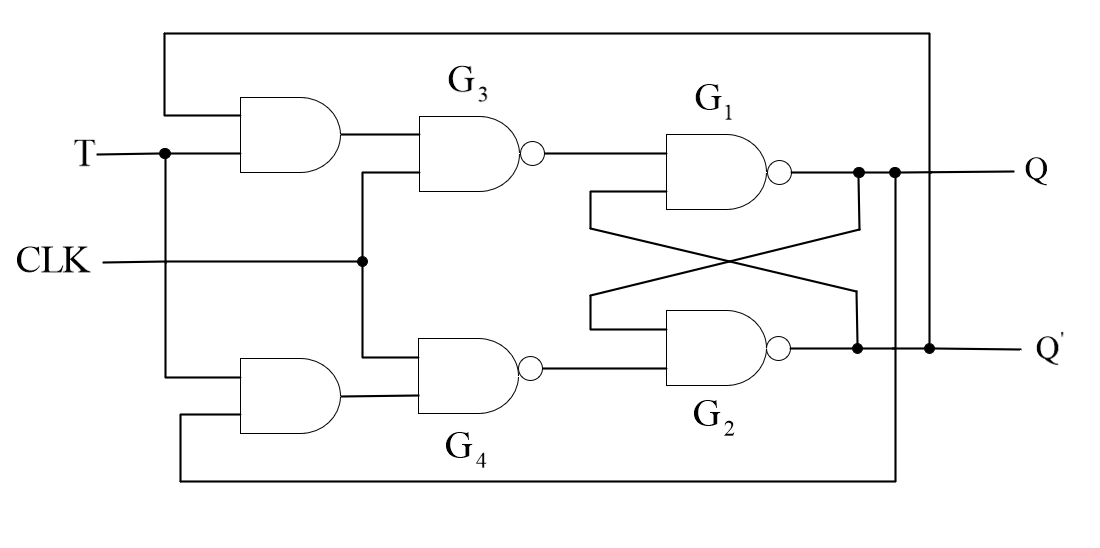

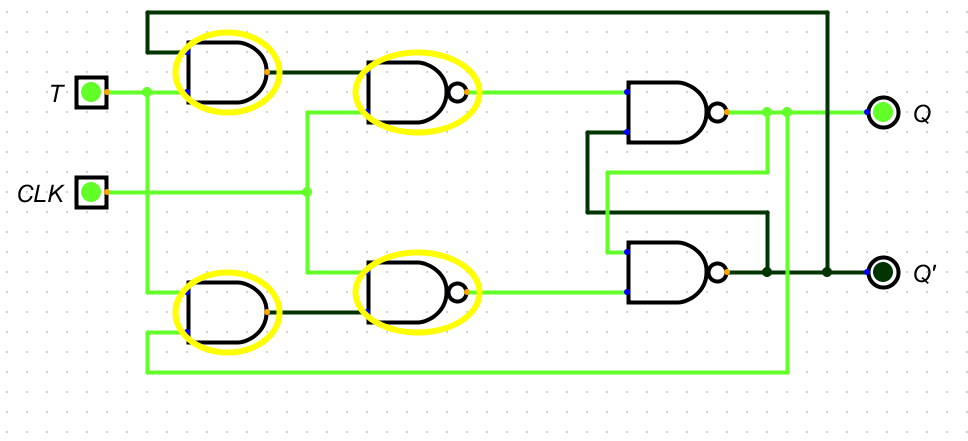

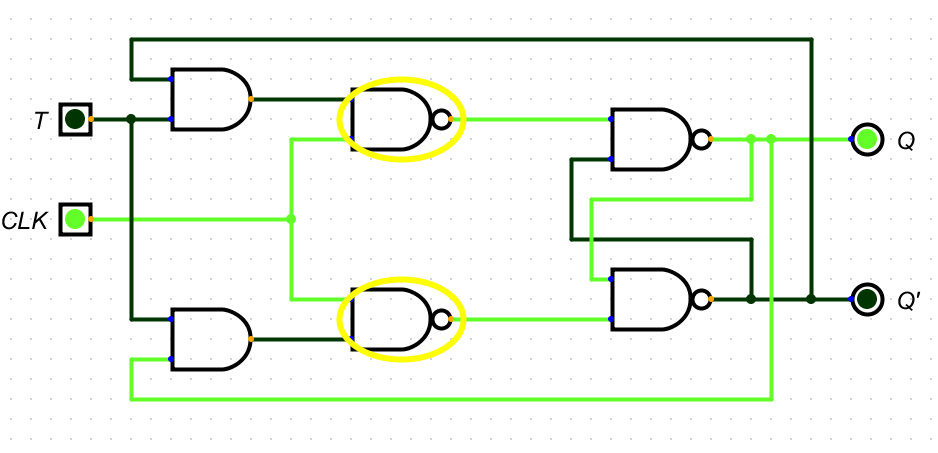

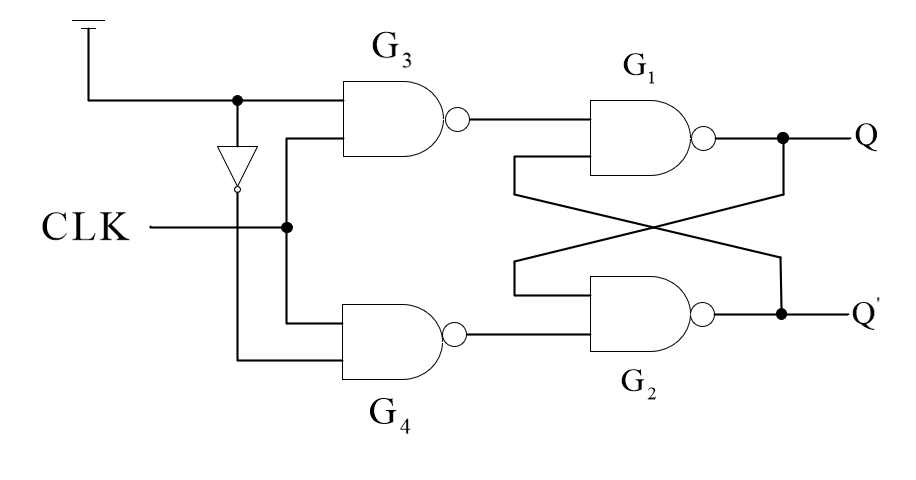

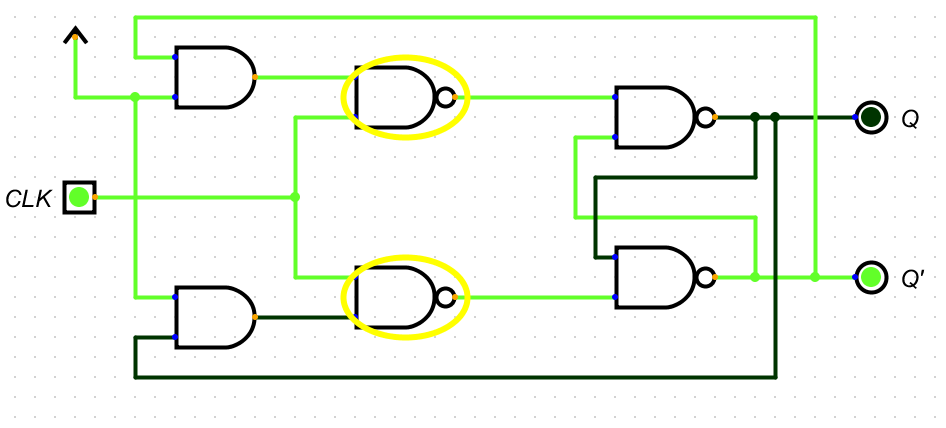

T触发器的电路图是在JK触发器的电路图进行改动,即将输入端J和K连接在一起,电路图如下所示:

需要注意的是,T触发器不是JK触发器的改进,而是JK触发器功能的简化,T触发器是JK触发器J=K时的特例。

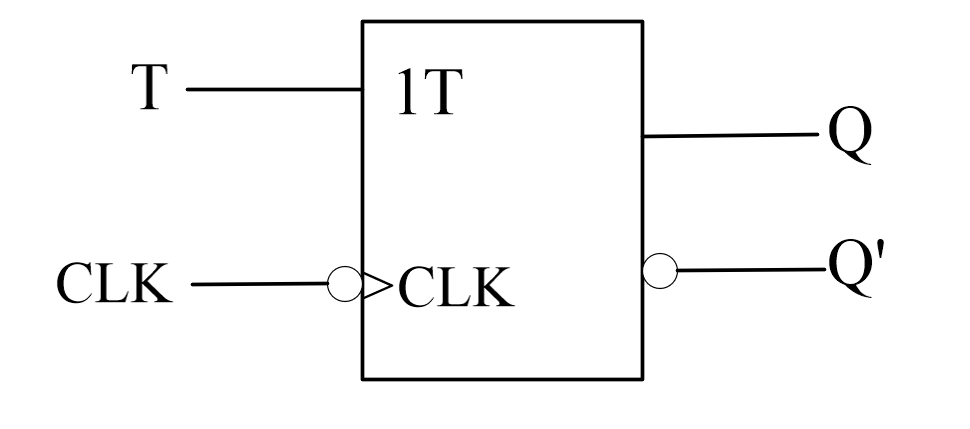

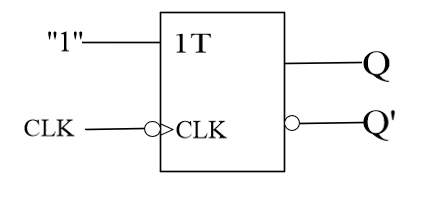

T触发器的图形符号为:

T触发器的特性表如下所示:

| T | Q | Q* |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

从T触发器的特性表可以得到T触发器的特性方程为:

1.2 使用Digital软件来绘制T触发器

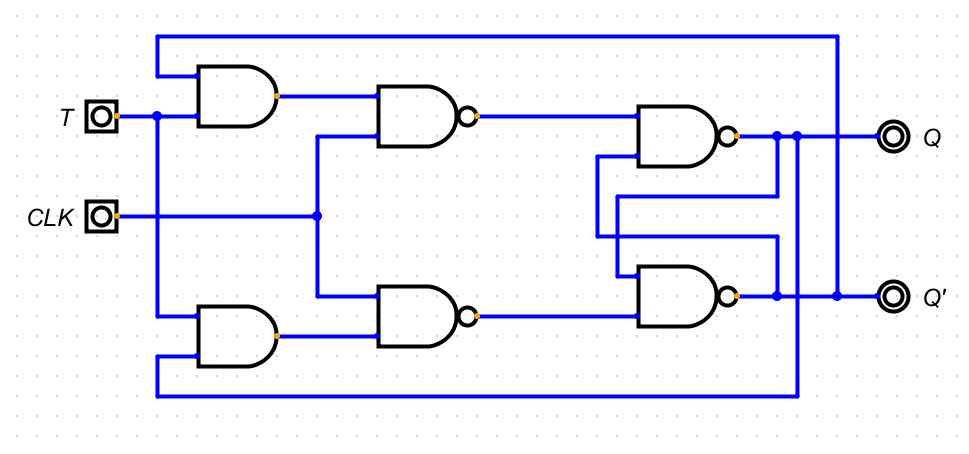

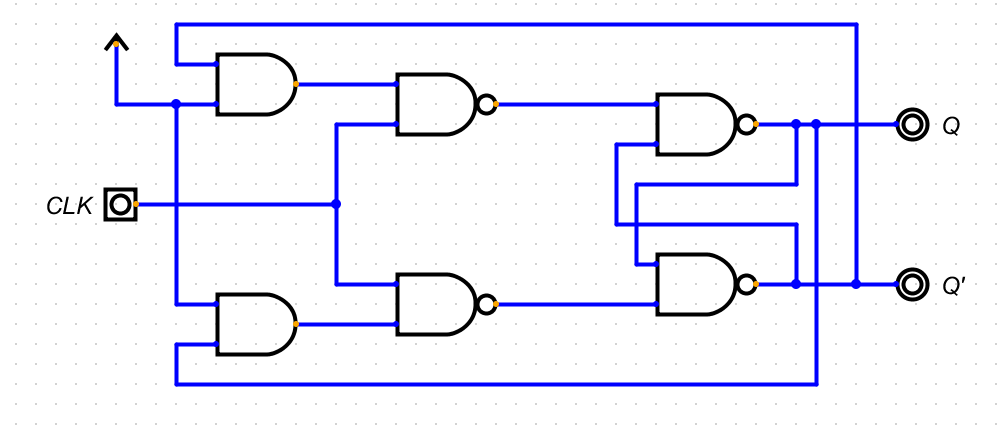

使用Digital软件来绘制T触发器如下所示:

下面尝试运行该电路,初始电路如下所示:

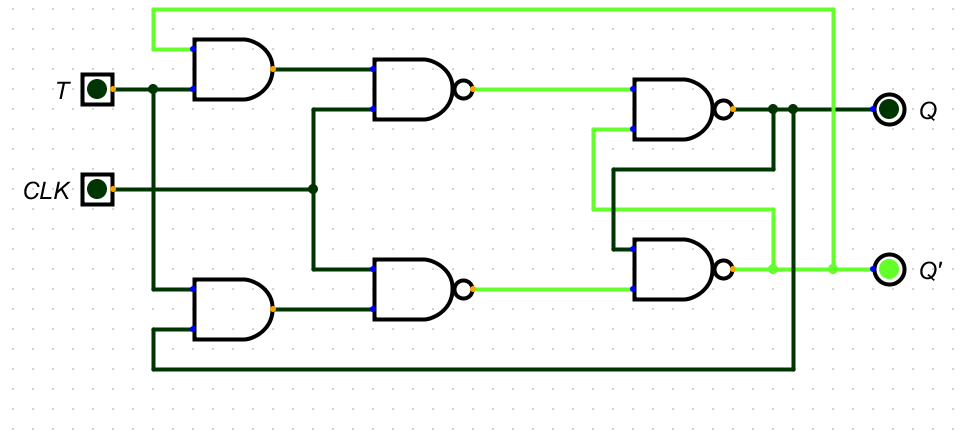

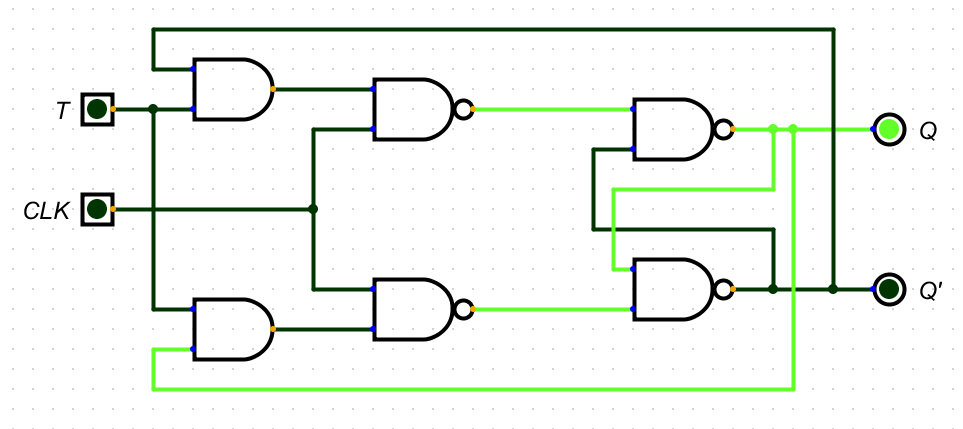

使用单门仿真,将CLK和T全部设置为高电平:

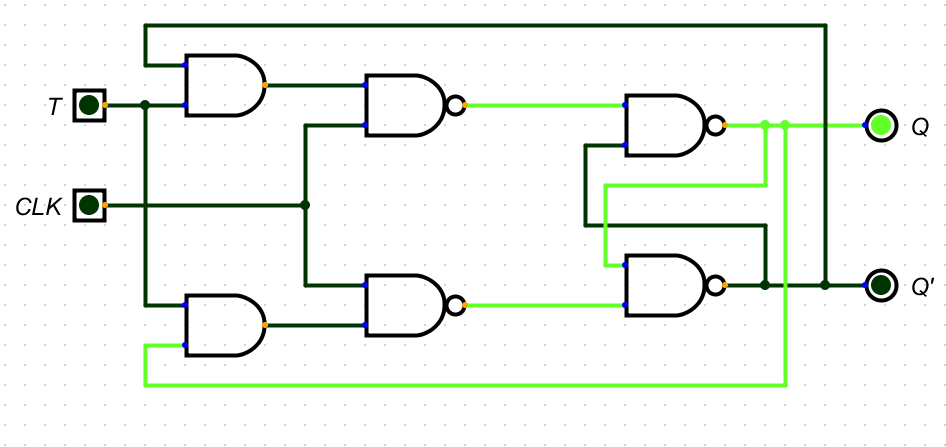

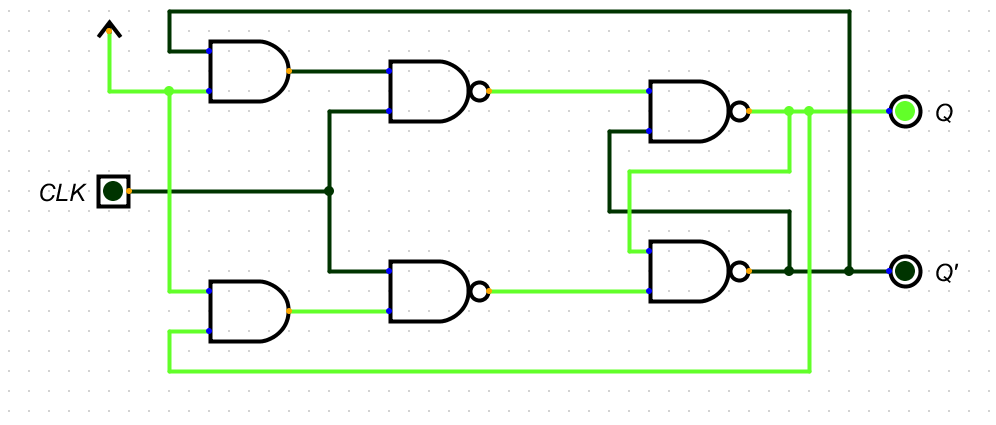

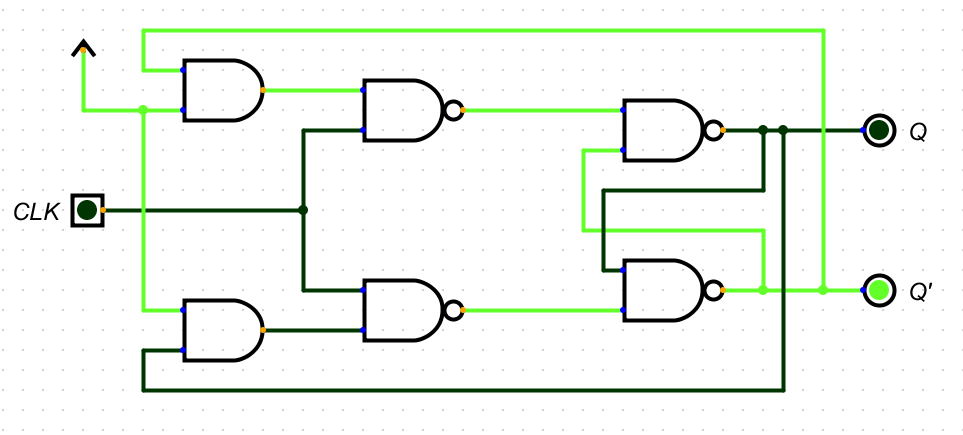

运行该电路如下所示:

可以看到,当T=CLK=1,Q=1时,此时电路输出结果为Q*=0,可以看到此时Q的状态发生了偏转。

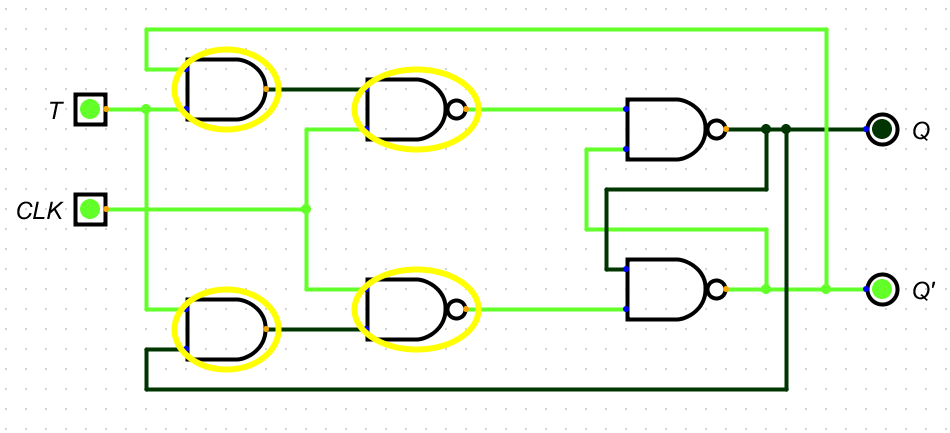

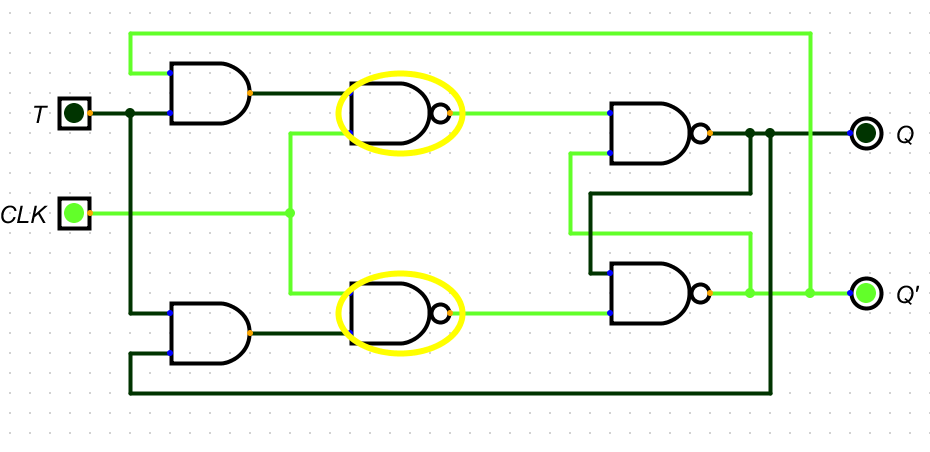

继续将CLK和T全部设置为高电平:

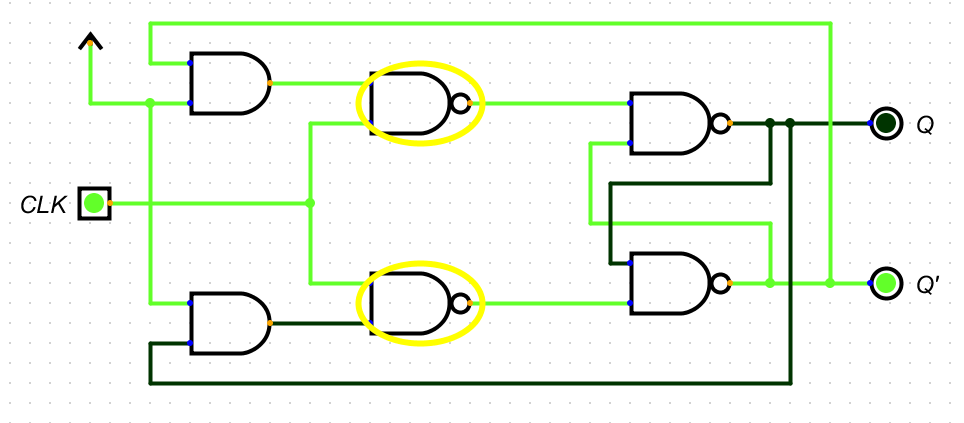

单步运行该电路:

可以看到,当T=CLK=1时,Q=0时,电路的输出结果为1。可以看到此时Q的状态同样发生了翻转。

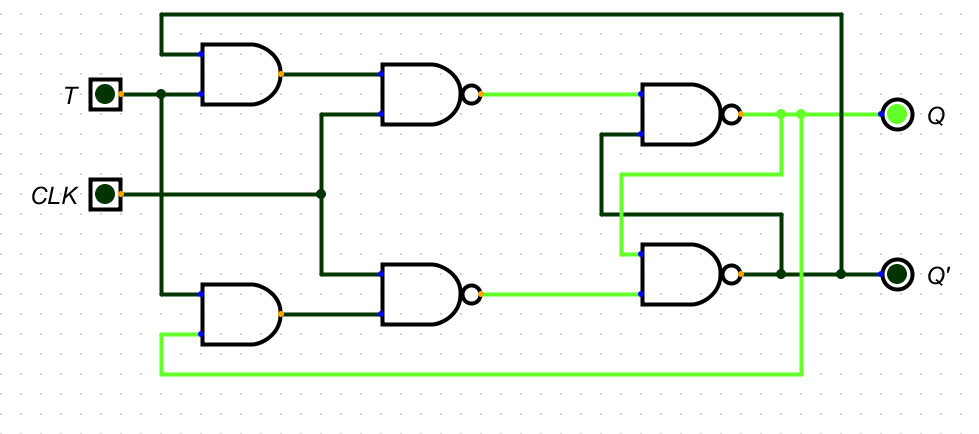

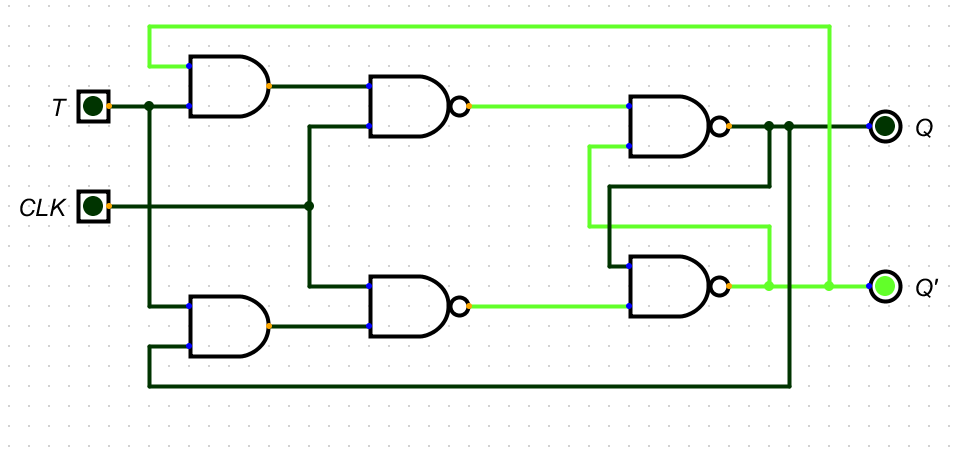

当输入端CLK设置为高电平,输入端T设置为低电平:

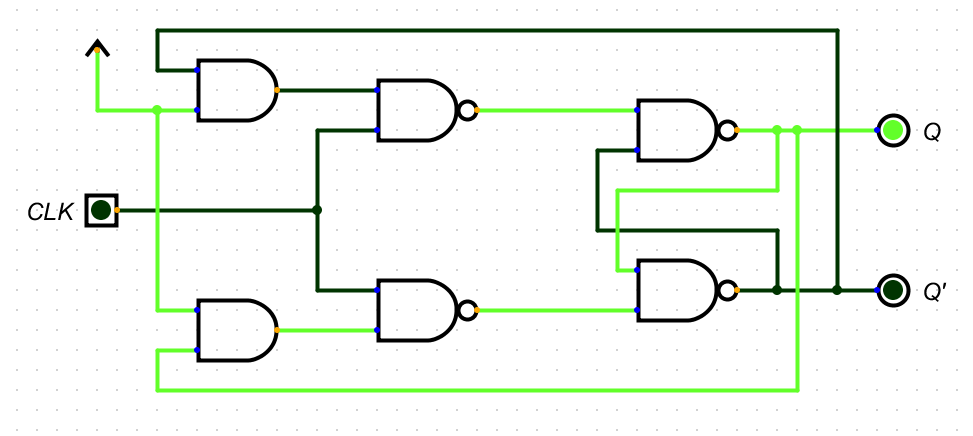

运行该电路如下所示:

可以看到,当CLK=1、T=0、Q=1时,输出端Q*=1。可以看到此时电路是处于输出端的高电平保持状态。

在上面电路的基础上再进行一次翻转操作,之后输入CLK=1、T=0:

运行结果如下所示:

可以看到,无论Q=1还是Q=0,当T=0、CLK=1时,电路的输出均保持不变。

2 T'触发器

2.1 T'触发器简介

T'触发器(T补触发器)是T触发器 的一种改进版本,主要区别在于其触发条件和翻转行为。T触发器在时钟有效边沿(或电平)到来时,若输入 T=1 则输出Q翻转(取反),若 T=0则保持原状态;T'触发器则固定每次时钟有效时都翻转输出(相当于 T恒为1),省去了外部输入控制,适用于固定频率分频或简单计数电路。T'触发器的电路图如下所示:

T'触发器的图形符号如下所示:

2.2 使用Digital软件来绘制T'触发器

使用Digital软件来绘制T'触发器,电路图如下所示:

运行该电路,初始状态如下所示:

使用单门仿真,将CLK设置为高电平:

单步运行该电路:

可以看到Q由原来的高电平变为了低电平。 在此基础上再次使用单门仿真,将CLK设置为高电平:

单步运行该电路:

可以看到电路从低电平再次变为了高电平。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?