贵州大学计算机科学与技术学院《操作系统》第 08 章习题解析

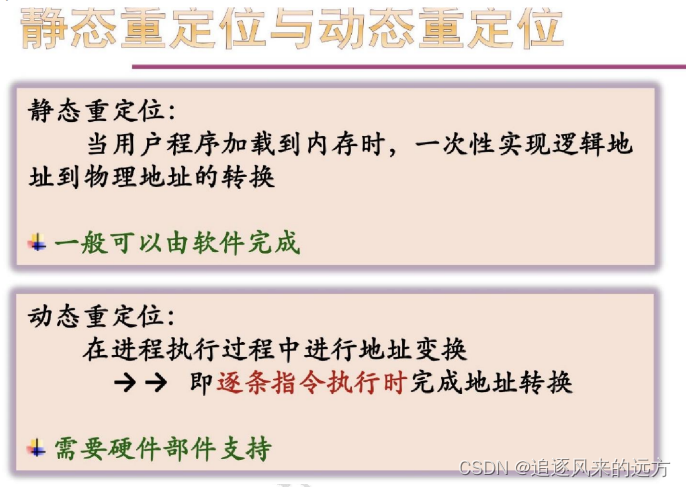

1. 若采用动态地址重定位,其地址重定位工作是在( B )完成的。

A、往内存装载进程时刻

B、执行每一条指令时刻

C、调度程序选中进程时刻

D、在内存中移动进程时刻

【解析】

2. 提出存储层次体系的主要依据是( A )。

A、程序访问的局部性原理

B、多道程序设计技术

C、存储保护技术

D、虚拟存储技术

3. 在虚拟页式存储系统中,若页面尺寸为 4KB,页表项大小为 4B,则采用三级 页表结构可以表示( B )大小的虚拟地址空间。

A、2^48

B、2^42

C、2^32

D、2^45

【解析】 每页可存储页表项的数目:4KB/4B=1K=2^10 个,每页大小:4KB=2^12B

一级页表可表示的虚拟地址空间:2^10*2^12=2^22

二级页表可表示的虚拟地址空间:2^10*2^10*2^12=2^32

三级页表可表示的虚拟地址空间:2^10*2^10*2^10*2^12=2^42

4. 已知系统为 32 位实地址,采用 48 位虚拟地址,页面大小为 4KB,页表项大 小为 8B。假设系统使用纯页式存储,则要采用几级页表,页内偏移多少位? ( B )

A、3,12

B、4,12

C、3,14

D、4,14

【解析】 每页大小:4K=2^12 每页可存储页表项的数目:4K/8=2^12/2^3=2^9 个

一级页表可表示的虚拟地址空间:2^9*2^12=2^21

二级页表可表示的虚拟地址空间:2^9*2^9*2^12=2^30

三级页表可表示的虚拟地址空间:2^9*2^9*2^9*2^12=2^39

四级页表可表示的虚拟地址空间:2^9*2^9*2^9*2^9*2^12=2^48

5. 下列关于快表的叙述中,( B )是错误的。

A、快表的内容是页表的子集

B、快表保存在内存固定位置

C、对快表的查找是按内容并行完成的

D、引入快表可以加快地址转换速度

【解析】 TLB 是一种高速缓存,MMU 使用它来改善虚拟地址到物理地址的转换速度。

6. 在段页式分配中,CPU 每回从内存中取数据,至少需要( C )次访问内存。

A、1

B、2

C、3

D、4

【解析】 第一次访问内存段表、第二次访问段内页表完成地址映射、第三次访问内存中的数据。

7. 操作系统采用分页存储管理方式,要求( A )。

A、每个进程拥有一张页表,且进程的页表驻留在内存中

B、每个进程拥有一张页表,但只要执行进程的页表驻留在内存中

C、所有进程共享一张页表,以节约有限的内存空间,但页表必须驻留在内存中

D、所有进程共享一张页表,只有页表中当前使用的页面必须驻留在内存中

【解析】 在多个进程并发执行时,所有进程的页表大多数驻留在内存中,在系统中只设置一 个页表寄存器 PTR,在其中存放内存中页表的起始地址和页表长度。 平时进程未执行时,页表的起始地址和页表长度存放在本进程的 PCB 中,当调度 到某进程时,才将这两个数据装入页表寄存器中。

8. 下列措施中,能加快虚实地址转换的是( C )。

I .增大快表 (TLB) 容量

II .让页表常驻内存

III .增大交换区 (swap)

A、仅 I

B、仅 II

C、仅 I、II

D、仅 II、III

9. 在采用页式存储管理方案的系统中,若进程处于就绪状态,则页表的起始地址 保存在( A )中。

A、进程控制块 PCB

B、寄存器

C、内存

D、TLB 快表

【解析】 进程执行前会将页表首地址载入 CPU 寄存器,切换时地址寄存器的值将写回 PCB。

10. 下列关于紧缩技术的叙述中,( C )是错误的。

A、紧缩技术可以合并分散的小空闲区,以形成大的空闲区

B、完成紧缩会增加处理器的开销

C、紧缩技术能解决内、外碎片问题

D、紧缩技术可用于可变分区存储管理方案

【解析】 内存紧缩只能处理外碎片问题,内碎片存在于进程内部,为了保证已分配内存块/ 页的大小要求(2 的整数次幂)不能调整。

11. 分区分配内存管理方式的主要保护措施是( A )。

A、界地址保护

B、程序代码保护

C、数据保护

D、栈保护

12. 在一分页存储管理系统中,某作业的页表如下所示。已知页面大小为 1024 字 节,则逻辑地址 2148 对应的物理地址是( D )。

A、2148

B、3059

C、1024

D、1124

【解析】 物理地址的计算公式为:物理地址=块大小(即页大小 L)×块号 f+页内地址 d 。本题中设页号为 p,页内位移为 d,则 p=int(2148/1024)=2,d=2148 mod 1024=100。查页表第 2 页在第 1 块,故物理地址为 1024+100=1124。

13. 假设一个将页表放在内存中的分页系统采用 TLB 以加快地址映射。如果一次内 存访问需要 200ns,75%的页表引用发生在 TLB(假设在 TLB 中查找页表项 占用零时间),则内存的有效访问时间是( D )。

A、300ns

B、400ns

C、200ns

D、250ns

【解析】 有效访问时间 = 0.75*200 ns+0.25*400 ns = 250 ns

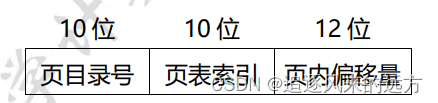

14. 某计算机系统按字节编址,采用二级页表的分页存储管理方式,虚拟地址格式 如下所示:

假定页目录项和页表项均占 4 个字节,则进程的页目录和页表共占( D )页。

A、4

B、10

C、1024

D、1025

【解析】 顶级页目录只会有 1 个页:页内必须连续分配,若超过 1 页,顶级目录将产生分 页,从而需要增加一层页目录。 页表索引所占页数=顶级页目录所包含的最大项数=页大小 212/页表项大小 4=210=1024 个

15. 设有 8 页的逻辑空间,每页有 1024B,它们被映射到 32 块的物理存储区中。 那么,逻辑地址和物理地址的有效位分别为( C )位。

A、10、11

B、12、14

C、13、15

D、14、16

【解析】 本题需要弄清页大小、页号位数、物理块数、页内偏移地址、逻辑地址位数、物理 地址位数之间的联系。

因为 8 页=23 页,所以表示页号的地址有 3 位,又因为每页有 1024B=210B, 所以页内偏移地址有 10 位,所以逻辑地址总共有 13 位;

又因为页面的大小和物理块的大小是一样的,所以每个物理块也是 1024B,而 内存至少有 32 块物理块,所以内存大小至少是 32×1024B=215B,所以物理 地址至少要 15 位,不然无法访问内存的所有区域。

16. 采用分段存储管理的系统中,若段地址用 24 位表示,其中 8 位表示段号,则 允许每段的最大长度是( B )。

A、2^24B

B、2^16B

C、2^8B

D、2^32B

17. 已知系统为 32 位实地址,采用 48 位虚拟地址,页面大小为 4KB,页表项大 小为 8B,每段最大为 4GB。 1)假设系统采用一级页表,TLB 命中率为 98%,TLB 访问时间为 10ns,内存访 问时间为 100ns,并假设当 TLB 访问失败后才开始访问内存,则平均页面访 问时间为(112 )ns。 2)如果是二级页表,则页面平均访问时间为( 114 )ns。 3)若系统采用段页式存储,则每用户最多可以有( 65536 )个段,段内采用 ( 3 )级页表。

【解析】

1)系统进行页面访问操作时,首先读取页面对应的页表项,有 98%的概率可以在 TLB 中直 接读 取到( 10ns), 然后 进行 地址 变换 ,访 问内存 读取 页面 ( 100ns ) , 所 需 要 的 时 间 为 10ns+100ns=110ns 。 如 果 TLB 未 命 中 (10ns),则要通过一次内存访问来读取页表项(100ns),地址变换后,再 访问内存(100ns),因 TLB 访问失败后才开始访问内存,因此所需时间为 10ns+100ns+100ns=210ns。页表平均访问时间为: [98%×110+(1-98%)×210]ns=112ns

2)二级页表的情况下,TLB 命中的访问的访问时间还是 110ns,未命中的访问时间加 上一次内存访问时间(多了一级页表要多访存一次),即 210ns+100ns=310ns, 所以平均访问时间为: [98%×110+(1-98%)×310]ns=114ns

3)系统采用 48 位虚拟地址,虚拟地址空间为 248B,每段最大为 4GB,那么最大 段数=2^48B/4GB=2^16=65536。 4GB=2^32B,即段内地址位数为 32,段内采用多级页表,那么多级页表级数=⌈(32-12)/9⌉=3,故段内采用 3 级页表。

所有资料均来自老师课件!!!

8750

8750

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?