MAX9296

1外设资源

含有2个2X4lane端口(A,B),并且有多个自定义GPIO(MFP0-MFP12)

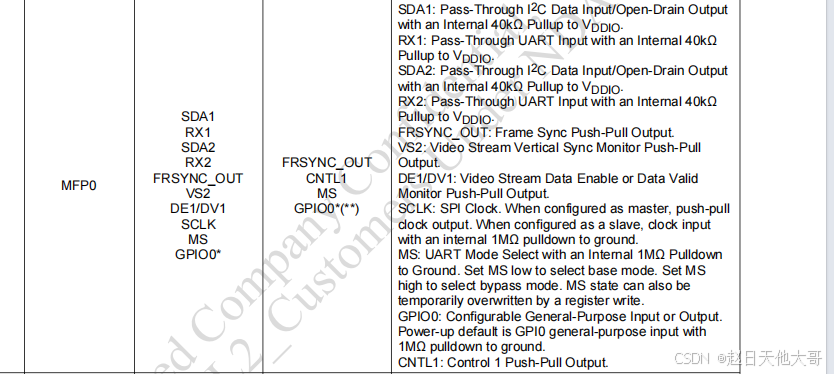

GPIO在不同模式下有不同的复用模式(GMSL2 和GMSL1)以MFP0为例

GMSL2下可以复用成SDA1,RX1,SDA2等等多种模式

PWDNB : 默认为低电平,当电平时,为关机模式,在使用时需要上拉

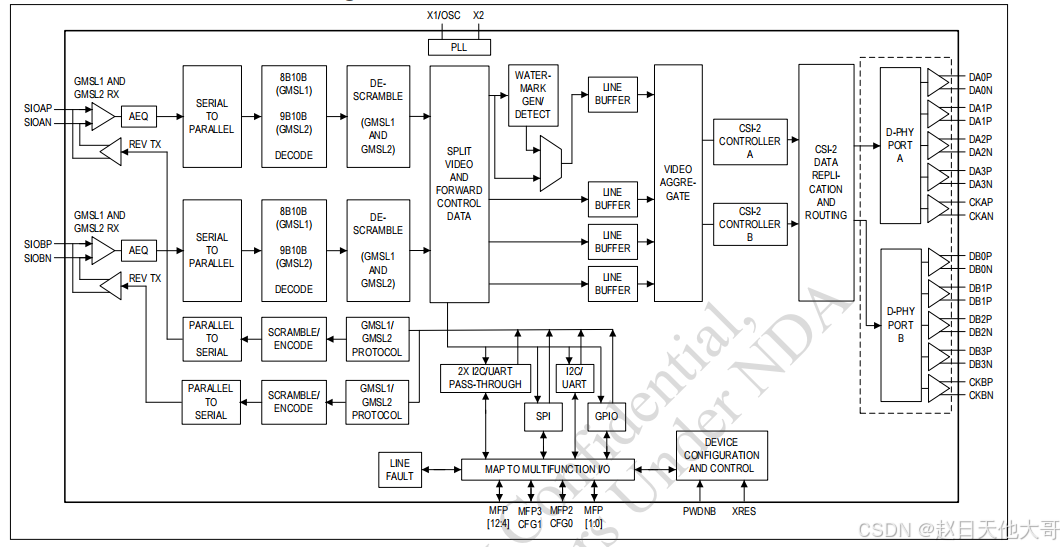

2,板块框图

从上述系统框图,可以看到,MAX9296有两个输入接口SIOAP/N和SIOBP/N,输入由两根差分线接入,经过CMSL2或者CMSL1接入到解除模块,并且,也能通过REV TX将解串器的信息反向发送给串化器。这里反向发送

的信息可以看到时从MFP的引脚映射而来,同样的,串化器的信息也能通过SPLIT VIDEO AND FORWARD CONTROL DATA 中间这个控制模块,解析后,传输到MFP对应的引脚上。

并且,视频输出的数据,也能路由到两个CSI-2mipi控制器上

3,链接方式

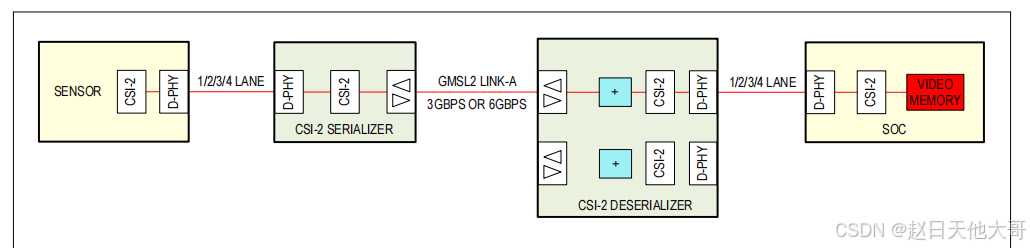

1.单通道链接

图中显示了一个传输视频数据的单个串行链路。正向信道以固定的3Gbps或6Gbps的速率运行。反向通道以固定的187.5Mbps的速率运行。空闲数据包被替换,以填补正向和反向通道中任何未使用的链路带宽。

带宽计算:H x V x fps x bpp x (1+% blanking) x 1.14

H=水平分辨率

V=垂直分辨率

fps =帧每秒

bpp =位每像素

blanking=总水平和垂直消隐

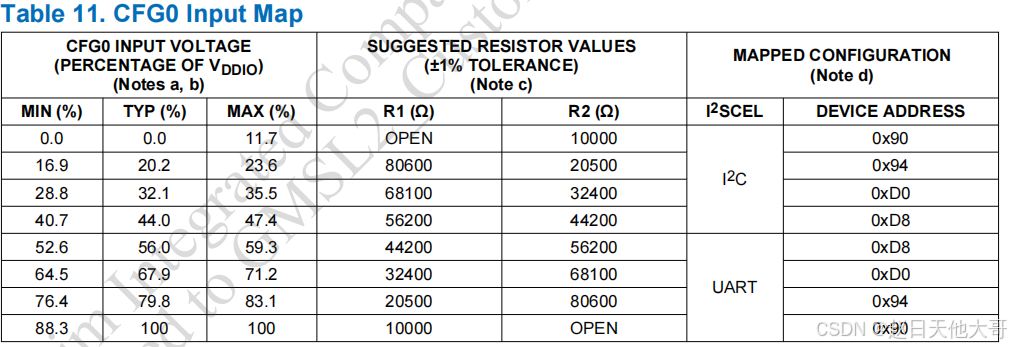

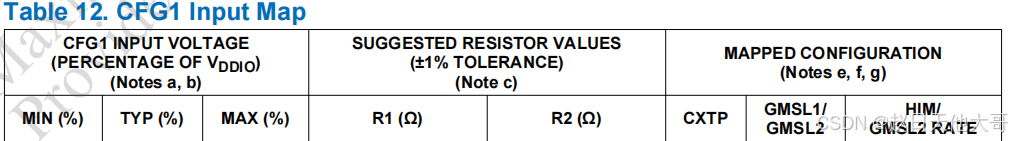

4,模式配置

CFG0为MFP2,CFG1为MFP3

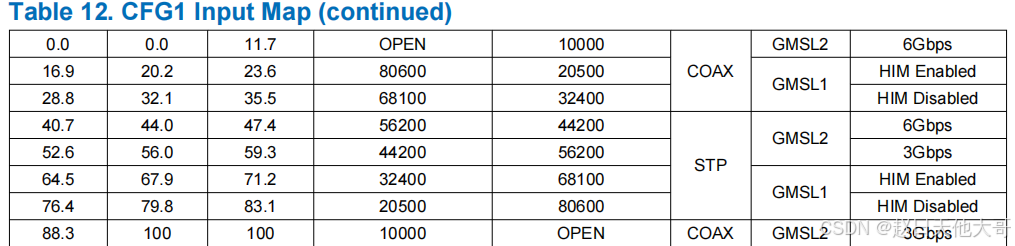

链接的重要顺序

MAX9296有提供VIDEO lock ,视频锁定位表示反序列处理器正在接收有效的视频数据

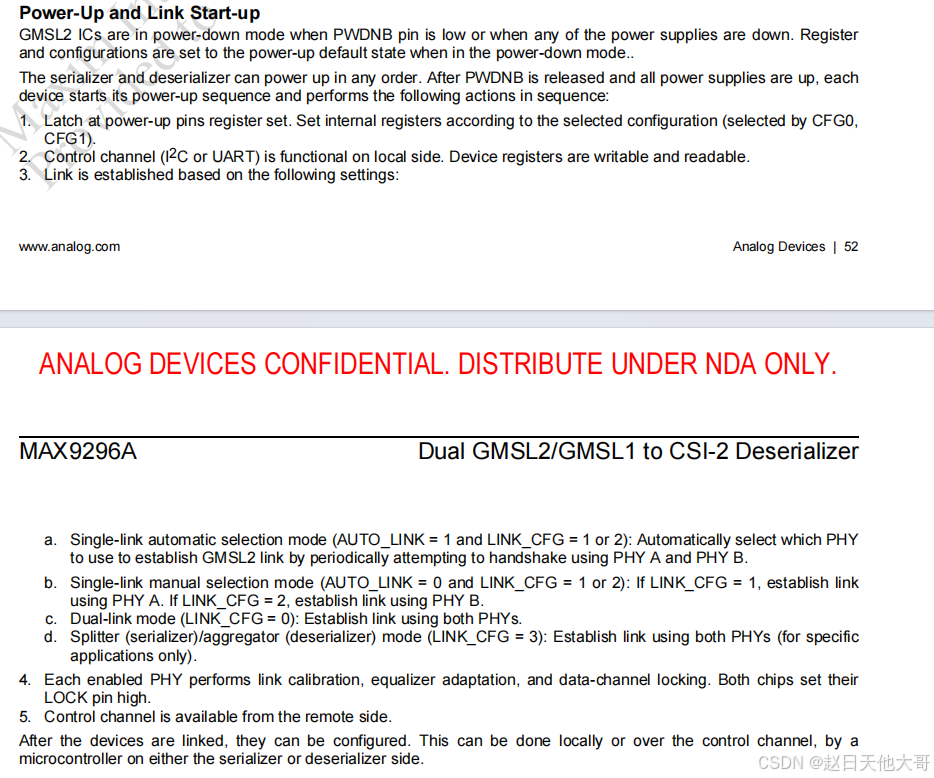

5,输出管道

MAX9296有四个管道,每个管道有256KB的buffer,最大支持8192*24bit像素的每行数据。在接收到数据后,会通过聚合器,把管道的数据传输给csi控制器,最终由D-PHY控制器输出,但是每个D-PHY只能接受一个csi控制器的数据

管道数据有3中模式

模式1:传输固定大小24bpp的数据格式

模式2:输出16bit一下的数据格式(12bit,10bit,8bit),每个像素不够的由0填充

模式3:具有两个不同bpp值的流。一个流的bpp必须是另一个流的bpp的两倍。较高的bpp流最大值为24bpp

CSI-2输出

1.lane配置和数据速率

每个端口支持1、2、3或4个差速器lanes,为了简化PCB的布局,数据通道交换支持独立于使用多少个lane。例如,当该设备被配置为启用一条单一lane时,该lane可以是该端口内可用的四个lane中的任何一个。如果启用了两lane,这两lane可以是端口内的任意两lane。数据lane和时钟lane同时也支持lane内的极性交换。

CSI-2输出端口支持每个通道高达2.5Gbps的数据速率。

2539

2539

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?