1.引言:

如果我们直接控制 STM32 的两个 GPIO 引脚,分别用作 SCL 及 SDA,按照IIC信号的时序要求, 直接像控制 LED 灯那样控制引脚的输出 (若是接收数据时则读取 SDA 电平),就可以实现 I2C 通 讯。同样,假如我们按照 USART 的要求去控制引脚,也能实现 USART 通讯。所以只要遵守协 议,就是标准的通讯,不管您如何实现它,不管是 ST 生产的控制器还是 ATMEL 生产的存储器, 都能按通讯标准交互。

由于直接控制 GPIO 引脚电平产生通讯时序时,需要由 CPU 控制每个时刻的引脚状态,所以称 之为“软件模拟协议”方式。 相对地,还有“硬件协议”方式,STM32 的 I2C 片上外设专门负责实现 I2C 通讯协议,只要配 置好该外设,它就会自动根据协议要求产生通讯信号,收发数据并缓存起来,CPU 只要检测该 外设的状态和访问数据寄存器,就能完成数据收发。这种由硬件外设处理 I2C 协议的方式减轻了 CPU 的工作,且使软件设计更加简单。

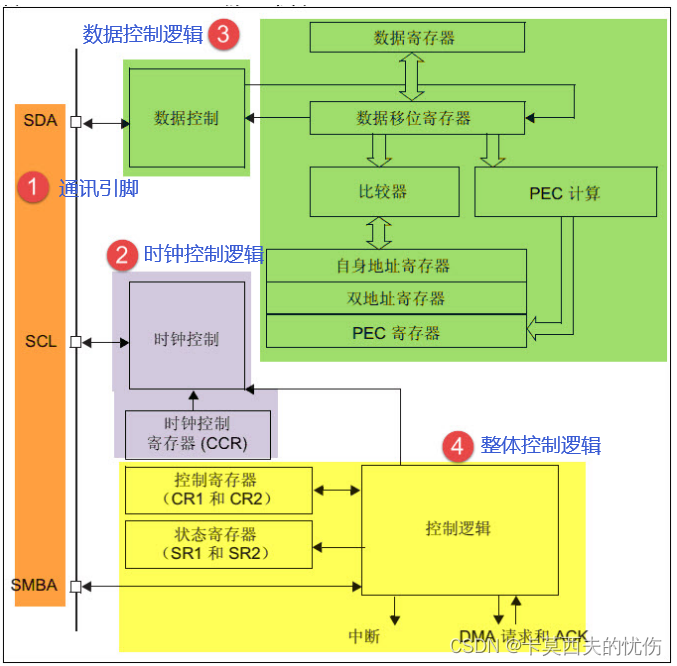

2.stm32的IIC架构剖析:

如下图所示,可以将IIC的架构分为以下四个部分:通讯引脚,时钟控制逻辑,数据控制逻辑,整体控制逻辑。

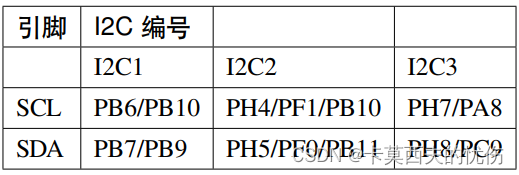

2.1.通讯引脚:

I 2C 的所有硬件架构都是根据图中左侧 SCL 线和 SDA 线展开的 (其中的 SMBA 线用于 SMBUS 的 警告信号,I2C 通讯没有使用)。STM32 芯片有多个 I2C 外设,它们的 I2C 通讯信号引出到不同 的 GPIO 引脚上,使用时必须配置到这些指定的引脚,见表 STM32F4xx 的 I2C 引脚。关于 GPIO 引脚的复用功能,可查阅《STM32F4xx 规格书》,以它为准。

STM32F4xx 的 I2C 引脚为例:

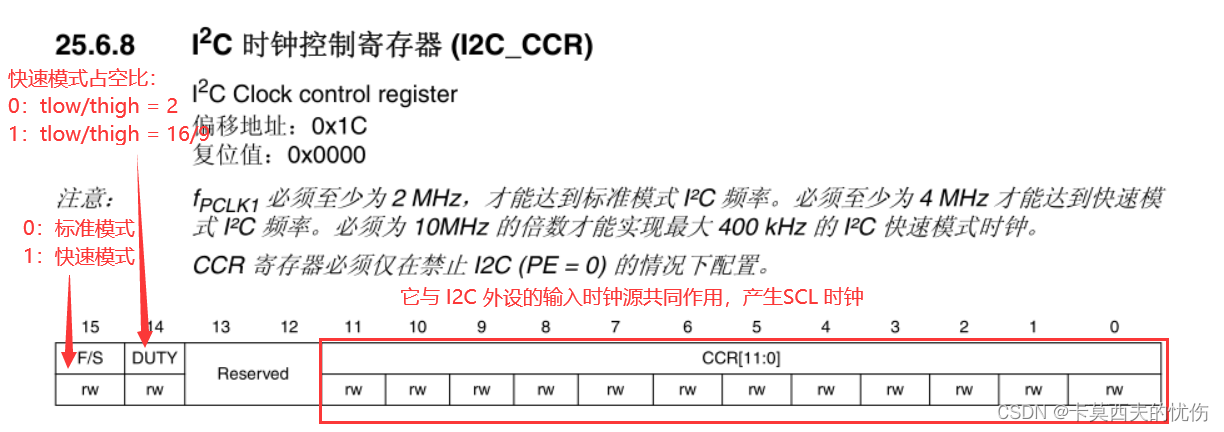

2.2.时钟控制逻辑:

SCL 线的时钟信号,由 I 2C 接口根据时钟控制寄存器 (CCR) 控制,控制的参数主要为时钟频率。 配置 I2C 的 CCR 寄存器可修改通讯速率相关的参数:

• 可选择 I2C 通讯的“标准/快速”模式,这两个模式分别 I2C 对应 100/400Kbit/s 的通讯速率。

• 在快速模式下可选择 SCL 时钟的占空比,可选 Tlow/Thigh=2 或 Tlow/Thigh=16/9 模式,我 们知道 I2C 协议在 SCL 高电平时对 SDA 信号采样,SCL 低电平时 SDA 准备下一个数据, 修改 SCL 的高低电平比会影响数据采样,但其实这两个模式的比例差别并不大,若不是要 求非常严格,这里随便选就可以了。

• CCR 寄存器中还有一个 12 位的配置因子 CCR,它与 I2C 外设的输入时钟源共同作用,产生 SCL 时钟,STM32 的 I2C 外设都挂载在 APB1 总线上,使用 APB1 的时钟源 PCLK1。

SCL 信号线的输出时钟公式如下:

例如,我们的 PCLK1=45MHz,想要配置 400Kbit/s 的速率,计算方式如下:

例如,我们的 PCLK1=45MHz,想要配置 400Kbit/s 的速率,计算方式如下:

PCLK 时钟周期:TPCLK1 = 1/45 000 000(使用 APB1 的时钟源 PCLK1,APB1时钟源45MHZ)

目标 SCL 时钟周期:TSCL = 1/400 000

SCL 时钟周期内的高电平时间:THIGH = TSCL/3

SCL时钟周期内的低电平时间:TLOW = 2*TSCL/3

计算 CCR 的值:CCR = THIGH/TPCLK1 = 37.5

计算结果为小数,而 CCR 寄存器是无法配置小数参数的,所以我们只能把 CCR 取值为 38,这样 I2C 的 SCL 实际频率无法达到 400KHz (约为 394736Hz)。要想它实际频率达到 400KHz,需要修 改 STM32 的系统时钟,把 PCLK1 时钟频率改成 10 的倍数才可以,但修改 PCKL 时钟影响很多 外设,所以一般我们不会修改它。SCL 的实际频率不达到 400KHz,除了通讯稍慢一点以外,不 会对 I2C 的标准通讯造成其它影响。

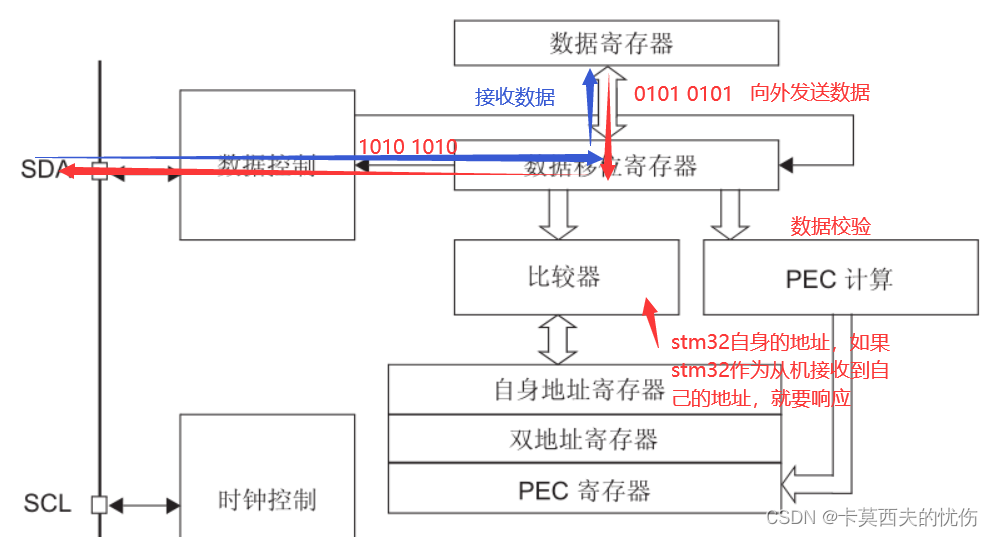

2.3 数据控制逻辑:

2C 的 SDA 信号主要连接到数据移位寄存器上,数据移位寄存器的数据来源及目标是数据寄存 器 (DR)、地址寄存器 (OAR)、PEC 寄存器以及 SDA 数据线。当向外发送数据的时候,数据移位 寄存器以“数据寄存器”为数据源,把数据一位一位地通过 SDA 信号线发送出去;当从外部接收 数据的时候,数据移位寄存器把 SDA 信号线采样到的数据一位一位地存储到“数据寄存器”中。 若使能了数据校验,接收到的数据会经过 PCE 计算器运算,运算结果存储在“PEC 寄存器”中。 当 STM32 的 I2C 工作在从机模式的时候,接收到设备地址信号时,数据移位寄存器会把接收到 的地址与 STM32 的自身的“I2C 地址寄存器”的值作比较,以便响应主机的寻址。STM32 的自 身 I2C 地址可通过修改“自身地址寄存器”修改,支持同时使用两个 I2C 设备地址,两个地址分 别存储在 OAR1 和 OAR2 中。

2.4.整体控制逻 :

整体控制逻辑负责协调整个 I2C 外设,控制逻辑的工作模式根据我们配置的“控制寄存器 (CR1/CR2)”的参数而改变。在外设工作时,控制逻辑会根据外设的工作状态修改“状态寄存 器 (SR1 和 SR2)”,我们只要读取这些寄存器相关的寄存器位,就可以了解 I2C 的工作状态了。除 此之外,控制逻辑还根据要求,负责控制产生 I2C 中断信号、DMA 请求及各种 I2C 的通讯信号 (起始、停止、响应信号等)。

3.IIC通讯过程:

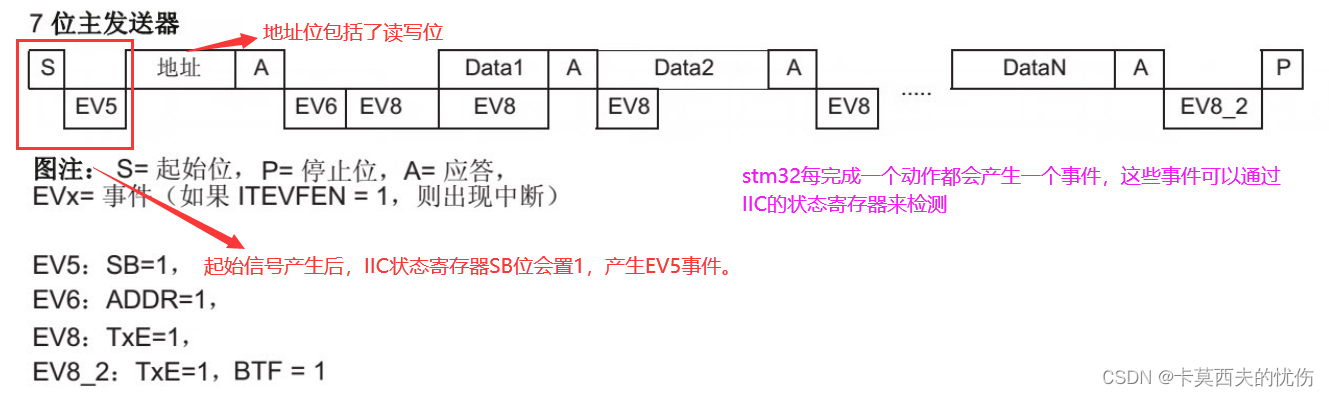

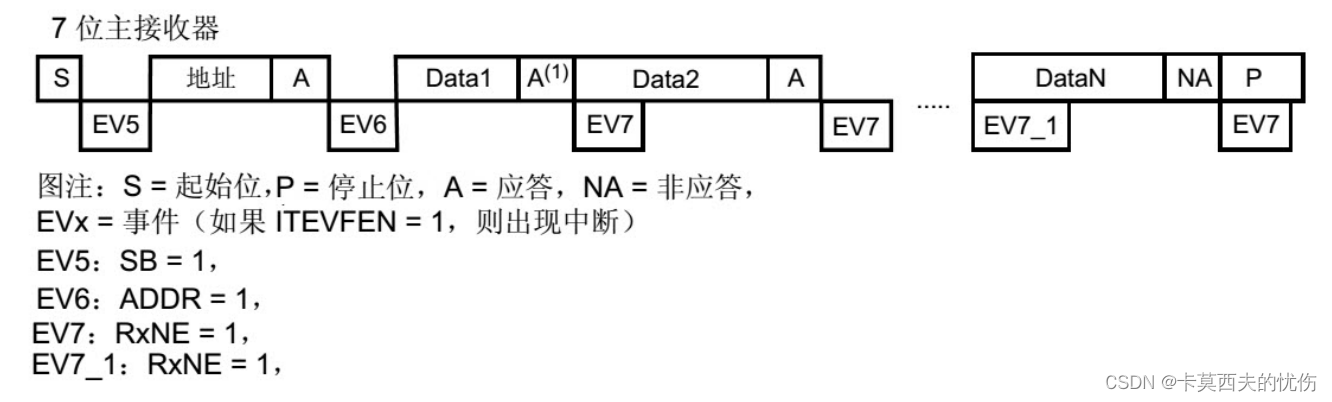

使用 I2C 外设通讯时,在通讯的不同阶段它会对“状态寄存器 (SR1 及 SR2)”的不同数据位写入 参数,我们通过读取这些寄存器标志来了解通讯状态。

3.1主发送器:

图中的是“主发送器”流程,即作为 I2C 通讯的主机端时,向外发送数 据时的过程:

3.2 主接收器:

图中的是“主接收器”流程,即作为 I2C 通讯的主机端时,从外部接收数据的过程:(过程与主发送器类似)

本文详细介绍了STM32通过GPIO实现I2C通信的过程,包括软件模拟协议与硬件协议的区别,以及I2C架构的四个组成部分:通讯引脚、时钟控制、数据控制和整体控制逻辑。重点阐述了I2C时钟生成和数据传输的机制,并展示了主发送器和主接收器的流程。

本文详细介绍了STM32通过GPIO实现I2C通信的过程,包括软件模拟协议与硬件协议的区别,以及I2C架构的四个组成部分:通讯引脚、时钟控制、数据控制和整体控制逻辑。重点阐述了I2C时钟生成和数据传输的机制,并展示了主发送器和主接收器的流程。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?