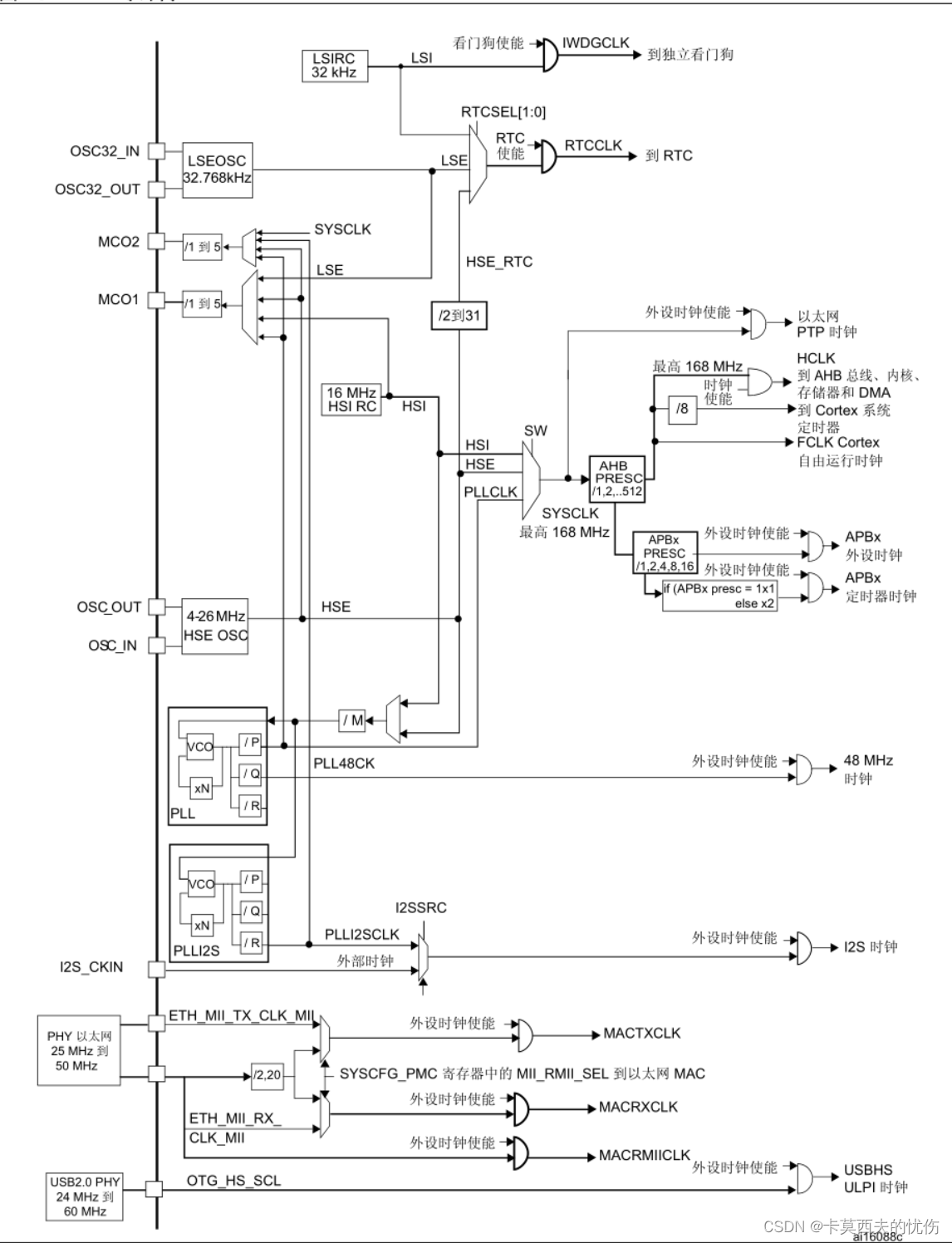

1.RCC时钟数总体框图:

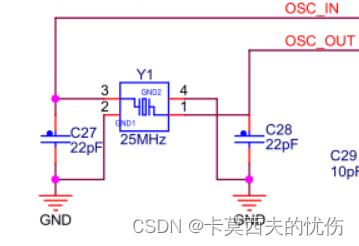

2.HSE 高速外部时钟信号:

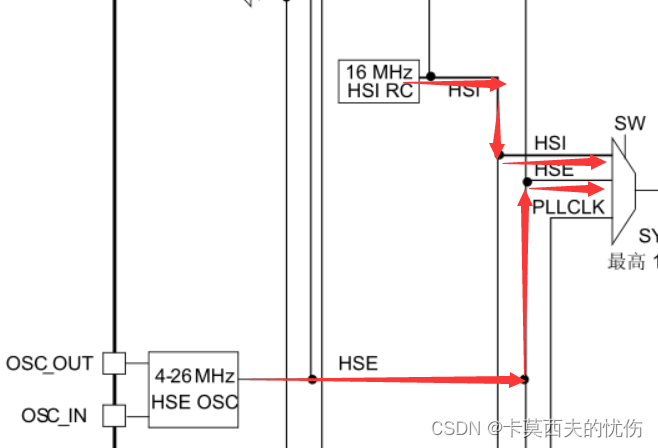

HSE 是高速的外部时钟信号,可以由有源晶振或者无源晶振提供,频率从 4-26MHZ 不等。当 使用有源晶振时,时钟从 OSC_IN 引脚进入,OSC_OUT 引脚悬空,当选用无源晶振时,时钟从 OSC_IN 和 OSC_OUT 进入,并且要配谐振电容。HSE 我们使用 25M 的无源晶振。如果我们使用 HSE 或者 HSE 经过 PLL 倍频之后的时钟作为系统时钟 SYSCLK,当 HSE 故障时候,不仅 HSE 会 被关闭,PLL 也会被关闭,此时高速的内部时钟时钟信号 HSI 会作为备用的系统时钟,直到 HSE 恢复正常,HSI=16M。

3.锁相环 PLL:

PLL 的主要作用是对时钟进行倍频,然后把时钟输出到各个功能部件。PLL 有两个,一个是主 PLL,另外一个是专

本文详细介绍了STM32F429单片机中RCC时钟系统,包括HSE高速外部时钟、HSI内部时钟、PLL锁相环倍频以及系统时钟SYSCLK、AHB和APB总线时钟的配置过程,特别关注了PLL配置的细节和HSE故障下的备用时钟策略。

本文详细介绍了STM32F429单片机中RCC时钟系统,包括HSE高速外部时钟、HSI内部时钟、PLL锁相环倍频以及系统时钟SYSCLK、AHB和APB总线时钟的配置过程,特别关注了PLL配置的细节和HSE故障下的备用时钟策略。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5974

5974

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?