双端口ram 和多模块寄存器

●无冲突读写控制

(1)当两个端口地址不同时,在两个端口上进行读写操作,一定不会发生冲突;

(2)当两个端口地址相同时,在两个端口上不同时进行读写操作,一定不会发生冲突;

(3)当两个端口地址相同时,在两个端口上同时进行读操作,一定不会发生冲突。

●有冲突读写控制

(1)当两个端口地址相同时,在两个端口上同时进行写操作,一定会发生冲突;

(2)当两个端口地址相同时,在两个端口上同时一读一写,一定会发生冲突。

解决办法:设置一个BUSY位,置busy为0,来避免对同一地址存储单元的同时访问。

多体并行存储器

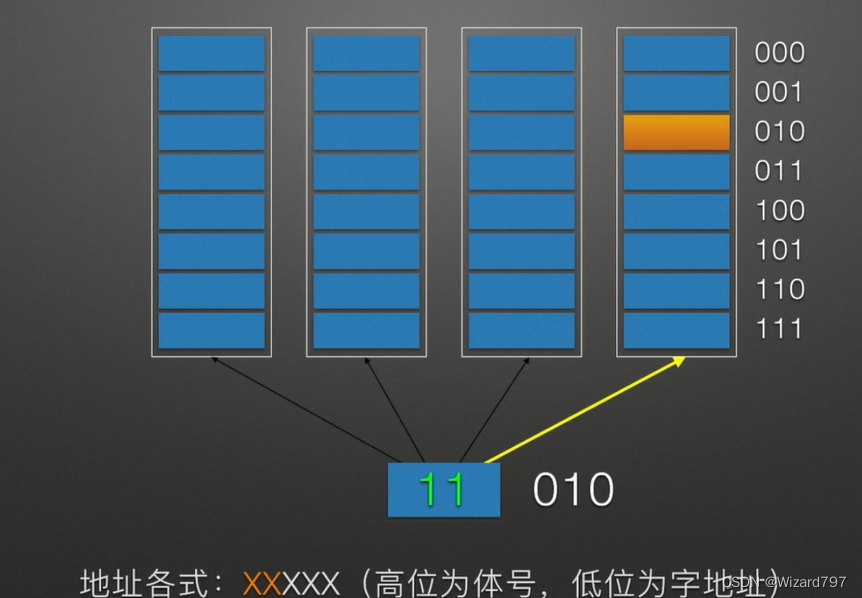

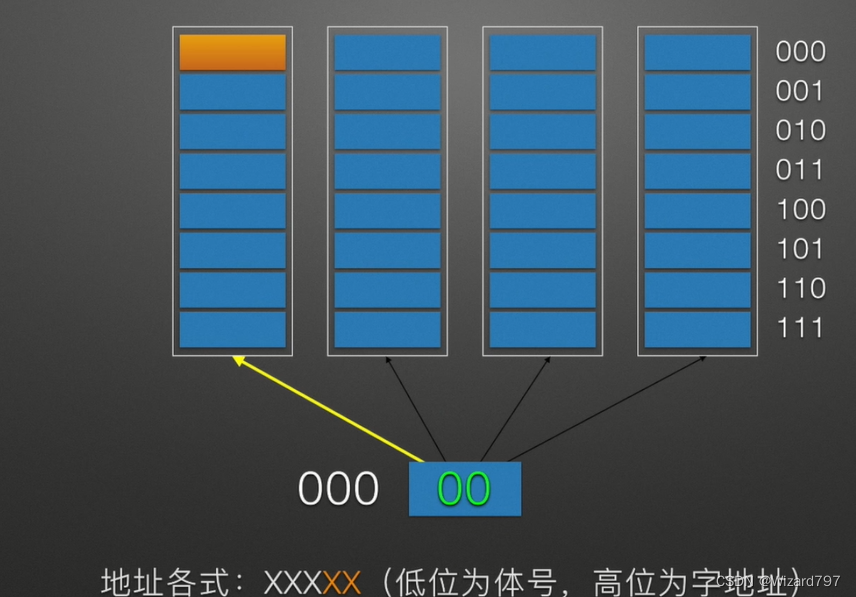

- 高位交叉编制

地位交叉编制

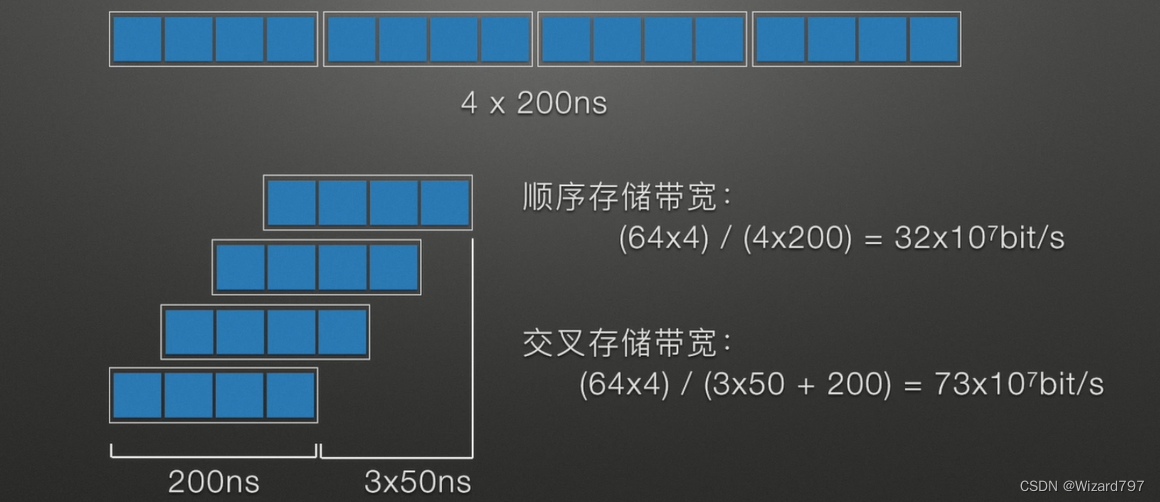

一个存储周期等于4个总线传输周期

例题:有字长为64位的存储器,有4个模块,分别采用顺序方式和交叉方式进行组织,存储周期为200ns,数据总线为64位,总线传输周期为50ns,再连续读出4个字的情况下分别计算顺序存储和交叉存储的带宽。

高位交叉编制为顺序存储

地位交叉编制为交叉存储

程序的局部性访问原理

- 时间局部性

现在正在用的数据,很可能在不久的将来依然要用。 - 空间局部性

现在正在用的数据,很可能与在不久的将来要用到的数据在空间上相邻。

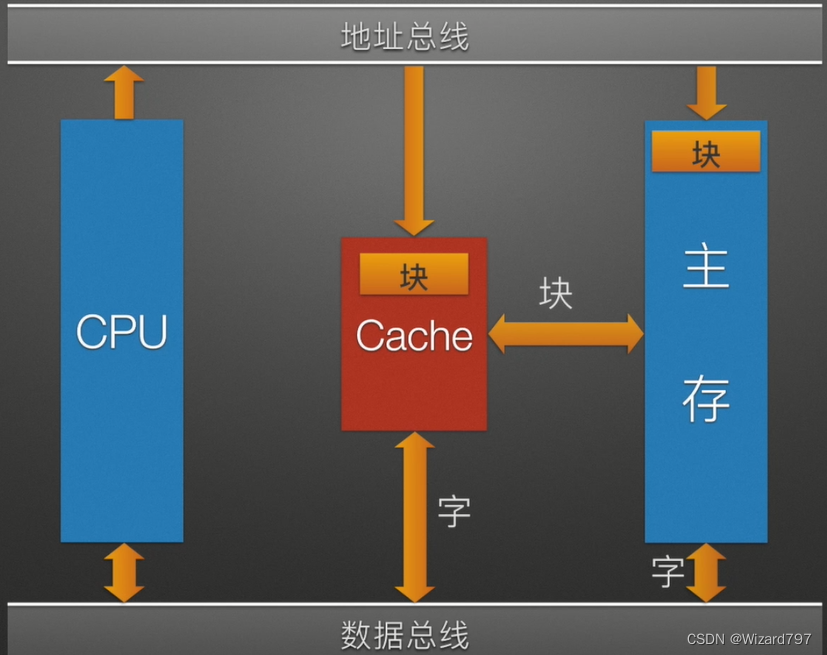

将内存单位的许多字组成一个块

主存-cache

cache的读写操作

- 1.Cache的读操作

当 CPU 发出读请求时,如果 Cache 命中,就直接对 Cache 进行读操作,与主存无关;如果 Cache 不命中,则仍需访问主存,并把该块信息一次从主存调入 Cache 内。- 2.Cache的写操作

当 CPU 发出写请求时,如果 Cache 命中,有可能会遇到 Cache 与主存中的内容不一致的问题,例如,由于 CPU 写 Cache ,把 Cache 某单元中的内容从 X 修改为 X ,而主存对应单元中的内容仍然是 x ,没有改变,所以如果 Cache 命中,需要进行一定的写处理,处理的方法有:写直达法和写回法。

a.写直达法:修改cache后同步在内存中更改数据 保持实时一致性。

b.回写法:出现修改位(脏位)记下cache块内容发生变化 若需要cache位置 给别的cache用时,再将整个cache块写回到主存中去。

补充点:计算机存储不同位字节换算

大多数的现代计算机系统里面,一个字要么是4个字节,要么是8个字节。

①:1字节(byte) = 8位(bit)

②:

在16位的系统中(比如8086微机) 1字 (word)= 2字节(byte)= 16(bit)

在32位的系统中(比如win32) 1字(word)= 4字节(byte)=32(bit)

在64位的系统中(比如win64)1字(word)= 8字节(byte)=64(bit)

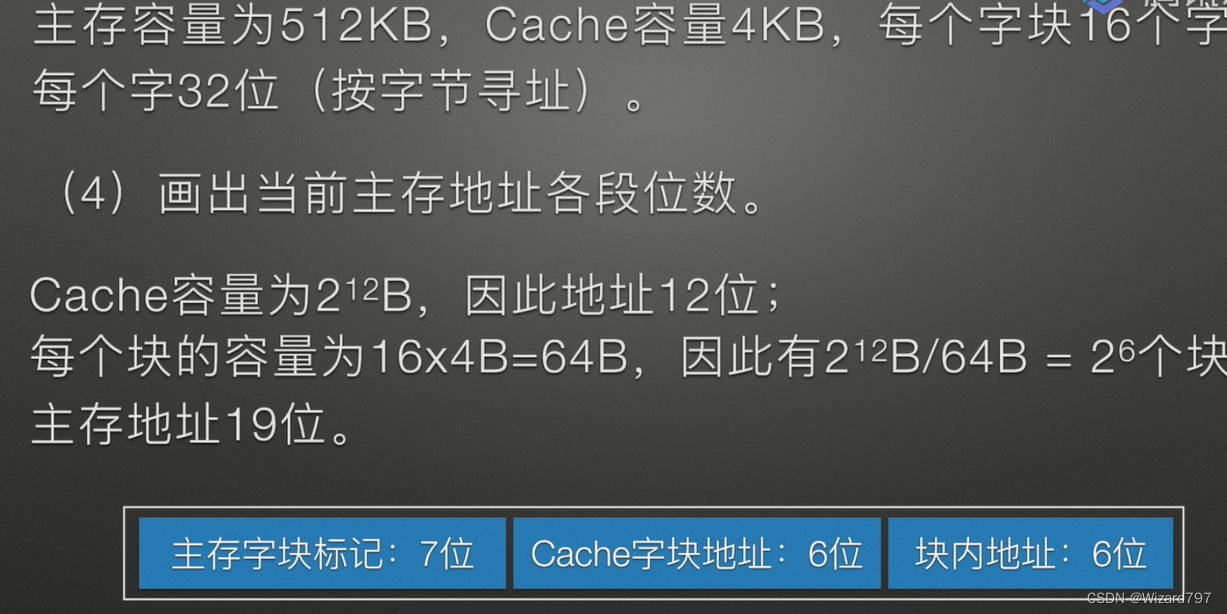

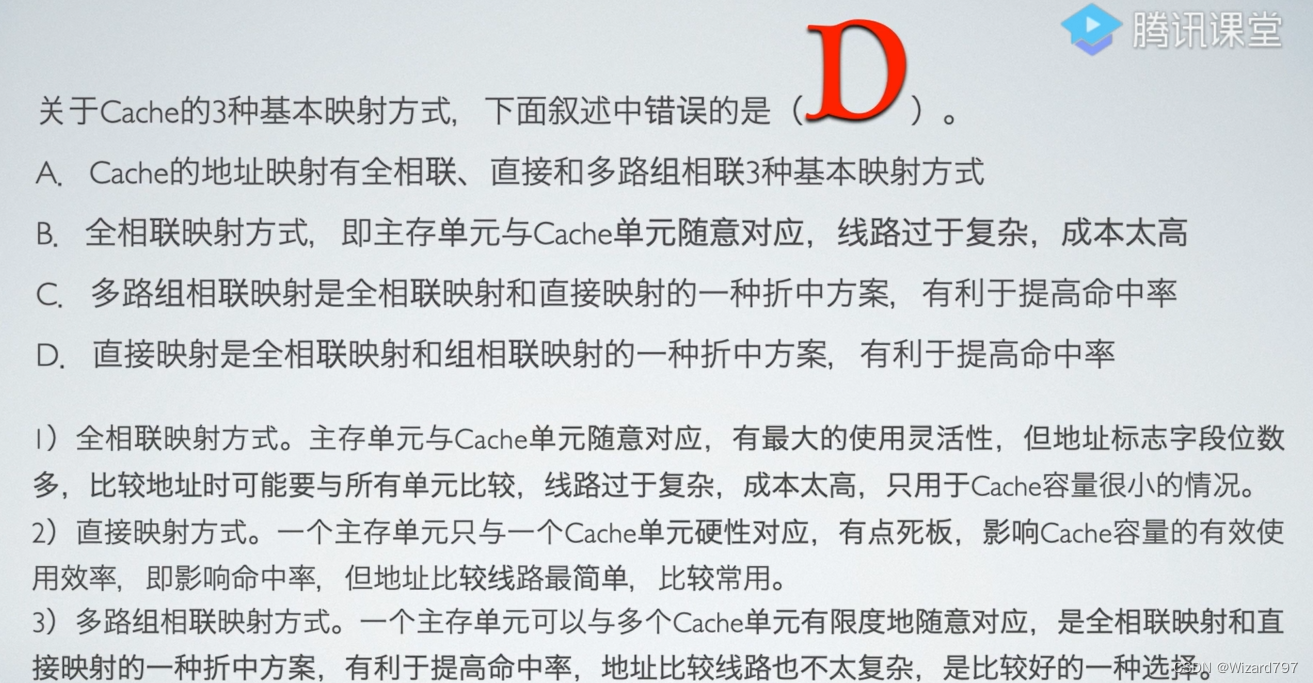

主存-cache地址映射

分为2块为:2^1 位置

分为4块为:2^2 位置

分为m块为:2^m 位

cache 4 x 32B 4个Block,每块32字节 7位地址

memory 16 x 32B 16个Block … 9个地址

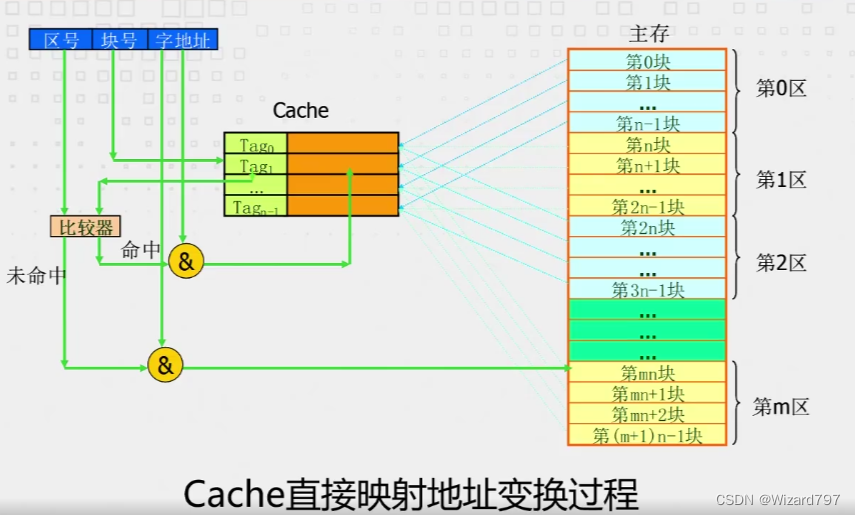

直接映射

内存分区

- 映象规则:

K = l mod 2c

1.式中: K 为 Cache 的块号, I 为主存的块号;2为 Cache 块数。

2.Tag 内容是映射到该位置的主存块的主存地址中的区号,因为比较时只需确定映射的是哪一个区中的块。

地址转换过程:

用程序中给出的主存地址中的块号找到 Cache 中对应的块,读出块的 Tag

标记与主存地址给出的区号进行比较,按照以下几种情况进行判断:

1.如果与主存地址给出的区号相等,且有效位为1,命中。

2.如果区号相等,有效位为0,失效(作废)。

3.区号不相等,有效位为0, Cache 块为空,可以直接装入

4.区号不相等,有效位为1,该块内容有用,写回后,替换。

例题

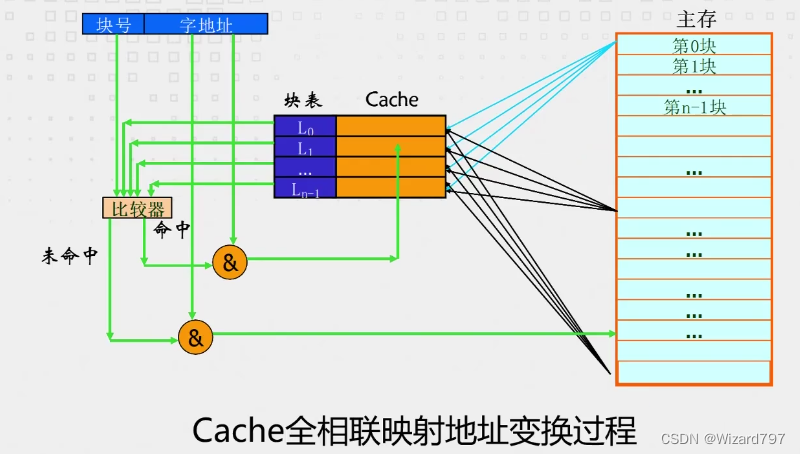

全相联

cache和tag内容

- 主存中与cache数据块对应的数据块的快地址

- 标记位数 = 主存块号位数

- 地址转换过程:

1.因为全相联映射的主存块可能映射在任何 Cache 块内,所以根据主存块号与所有 Cache 块的标记进行比较,有相等的,说明命中,读出 Cache 块号访问 Cache 。

2.需要一个目录表来存放映射关系,目录表容量为 Cache 的块数,字长等于 Cache 块的标记、 Cache 块号、有效位之和。

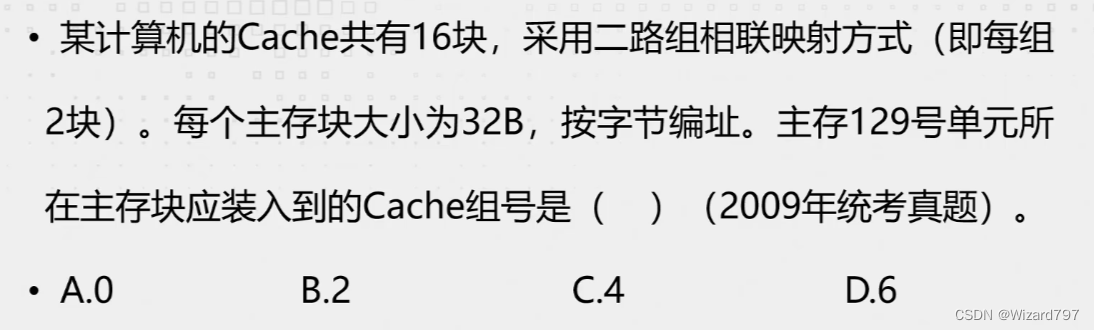

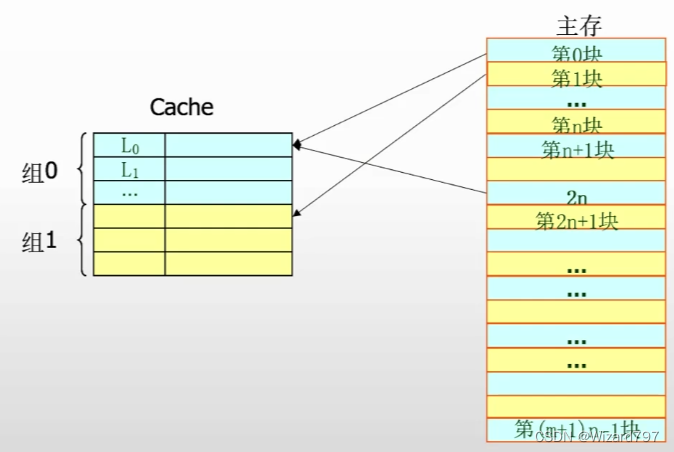

组相连

- 映像规则:

将 Cache 空间分成大小相同的组,让主存中的一块直接映像装入 Cache 中对应组的任何一块位置上,即主存的块对应 Cache 的组,采用直接映像, Cache 组内采用全相联映像

J =I mod Q

J 为 Cache 的组号,I为主存的块号, Q 为 Cache 的组数

假如每个组内有2^r 块,cache和主存地址相差t位,则标记区t+r位

- 地址映像

Tag 内容是主存区号 E 和组内块号 B ,因为某一个 Cache 块中的内容可能来自任何一个区,确定了区号后,区内组号是一定的,(因为组到组是直接映像)还需要确定是组内哪一块(因为组内是全相联映像)

例题:

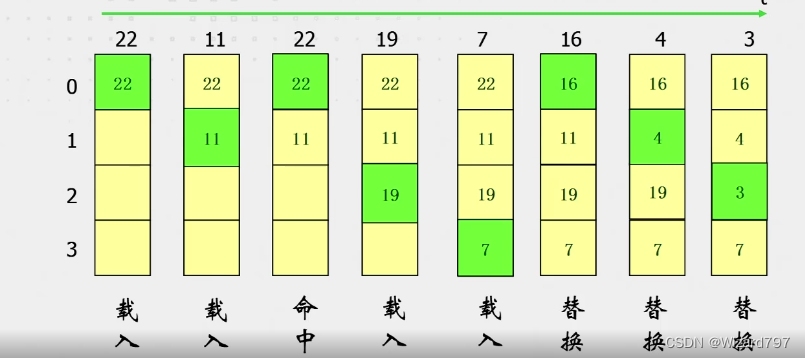

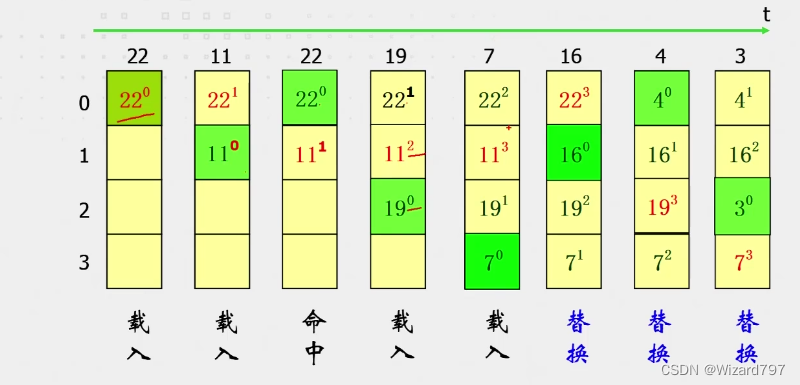

替换算法

1.先进先出算法

2.最近最少使用(LUR)算法

3. 更新策略

1.写 Cache 命中时,如何保持 Cache 与主存中的内容一致?

- (1)写直达法:每次信息从 CPU 写入 Cache 单元中时,也要写回相应的物理内存单元中。

- (2)写回法:即数据暂写入 Cache ,并用标志将该块注明,等需要将该块替换回到主存时,才写回主存,也称标志交换方式。

2.写 Cache 不命中时

- (1)按写分配法:把信息写人主存,同时将将该块信息装入 Cache 。

- (2)不按与分配法:直接更新物内存种种的值,而不把值装入 Cache

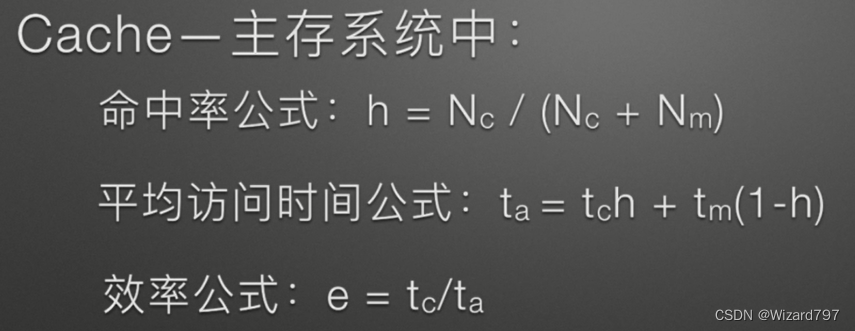

cache 性能评价

- 命中率问题

说明:对于 CPU 执行一段程序时的访存操作, N 。为命中 Cache 的次数, Nm 为直接访问主存的次数, h 为命中率, to 为 Cache 存储周期(一次访问 Cache 所需时间), th 为主存存储周期, ta 为平均访存时间, e 为访存效率。

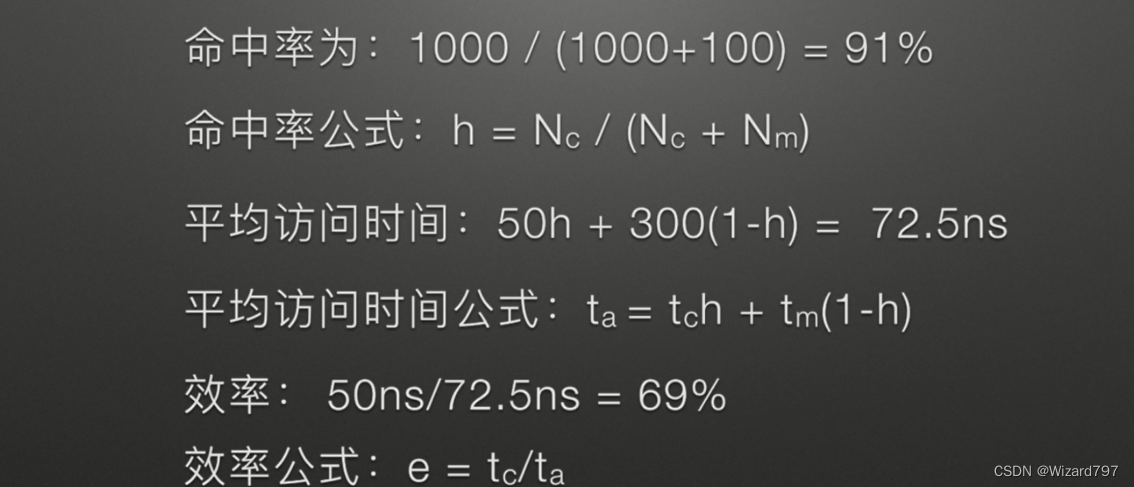

例题1:

CPU执行某程序时共访问Cache命中1000次,直接访问主存100次,Cache的存储周期为50ns,主存的存储周期为300ns ,求Cache——主存系统的命中率,效率和平均访问时间。

例题2:

2810

2810

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?