一、简介

DVI接口最高的传输速率可达8G/s,分辨率高达1920*1080,但是DVI只能用于传输视频信号,无法和HDMI信号一样同时传输视频和音频信号。

DVI接口支持:

a) 内容从创建到消费都保持在无损数字领域。

b) 显示器技术的独立性。

c) 通过热插拔检测、EDID和DDC2B,即插即用。

d) 在单个连接器中支持数字和模拟功能。

1. 分类

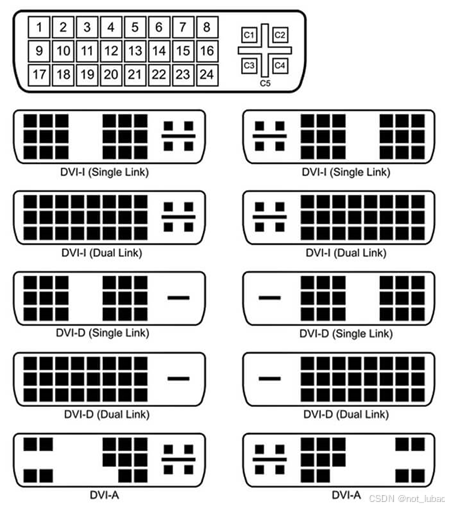

有多种规范,常见的有DVI-A、DVI-D和DVI-I。

1.1 DVI-A(模拟)接口

DVI-A(A=Analog)用于传输模拟信号,可以理解为假DVI接口,DVI-A因为传输的是模拟信号,因此无法体现数字信号的优势。下图为DVI-A实物图:

1.2 DVI-D接口

DVI-D(D=Digital)是数字信号接口,是真正意义上的数字信号接口,其主要的不足是无法兼容VGA。下图为Dual Link实物图:

DVI-D可分为DVI-D(Single Link)和DVI-D(Dual Link)。其主要的区别在于DVI-D(Single Link)比DVI-D(dual Link)少了四组差分信号(D4-和D4、D3-和D3、D5-和D5),其余信号均相同。

1.3 DVI-I接口

DVI-I(I=A+D=Integrated)是集成DVI-A和DVI-D的混合接口,在引脚定义上有明显的区分。

DVI-I可分为DVI-I(Single Link)和DVI-I(Dual Link)。其主要的区别在于DVI-I (Single Link)比DVI-I (dual Link)少了四组差分信号(D4-和D4、D3-和D3、D5-和D5),其余信号均相同。

1.4 带宽

| 类型 | 通道 | 引脚个数 | 最大带宽 | 支持最大分辨率 |

| DVI-A(VGA) | 2048*1536@60Hz | |||

| DVI-I | 单通道 | 18+5 | 168MHz | 1920*1200@60Hz |

| DVI-I | 双通道 | 24+5 | 2*168MHz | 2560*1600@60Hz,1920*1200@120Hz |

| DVI-D | 单通道 | 18+1 | 1920*1200@60Hz | |

| DVI-D | 双通道 | 24+1 | 2560*1600@60Hz,1920*1080@120Hz |

备注:

当DVI-I接VGA时,就是起到了DVI-A的作用。

当DVI-I接DVI-D时,只起了DVI-D的作用。

2. 管脚

包含了6对数据、1对时钟、4根屏蔽线、电源(+5V和GND)、HPD(热拔插检测)、 DDC通道、C1~C5。

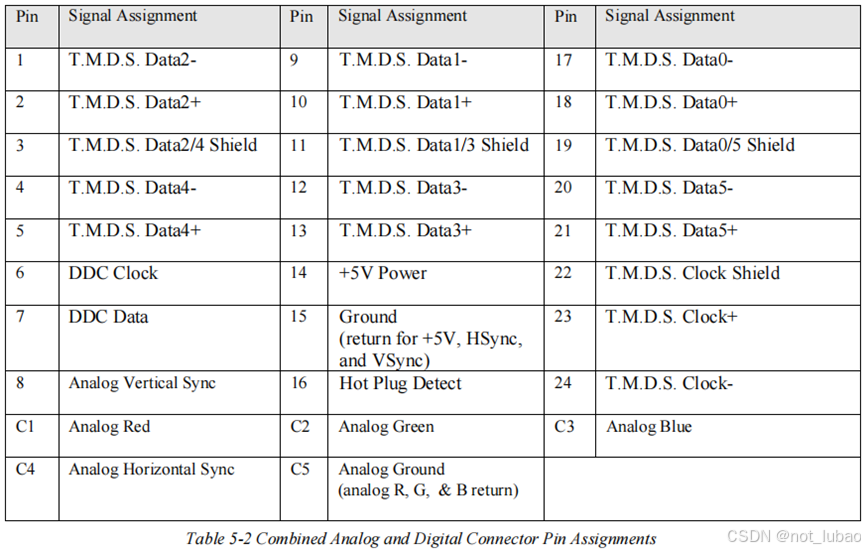

前面的信号与HDMI类似,下面详细说明一下C1~C5的功能:

C1(Analog Red)模拟视频信号 三基色信号线中的红

C2(Analog Green)模拟视频信号 三基色信号线中的绿

C3(Analog Blue)模拟视频信号 三基色信号线中的蓝

C4(Analog Horizontal)sync 模拟视频信号(水平扫描)行同步信号

PIN8(Analog Vertical)sync 模拟视频信号(垂直扫描)场同步信号

C5(Analog Ground)模拟视频信号地线

二、 官方技术手册阅读笔记

1. 介绍

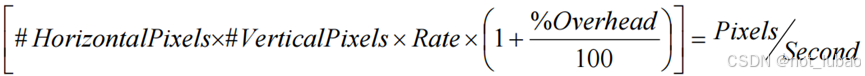

1.1 带宽估计

在物理介质上所需的带宽很容易估计。作为输入所需要的数据包括水平像素、垂直像素、刷新频率(Hz)、带宽消耗(大致定义为消隐,即非实际显示的)。快速估计所需带宽的一个方程式为:

其中,带宽消耗定义为:

为了测量以每秒像素为单位的电路带宽,假设三个通道都在同时传输R-pel、G-pel和B-pel数据。pel是一个像素元素,即一个RGB像素的独有的红色值或绿色值或蓝色值。通过将每秒像素的数值乘以每像素的比特数,可以将每秒像素转换为每秒比特。使用上述公式和TMDS信令协议,每秒的像素等于TMDS时钟链路的频率。(Transition Minimized Differential Signaling,最小化传输差分信号)

2. 结构要求

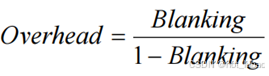

2.1 TMDS概述

DVI使用过渡最小化的差分信号的基础电气互连。使用的TMDS连接用于将图形数据发送到显示设备。转换最小化是通过实现一种先进的编码算法来实现的,该算法将8位数据转换为一个10位的直流平衡字符。可以选择使用一个还是两个TMDS连接,这取决于像素格式和所需的时间。这两个TMDS连接共享相同的时钟,允许带宽在两个链路之间平均分配。当确定了显示设备的功能后,系统将选择启用一个或两个TMDS连接。

2.2 即插即用规范

2.2.1 概述

在系统初始启动时,图形控制器可能会假定存在一个符合VGA标准的设备。为了适应系统引导模式和调试模式,DVI兼容的显示器必须支持第2.2.4.2节中定义的低像素格式模式。BIOS POST和操作系统很可能会使用DDC2B协议查询显示器,以确定支持的像素格式和接口。DVI使用EDID数据结构来识别显示器类型和功能。显示器支持的像素格式、图形子系统支持的像素格式以及用户输入的组合将确定要显示的像素格式。

DVI提供了单链接或双链接实现。单链接可以在减少空白间隔的情况下支持超高清电视(HDTV)像素格式。双链接配置旨在支持不支持减少空白的显示器对更高带宽的需求。双链接配置将支持大像素格式的数字阴极射线管(CRT);双链接不仅限于大像素格式的数字CRT支持。数字CRT预计与传统CRT类似,只是显示传感器接收的图形数据处于数字领域,最终的数字到模拟转换发生在监视器中。数字CRT需要分配时间给水平和垂直回跳间隔。为了使CRT显示与减少空白的平板显示器相同的像素格式,回跳时间分配对图形子系统提出了高峰值带宽要求。数字CRT的更高带宽要求是通过使用两个TMDS链路实现的。通过使用第二个链接和今天的技术发射机,符合VESA(Video Electronics Standards Association)的广义定时公式(GTF)的数字CRT可以以85Hz的刷新率支持超过275万像素的像素格式。支持减少空白和刷新率的显示设备可以轻松支持两个TMDS链路的超过500万像素。

在系统初始启动时,如果检测到数字显示器,只能激活主TMDS链路。只有在图形控制器驱动程序确定监视器存在第二链接的能力后,才能激活辅助TMDS链路。这两个TMDS链路共享相同的时钟,使得带宽可以均匀分配给两个链接。如果将模拟 DVI 兼容监视器连接到系统,则系统应将模拟DVI兼容监视器视为连接到15针VGA连接器的模拟监视器一样对待。

如果在启动过程中不存在DVI兼容监视器,存在热插拔检测机制,允许系统确定何时插入了一个DVI兼容监视器。在热插拔事件之后,系统将使用DDC2B接口查询监视器,并在需要时启用TMDS链路。在确定像素格式和时序之后,还有两个参数会影响用户对图片质量的感知,即伽马(gamma)和缩放。

显示器的伽马特性取决于显示技术。过去,曾假定CRT是主要的显示技术。现在,为了确保显示独立性,不假定显示技术。DVI要求在接口处对数据进行伽马特性的定义,从而使不同显示技术的显示器能够补偿其特定的显示传递特性。

如果在EDID数据结构中将显示器标识为支持多个像素格式的固定像素格式设备,则假定存在监视器标量。监视器标量允许监视器制造商确保显示图像的质量。有关缩放和EDID要求的完整详细信息,请参阅本规范后面的各自章节。

2.2.2 TMDS连接使用模型

2.2.2.1TMDS链接系统的要求

一个符合DVI标准的系统必须至少实现一个TMDS链接,即链接#0。必须支持最低像素格式模式。支持的最大像素格式的实现是特定的。如果系统支持需要大于165MHz的像素格式和时序,那么第二个TMDS链接就需要使用。没有指定的双链路实现的最大值。

也就是第一个连接线路的最大像素时钟是165MHz,更大就需要使用第二个连接。

一个支持双TMDS的系统链路必须能够在支持的像素格式之间动态切换,包括在需要单链路和双链路配置的像素格式之间切换。当一个双TMDS支持链路的系统只驱动一个链路,辅助链路必须不在工作。

2.2.2.2TMDS链接监控器的要求

一个符合DVI标准的监视器必须至少实现一个TMDS链接,即链接#0。必须支持最低像素格式模式。支持的最大像素格式是特定于实现的。如果系统支持需要大于165MHz的像素格式和时序,那么第二个TMDS链接就需要使用。

一个双链路TMDS监视器必须能够检测每个链路的活动,并在受支持的像素格式之间进行动态切换,包括在需要单链路和双链路配置的像素格式之间进行切换。

2.2.3 高颜色深度支撑

允许每像素大于24位的颜色深度,但需要通过第二个链路支持。每个像素的颜色在逻辑上与主TMDS链路(#0)上提供的最重要的位相连接链路和在辅助TMDS链接(#1)上提供的最不重要的位链接。如果实现,则使用辅助TMDS链接上的数据格式必须使用与为主链接定义的相同的24位MSB对齐的RGB TFT数据格式。

TFT-LCD(Thin film transistor liquid crystal display,薄膜晶体管液晶显示器)可能是RGB565,而不是RGB888。对齐方式为:R、G、B各自的最高位对齐,低位空置。

16bit数据接入24bit接口时,空置接口生成比特流会报错,在约束文件中加入以下代码即可。

在启用高色深度之前,系统必须识别监视器中存在的功能。如果显示器不支持高颜色深度,系统必须能够以所需的24位格式操作。

2.2.4 低像素格式的支持

支持低像素格式的模式,以允许一个默认的操作模式。此默认操作模式使用户能够查看BIOS消息和进展以及操作系统初始加载消息。保持清晰的图像,不需要将图像缩放到全屏或居中。

一旦操作系统加载了图形控制器驱动程序,驱动程序就可以切换到不同的像素格式和定时模式。视频BIOS需要响应所有遗留的VESA BIOS调用和INT 10 BIOS(IBM PS/2 Legacy BIOS)调用,但是硬件模拟遗留模式是可以接受的。

2.2.4.1 系统低像素格式的支持要求

640x480像素格式,60 Hz刷新,像素时钟为25.175 MHz,水平频率为31.5 kHz。为了确保兼容性,系统必须将int10模式3 BIOS调用重新映射到所需的低像素格式支持模式。

2.2.4.2 监视器低像素格式的支持要求

640x480像素格式,60 Hz刷新,像素时钟为25.175 MHz,水平频率为31.5 kHz。

水平频率可以理解成屏幕一秒钟刷新多少行像素,即60*(480+2+33+10)=60*525=31500

2.2.5 EDID(Extended Display Identification Data)

在创建DVI规范的同时,VESA(Video Electronics Standards Association)正在进行开发工作,该标准机构负责创建监视器识别标准。

2.2.5.1 EDID系统的要求

一个符合DVI规范的系统必须支持EDID数据结构。在系统的过渡支持中,建议使用EDID 1.2和2.0版本。关于监视器支持,不能假设超低像素格式要求(640x480)的像素格式。系统需要读取EDID数据结构以确定监视器支持的功能。

2.2.5.2 EDID监控器的要求

符合DVI标准的监视器必须支持EDID数据结构。建议将EDID 1.2和2.0用于系统的临时支持。DVI低像素格式要求不必在EDID数据结构中列出,但显示器必须显示清晰的图像。如果显示器是一个固定的像素格式的显示器,那么EDID的“首选时序模式”位必须设置(EDID 1.2数据结构偏移量18h bit 1;EDID 2.0数据结构偏移量7Eh bit 6),并且监视器的本机像素格式必须报告在第一个详细的时间字段。

2.2.6 DDC(主要是电器规范,不研究)

2.2.7 伽马

术语“伽玛”经常被误用;有关该术语及其用法的详细描述,请参阅sRGB规范,网址为 srgb.com。简而言之,CRT显示器和电视显示器具有固有的非线性颜色传递函数,需要对输入数据进行预补偿以生成标准化图像。然而,计算机生成的图形数据(如电子表格、文字处理文档等)是在数学上线性的颜色空间中生成的。由于这些数据通常在CRT设备上显示,图形控制器会应用称为伽玛校正的显示传递函数,以在数据离开图形控制器时进行预补偿。典型的CRT显示传递函数由形式为Y=x^g的指数函数表示,其中x是输入信号,Y是输出信号,g(伽玛)是显示传递特性,对于CRT来说大约是2.2。

在不同类型的输出设备之间生成准确的颜色再现是该行业持续研究和开发的主题。国际色彩联盟等标准机构正在努力标准化方法。因此,本规范的目的和范围不包括在此领域定义标准。然而,在进一步确定要求之前,建议将数字显示器的默认颜色传递函数设置为类似于模拟CRT显示器的值(g = 2.2),因为模拟CRT显示器在计算机显示市场中占据主导地位。这将在很大程度上避免数字显示器上的颜色呈现不佳以及图形控制器必须支持备选传递函数的必要性。

2.2.8 缩放比例

固定像素格式(即空间采样)监视器有两种基本操作模式:1.显示原本像素格式数据和2.显示符合监视器像素格式的数据。

缩放到原本像素格式是显示器的责任。它被假定为一个质量标准,这是监视器的一个增值特性。固定像素格式的数字监视器应尽一切努力提供一个高质量的标准,从而允许最终用户的体验匹配的典型的模拟多同步监视器。

2.2.8.1 系统缩放的要求

主机可以假定监视器可以显示所需的低像素格式模式,即使它没有在EDID数据结构中列出。如果监视器不支持请求的像素格式,则图形控制器可以1.将图像缩放到监视器的原本像素格式,2.将图像居中心或3.将像素格式报告为不可用。系统可以提供一个实用程序,允许最终用户在监视器标准和系统标准之间进行选择。默认的操作模式是在可用时使用监视器的标准。

注意:为了消除级联标准的可能性,如果系统对图像进行缩放,那么系统必须将图像缩放到显示器定义的首选模式定时(固定像素格式面板中的原本像素格式)。

2.2.8.2 监视器的缩放的要求

如果监视器被标识为支持多个像素格式的固定像素格式设备,那么对于那些支持的像素格式,需要存在一个监视器标准,并且应该始终使用。显示器应在其最大像素格式和低像素格式要求之间扩展到所有标准像素格式。监视器必须只在EDID数据结构中要求支持可以在至少一个维度中全屏显示的像素格式。

如果显示器没有标准,显示器必须只在EDID数据中报告其单一固定像素格式,但当显示所需的低像素格式模式时,显示器仍然必须显示清晰的图像。

注意:如果符合DVI的显示器仅支持(即至少一个方向的全屏)其原本固定像素格式,如果所需的低像素格式模式清晰但不是全屏显示,则显示器必须仅列出支持其原本的固定像素格式。如果所需的低像素格式模式至少在一个维度上全屏显示,则可以在EDID中列出。

注意:如果显示器是一个固定的像素格式的显示器,则必须设置EDID的“首选时序模式”位,并且必须在第一个详细的时序字段中报告显示器的本地像素格式。(EDID“首选时序模式”位位于EDID 1.2数据结构偏移18h位1和EDID 2.0数据结构偏移7Eh位6d)这个优选模式时序识别要求旨在允许系统确定平板显示的原生像素格式(通过设计,固定像素格式设备)。 (联系2.2.5.2)

2.2.9 热插拔

热插拔检测(HPD)是一种系统级功能,需要在硬件和软件级别的行业规范。定义一个完整的系统解决方案超出了本规范的范围。因此,本节仅限于热插拔信号的规范,该信号为一个完整的系统解决方案提供了硬件基础。本规范要求操作热插拔针脚,任何对热插拔针脚的特定系统响应都是可选的。

预计未来的软件规范,这将提供完整的系统解决方案。在此期间,图形驱动程序可以自由基于热插拔信号生成其自己的应用程序。

热插拔事件:

监视器附件:当检测到“监视器附加”热插拔事件时,图形子系统必须生成一个系统级事件(依赖于操作系统),以允许操作系统读取监视器的EDID数据。如果图形子系统和监视器支持兼容的像素格式,则操作系统应该启用监视器和TMDS。如果需要,请进行链接。

监控器删除:当检测到“监控器删除”热插拔事件时,图形子系统必须生成系统级事件(依赖于操作系统)以通知操作系统。此外,如果DVI认为监视器是一个数字监视器,则当检测到“监视器删除”时,图形子系统必须在1秒之内禁用TMDS的数据发送机。

2.2.9.1 系统的热插拔要求

当主机检测到+高于2.0伏或低于+0.8伏的转换时,图形子系统必须生成一个系统级事件(依赖于操作系统),以通知操作系统该事件。此外,如果DVI认为监视器是一个数字监视器,则当检测到“监视器删除”时,图形子系统必须在1秒之内禁用TMDS的数据发送机。

2.2.9.2 监视器的热插拔要求

只有当主机可以读取EDID数据结构时,监视器才能在连接器的热插拔检测(HPD)针脚上提供大于+2.4伏的电压。当EDID数据结构无法读取时,则HPD引脚上的电压必须低于+0.4伏。

实现注意:作为热插拔支持的一个例子,HPD支持的一个简单的监控实现可以是EDID电源的一个上拉式电阻。

2.2.10 HSync,VSync和数据有效的需要

预计数字CRT显示器将可以连接到DVI接口。为了确保显示独立性,需要数字主机在T.M.D.S.中分别对HSync和VSync进行编码通道。

数字主机需要在T.M.D.S.中对数据启用(以下简称DE)进行编码通道。DE必须是一个活跃的高信号。

注意:在T.M.D.S.中的位映射规定在第3.2节中。

2.2.11 数据格式

2.2.11.1 系统数据格式的支持

系统必须至少支持24位MSB对齐的RGB TFT数据格式。24位MSB对齐的RGB TFT数据格式在VESA EDID规范3.0版本中定义。请注意,这里也定义了较低的颜色深度。

如果监视器实现了EDID 1.2数据结构,则系统必须假设监视器支持24位MSB对齐的RGB TFT数据格式。

(VESA EDID规范3.0版本有待进一步学习)

2.2.11.2 监视器数据格式的支持

如果监视器选择实现EDID 1.2数据结构,那么监视器必须接受在VESA EDID规范3.0版本中定义的24位MSB对齐的RGB TFT数据格式。

如果监视器实现了EDID 2.0、1.3或更新的数据结构,则监视器可以指定在所使用的EDID数据结构中可定义的任何数据格式。在所有情况下,监视器必须至少支持24位MSB对齐的RGB TFT数据格式。

2.3 带宽

2.3.1 所支持的最低频率

指定支持的最小频率,以允许链路区分活动低像素格式链路和电源管理状态(非活动链路)。DVI规范所要求的最低像素格式为640x480@60Hz(时钟定时为25.175 MHz)。如果时钟小于22.5 MHz,那么T.M.D.S的转换将超过一秒。(没懂)

2.4 数字监视器电源管理(不研究)

2.5 信号列表

| 名称 | 描述 |

| TMDS信号 | |

| TMDSClock + & - | TMDS时钟差分对 |

| TMDSClock Shield | TMDS时钟差分对的屏蔽 |

| TMDSData0 + & - | TMDSlink #0 channel #0 差分对 |

| TMDSData0/5 Shield | TMDSlink #0 channel #0 and link #1 channel #2 的共享屏蔽 |

| TMDSData1 + & - | TMDSlink #0 channel #1 差分对 |

| TMDSData2/4 Shield | TMDSlink #0 channel #2 and link #1 channel #1的共享屏蔽 |

| TMDSData2 + & - ir | TMDSlink #0 channel #2 差分对 |

| TMDSData1/3 Shield | TMDSlink #0 channel #1 and link #1 channel #0的共享屏蔽 |

| TMDSData3 + & - | TMDSlink #1 channel #0 差分对 |

| TMDSData4 + & - | TMDSlink #1 channel #1 差分对 |

| TMDSData5 + & - | TMDSlink #1 channel #2 差分对 |

| 控制信号 | |

| Hot Plug Detect (HPD) | 信号由监视器驱动,使系统能够识别监视器的存在。 |

| DDC Data | DDC接口的数据线。 |

| DDC Clock | DDC接口的时钟线。 |

| +5V Power | 系统提供的+5伏信号,使监控器在不通电时提供EDID数据。 |

| Ground (for +5V) | +5伏电源引脚的接地参考线。作HSync和VSync信号的返回 |

| 模拟信号 | |

| Analog Red | 模拟红色信号。 |

| Analog Green | 模拟绿色信号。 |

| Analog Blue | 模拟蓝色信号。 |

| Analog Horizontal Sync | 模拟接口的水平同步信号。 |

| Analog Vertical Sync | 模拟接口的垂直同步信号。 |

| Analog Ground | 模拟信号的共同地。仅用于模拟红、绿、蓝信号的返回。 |

3. TMDS协议规范

3.1 概述

3.1.1 链接架构

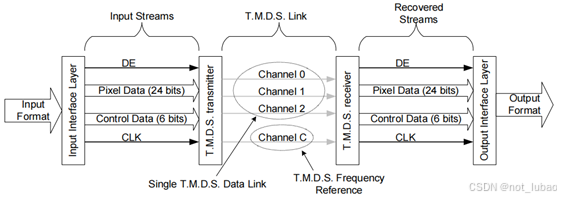

发送机通过TMDS进行编码并串行传输输入数据流链接到一个TMDS接收机,如下图。使用的TMDS编码规范为了通过链接进行输入流,定义了TMDS传输的编码器和解码器的功能要求。尽管在这个规范中,每个链路的输入流被表示为24位宽,但这并不意味以任何方式限制T.M.D.S发送机或接收机的接口格式。发射机和接收器不需要提供一个24位并行接口才能符合本规范。也未指定附加的输出层和输入层的功能。

输入包含像素数据和控制数据。发射机根据数据启用信号(DE)的状态,在任何给定的输入时钟周期上对像素数据或控制数据进行编码。活动数据启用信号表示要传输像素数据。请注意,当传输像素(控制)数据时,控制(像素)数据将被忽略。在TMDS的接收方,恢复的像素数据只能在DE激活时转换;而恢复的控制数据只能在DE非激活时转换。

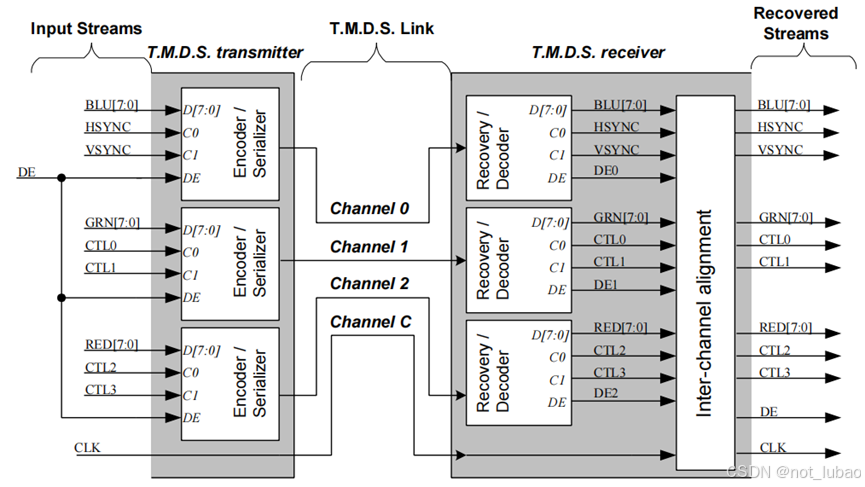

发射机包含三个相同的编码器,每个编码驱动一个串行TMDS数据通道,每个编码器的输入是两个控制信号和八位像素数据。根据DE的状态,编码器将产生来自2个控制信号或来自8位像素数据的10位字符。每个解码器的输出是一个连续的TMDS的字符。

3.1.2 时钟

使用的TMDS时钟信道携带一个pair-to-pair频率参考,其中接收器为传入的串行数据流产生一个比特率采样时钟。由于必须容忍的高pair-to-pair 倾斜,必须对每个数据通道的衍生样本时钟的相位进行单独调整。用于数据恢复的时钟生成方法是特定于实现的,并且超出了本文档的范围。

3.1.3 同步

使用TMDS的接收方必须确定串行数据流中的character boundaries(字符边界)的位置。一旦在所有数据通道上建立了字符边界,接收机就被定义为与串行数据流同步,并可以恢复和解码数据通道中的字符。使用TMDS的数据流为解码器的同步提供了periodic cues(周期性的线索)。

即确定数据流中每段字符数据的开始与结束位置。

使用TMDS选择表示像素数据的字符包含5个或更少的高电平与低电平之间的转换,而TMDS选择来表示控制数据的字符包含7个或更多的转换。(直流平衡?)在消隐期间传输的字符的高转换内容构成了在解码器处进行字符边界同步的基础。虽然这些字符在串行数据流中不是唯一的,但它们足够相似,解码器可以在传输的消隐间隔期间唯一地检测这些字符的存在。这种检测的精确算法是超出本文档范围的实现细节,但定义了接收机同步的最小条件。

3.1.4 编码

第一阶段:

- 生成最小过渡的9位字符: 在视频数据期间,第一阶段从输入的8位生成一个最小过渡的9位字符。这个字符用于在第二阶段执行直流平衡。

- 异或和XNOR运算: 该阶段包括对输入的8位进行操作生成的8位表示,再加上一个额外的标志位,用于指示生成字符的方式(是通过异或还是异或非)。生成这个字符的过程涉及对输入的每一位与先前生成的位的顺序进行异或或异或非(XOR或XNOR)函数操作。

- LSb保持不变: 通过建立起始值,输出字符的其余7位是通过对输入的每一位与先前生成的位进行XOR或XNOR操作得到的。LSb(最低有效位)从解码器输入到输出时保持不变。

- 标志位表示操作方式: 生成的9位字符包括8位数据和一个标志位,用于指示是使用XOR还是XNOR函数生成输出字符。

第二阶段:

- 直流平衡处理: 第二阶段对通过第一阶段产生的9位字符的前8个数据位执行近似的直流平衡。这涉及有选择地反转这些数据位,以确保整体字符流保持直流平衡

- 第10位指示反转: 在第二阶段,一个额外的第10位被添加到码字中,用于指示是否已经对前8个数据位进行了反转。

- 动态编码决策: 编码器根据在传输流中跟踪的1和0之间的跳变以及当前字符中发现的1和0的数量,确定何时反转下一个字符。如果传输的1太多,并且输入包含的1比0多,那么就会反转码字。

- 接收端解码: 在接收端,通过检查TMDS字符的第10位,可以简单地解码动态编码决策,并相应地条件反转输入码字。

3.1.5 双链路体系结构

TMDS链路架构中数据通道的数量最初是基于对视频数据所需带宽和使用一个数据通道分别传输红色、绿色和蓝色像素数据的逻辑简单性的考虑而选择的。这样的设计旨在平衡对带宽效率和实现简便性的需求。

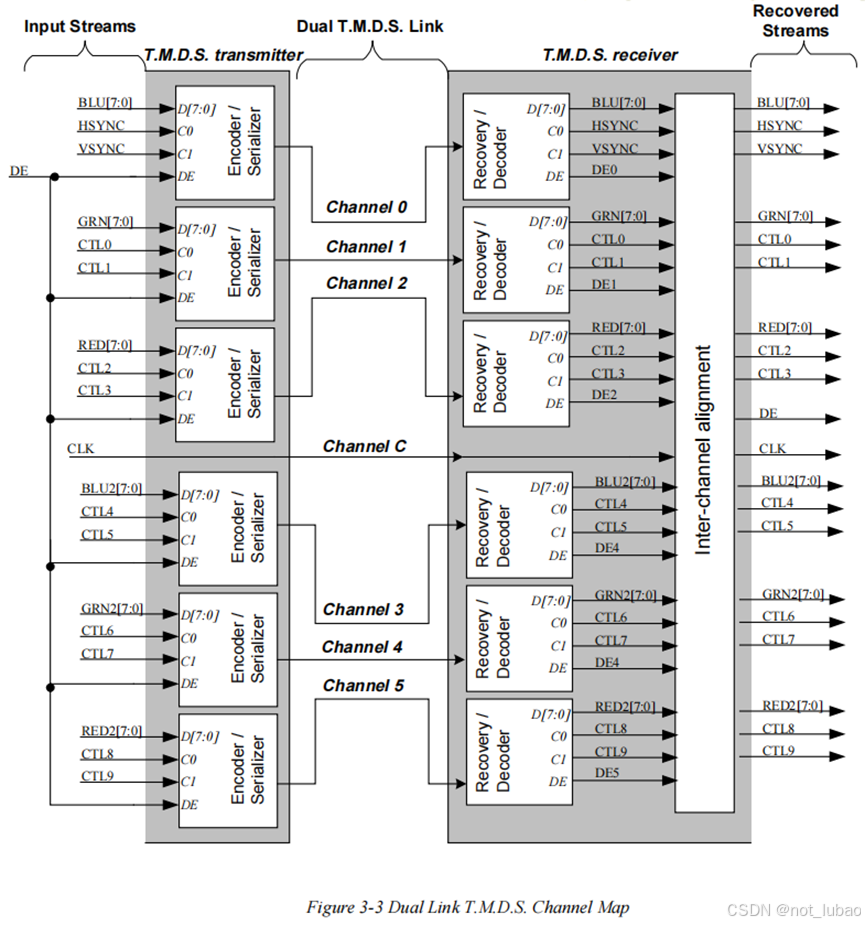

这个规范所指的双TMDS(Transition Minimized Differential Signaling)链路配置使用了六个数据通道,共享一个时钟通道,以增加接口的带宽。在这种配置下,第一个数据链路传输奇数像素,而第二个数据链路传输偶数像素。每行的第一个像素被定义为像素编号为一的奇数像素。

3.2 编码器规范

3.2.1 通道映射

单链路TMDS发射机由三个相同的编码器组成,并将输入流信号映射到其中,如下图。两个控制信号和bit的像素数据被映射到每个编码器。

一个双链路发射机包含另外三个数据通道(图3-3)。双链路配置传输第一链路上的每个水平线的奇数像素和第二链路上的每个水平线的偶数像素。每一行的第一个像素是像素数1(一个奇数像素)。

保留除水平同步(HSync)和垂直同步(VSync)以外的所有控制信号。控制信号CTL1、CTL2和CTL3必须在发射机输入处保持逻辑低。建议CTL0也保持在逻辑低,然而由于某些传输芯片(transmitter chips)出于遗留原因可能会通过CTL0线发送控制信号。如果在CTL0线上传输此信号,唯一的条件是该信号的上升沿发生在单个像素输入时钟的偶数边沿或奇数边沿,而在链路处于活动状态时,不得在偶数和奇数之间切换。(???什么意思)

3.2.2 编码算法

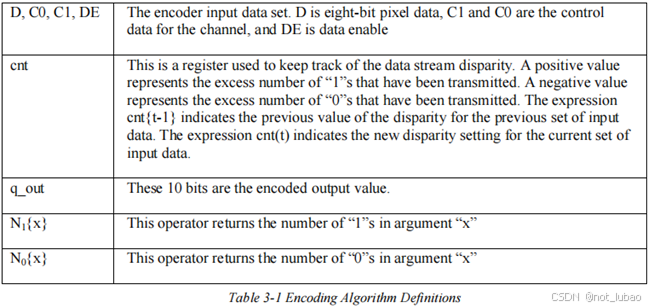

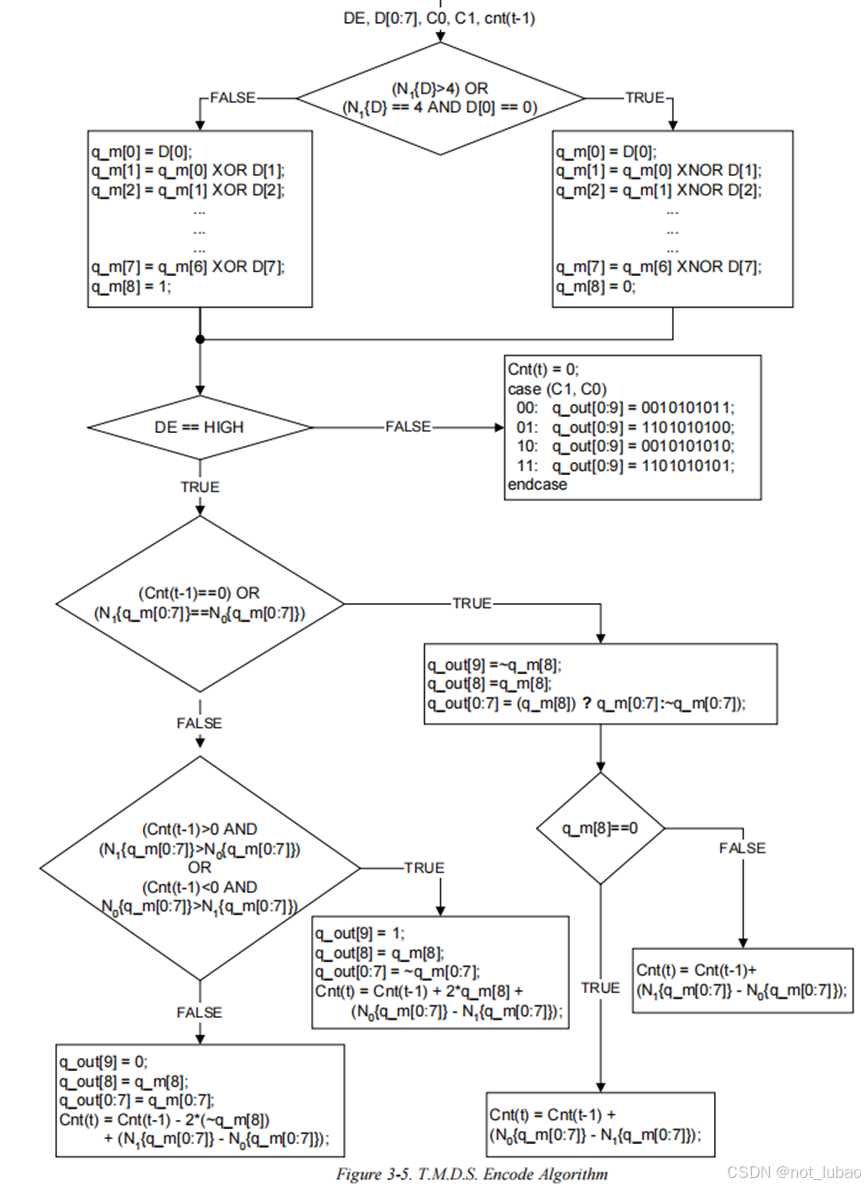

使用的TMDS编码算法定义如图3-5所示,定义见表3-1。编码器在消隐期间产生4个唯一的10位字符,在活动数据期间产生460个唯一的10位字符中的一个。在链接上使用所有其他10位字符是保留的,不能由编码器生成。

(详情见HDMI文档 5.3 视频数据编码)

3.2.3 串行化

在TMDS(Transition Minimized Differential Signaling)编码器产生的字符数据流中,进行串行化是为了在TMDS数据通道上传输。每个字符的最低有效位(LSB),即q_out[0],是首先被传输的。

3.3 解码器规范

3.3.1 时钟恢复

在TMDS接收端,必须具备与传输时钟相位锁定的能力,该时钟的频率范围从25 MHz一直到接收端规定的最大频率。相位锁定到输入时钟必须在输入时钟符合第四章电气规范的规定后的100毫秒内发生。

3.3.2 数据同步

在任何长度大于128个字符的空白时期,接收器必须与数据流建立同步。在同步检测之前,以及在失去同步的时期,接收器不得更新已恢复数据流的信号。

3.3.3 解码算法

3.4 连接时序要求

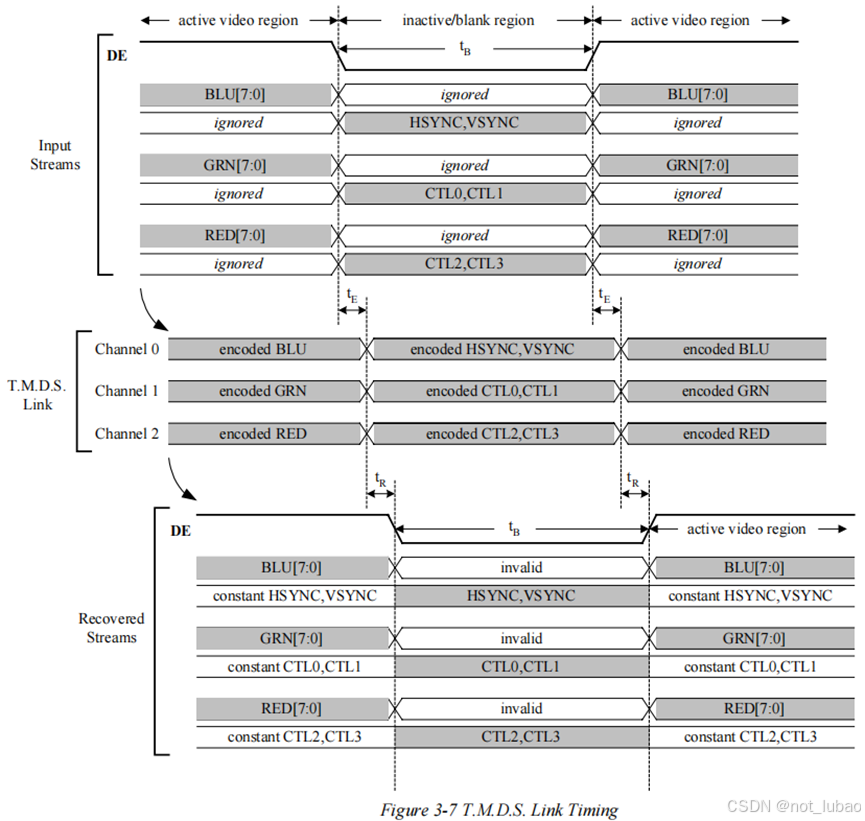

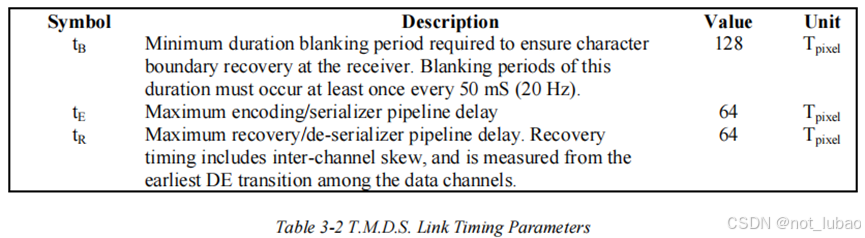

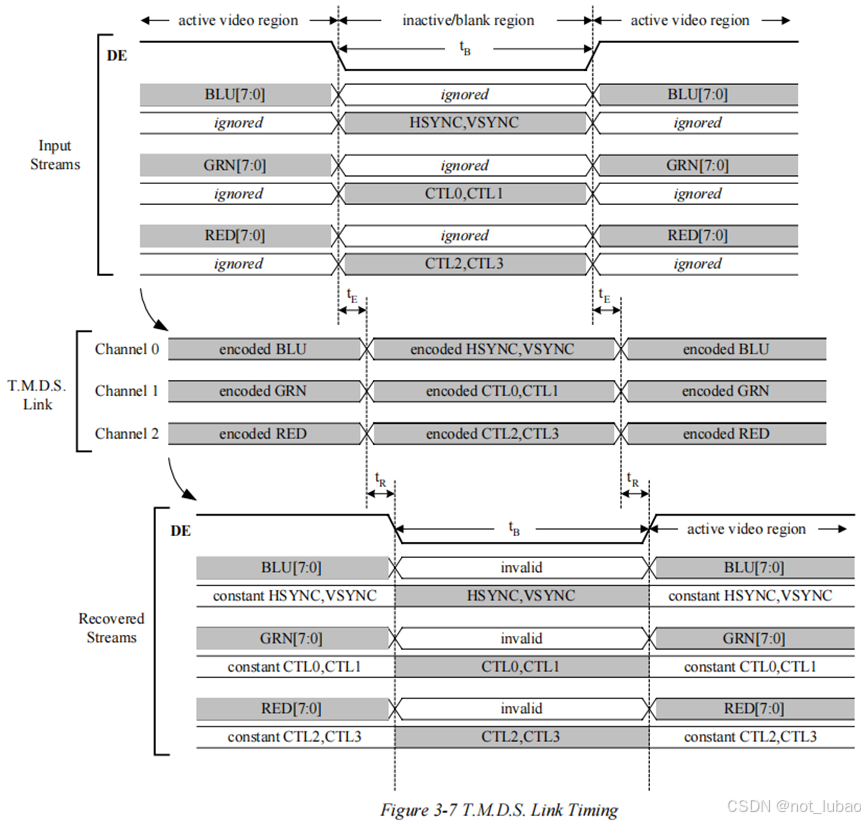

指定了编码、串行化和解码的最大时间,以便跨接口绑定延迟。图3-7和表3-2指定了这些参数。

最上面的是主机输入的数据,中间是传输信道里的数据流,下面的是从机接收到串行数据流并将其恢复之后的内容。

主机端在有效视频区输入视频信号,无效视频区输入行/列同步信号和控制信号,经过TE后转换为10位的编码并通过信道串行输出;从机接收到串行数据后进行解码,经过TR后并恢复成并行数据。

注意恢复后的数据流中,有效视频区包含了恒定不变的行/列同步信号和控制信号。(为什么?)

tB指的是确保接收器在接收到的数据中能够正确地恢复字符边界的最小持续消隐时间。为了实现这一点,必须至少每50毫秒(20赫兹)发生一次具有这种持续时间的消隐时期。

4. 电气技术规范(不研究)

5. 物理互连规范

5.1 概述

DVI(Digital Visual Interface)兼容的主机系统可以提供纯数字接口或混合模拟和数字接口。系统侧的连接器用于区分系统的功能。这两种定义的连接器具有相同的物理外部尺寸。在每种情况下,数字信号都存在,允许具有数字接口的显示器直接连接到任一系统连接器上。由于纯数字插座不具有模拟显示器的模拟引脚插槽,模拟显示器的插头将无法与纯数字系统连接。

5.2 机械特性

5.2.1 信号引脚分配

5.2.1.1 数字式连接器

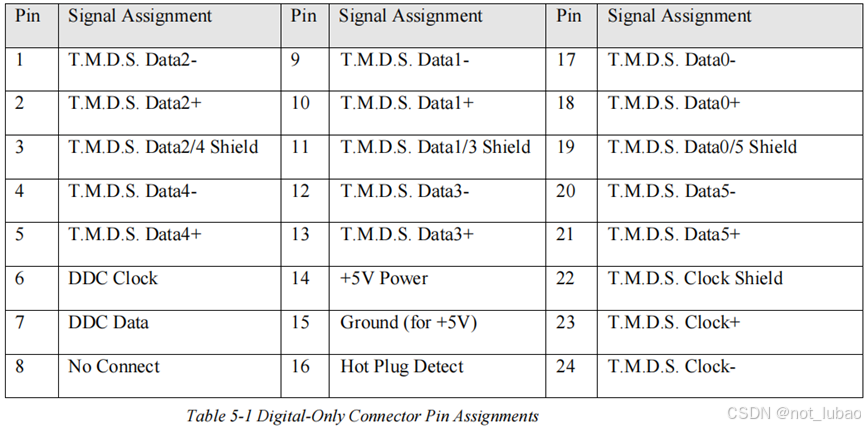

仅数字连接器包含24个信号触点,排列为3行,每行8个触点。表5中列出了仅数字接口的信号引脚分配情况。

前五行为6个差分信道,其中包含三个屏蔽接口;6-7为DDC时钟和数据;8为保留接口;14-16为电源/地和热插拔检测;22-24为时钟屏蔽接口和时钟差分信号。

DDC(Display Data Channel,主要用于EDID的传输)传输。在传输流程中,DDC通信几乎是最先做的(Hotplug之后),因为主从两个设备需要通过DDC来获得他们对方设备的EDID,从而得到各种信息。(与 2.2即插即用 也有关系)Clock和Data实际上为I2C接口。

DDC2B是更新的一种协议,具体区别细节仍待学习。

屏蔽接口为了减少共模噪声的影响。

5.2.1.2 模拟式连接器(也有数字部分)

机械连接包括29个信号接触点,分为两个部分。

第一部分数字信号接口组织成3行,每行有8个接触点。第二部分包含专门设计用于模拟视频信号的五个信号。水平同步、垂直同步、红色(R)、绿色(G)和蓝色(B)在模拟实现中都是必需的。信号引脚分配列在表5-2中。

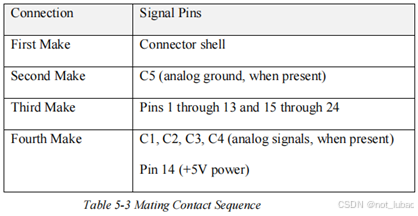

5.2.2 接点接通顺序

三、总结

其模拟接口与VGA基本相同,不做赘述。

数字接口主要分为2组3个通道的信号接口(即总共2*3=6)和时钟,DDC信道和热插拔检测。

DDC近似于i2c接口,用于主机读取显示设备的EDID数据来识别显示器类型和功能、支持的像素格式等,以判断要以什么形式输出视频数据。

发射机根据数据启用信号(DE)的状态,在任何给定的输入时钟周期上对像素数据或控制数据进行编码。数据启用信号有效表示要传输像素数据。请注意,当传输像素(控制)数据时,控制(像素)数据将被忽略。在TMDS的接收方,恢复的像素数据只能在DE激活时转换;而恢复的控制数据只能在DE非激活时转换。

发射机包含三个相同的编码器,每个编码驱动一个串行TMDS数据通道,每个编码器的输入是两个控制信号和八位像素数据。根据DE的状态,编码器将产生来自2个控制信号或来自8位像素数据的10位字符。每个解码器的输出是一个连续的TMDS的字符。

双TMDS链路配置使用了六个数据通道,共享一个时钟通道,以增加接口的带宽。在这种配置下,第一个数据链路传输奇数像素,而第二个数据链路传输偶数像素。每行的第一个像素被定义为像素编号为一的奇数像素。

最上面的是主机输入的数据,中间是传输信道里的数据流,下面的是从机接收到串行数据流并将其恢复之后的内容。

主机端在有效视频区输入视频信号,无效视频区输入行/列同步信号和控制信号,经过TE后转换为10位的编码并通过信道串行输出;从机接收到串行数据后进行解码,经过TR后并恢复成并行数据。

注意恢复后的数据流中,有效视频区包含了恒定不变的行/列同步信号和控制信号。

具体编码方式详见3.2.2

四、问题

- 具体信号和时钟的时序关系(是传输时钟的一个周期内发送10bit数据吗)

- 为什么接收端恢复数据后在有效像素段存在恒定不变的行/列同步信号和控制信号

- 为什么行/列同步信号和像素数据不是同时发送的

- EDID怎么进行读取和分析

- 热插拔如何实现

- 时钟恢复和数据同步的具体操作

- 3.2.1 CTL[3:0]的用处

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?