与技术无关的部分会省去,但标题编号不变(备注或解释)

1.1 显示端口(displayport)标准组成部分

显示端口标准被分为以下几个部分,其中定义了显示端口的整体体系架构(architecture)和构造(structure):

第一章——介绍

介绍部分定义了对显示端口的高级行业需求,以及协议、电气和机械部分,旨在满足的最终技术目标。本节还包括总体标准、引用和显示端口架构概述的术语表。

第二章——链路层

链路层部分描述了用于配置和管理正向(主机到显示)传输通道和辅助双向通道上的拓扑结构和数据流的协议。同时包括SST(单流传输)模式和MST(多流传输)模式。

第三章——物理层

物理层部分描述了显示端口发射机和接收机实现的电气要求。它还定义了通过电缆或电路板轨迹向显示端口链路层传输数据所需的电路和编码方法。

第四章——机械

机械部分定义了内部和外部显示端口的接头和电缆要求,用于传输由显示端口物理层定义的电信号。

第五章——发射机、接收机、分支设备之间互操作的策略需要

设备和链路介质需求部分描述了发射机、接收机设备和分支设备的策略需求,以支持实现显示端口连接的设备之间的互操作性。

1.6 位和字节排序的命名法

本节描述主链路和AUX CH的位和字节顺序。

AUX CH:显示端口发射机和显示端口接收机之间的半双工、双向辅助信道。1对传输数据的差分对由两种事务格式之一组成,曼彻斯特格式1Mbps或传真格式720Mbps。显示端口上游设备是启动AUX事务的主服务器(也称为AUX CH请求程序)。显示端口下游设备是响应由请求者发起的AUX事务的从设备(也称为AUX CH复制器)。

1.6.1 位排序

1.6.1.1 并行位排序

对于每种颜色的8位数据,红色位7(R7)放置在第7位,而红色位0(R0)放置在第0位。

对于每种颜色的6位数据,红色位5放置在第7位(R5),而绿色位4(G4)放置在第0位。

即红色6bit占据7~2,绿色的最高的2bit占据1~0

1.6.1.2 信道编码后的序列位排序

主链路(ANSI 8B/10B)

首先传输最不重要的位,最后传输最重要的位。

AUX CH(Manchester II in Manchester Transaction Format mode或ANSI8B/10B in FAUX transaction format mode)

首先传输最重要的位,最后传输最不重要的位。

1.6.2 字节排序

主链路(主数据流)

首先传输最重要的字节。例如,如果一个RGB像素的颜色位深度为每个颜色16位,则首先传输R[15:8](红色位15~8),后面是R[7:0](红色位7~0)。

当主数据流属性包的某些参数具有多个字节时,首先传输最重要的字节。例如,Mvid[23:16]首先被传输,然后是Mvid[15:8],然后是Mvid[7:0]。

主链路,辅助数据包

如音频示例所示,首先传输最小有效字节Audio sample0 channe0 byte 0,其次是Audio sample0 channe0 byte 1等。

AUX CH

在AUX CH上的突发写/读操作中,地址在每个数据字节后增加一个。对于具有多个字节的DPCD字段,最不重要的字节存储在最低的地址。因此,在AUX事务的突发操作期间,首先传输最小的字节。

DPCD:DisplayPort Configuration Data,显示端口配置数据。映射到DisplayPort接收器设备的DisplayPort地址空间。显示端口发送设备从DPCD地址中读取显示端口链路和接收设备的接收器(receiver)能力和状态。此外,DisplayPort 发送设备写入数据到DPCD的链路配置字段以配置和初始化链路。

例如:

注:如第1.6.1.2节所述,在AUX CH中最重要位首先运输,最不重要位最后运输。

1.7 显示端口概述

显示端口链路由主链路、辅助通道(AUX CH)和热插头检测(HPD)信号线组成。

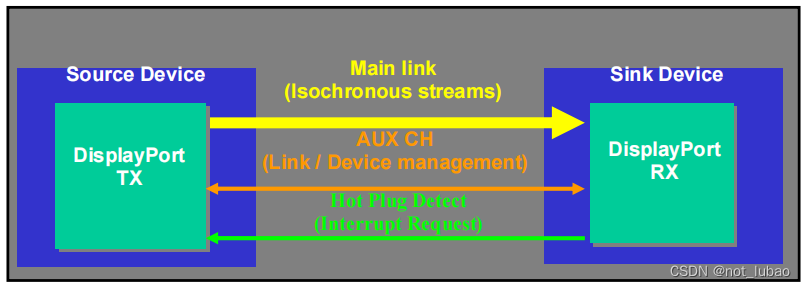

图1-1:显示端口的数据传输通道

主链路是下面使用的单向、高带宽和低延迟通道,用于传输同步数据流,如未压缩的视频和音频。辅助通道AUX CH是一个用于链路管理和设备控制的半双工双向通道。HPD信号也作为接收设备的中断请求。

此外,显示端口连接器有一个电源引脚,用于驱动显示端口中继器或显示端口到传统接口的转换器。

1.7.1 主链路的组成

主链路由一个、两个或四个交流耦合的双端接差分对(称为信道)组成。交流耦合有利于硅圆制造工艺的迁移,因为显示端口发射器和接收器可能有不同的共模电压。

支持三种链路速率,每信道5.4Gbps、2.7Gbps和1.62Gbps。所有已启用的通道必须以相同的链路速率运行。链路速率与像素速率解耦(decouple)。使用时间戳值M和N从链路simple时钟重新生成像素速率。显示端口发射器和接收器的能力以及信道(或电缆)的质量将决定链路速率是否设置为5.4Gbps、2.7Gbps或1.62Gbps。

Time Stamp:两个时钟系统用来保持同步的一个值

信道的数量与像素位深度(每像素位或bpp)和组件位(component)深度(每个组件位或bpc)解耦。无论主链接通道的数量如何,RGB、YCbCr444、YCbCr422的组件位深度都支持6、8、10、12和16。.

像素位深度/bpp:Bits per pixel,每个像素的数据位数。

组件位深度/bpc:Bits per color,每种颜色的比特数,R、G、B或Y、Cb和Cr中每一个的数据位数。

对于RGB和YCbCr444,bpp值是bpc值的三倍;对于YCbCr422,bpp值是bpc值的两倍;仅对于Y,bpp值等于bpc值。

所有信道都传递有数据。没有专用的时钟通道。时钟从使用ANSI 8B/10B编码规则(ANSI X3.230-1994第11条规定)编码的数据流本身中提取。

显示端口设备可以在可用带宽内自由地交换像素比特深度、像素格式和数据流的帧速率。

设计一个数据流到主链路的数据映射是为了方便支持各种信道计数。例如,无论像素位深度和比色法格式如何,像素数据的打包和映射如下:

像素数据在四信道主链路上的数据映射:

Pixels 0、4:Lane 0;

Pixels 1、5:Lane 1;

Pixels 2、6:Lane 2;

Pixels 3、7:Lane 3。

流数据被打包成“微包”,在SST(单流传输)模式下称为“传输单元”,在MST(多流传输)模式下称为MTP(多流传输包)”。在打包流数据并映射到主链路之后,打包的流数据速率将等于或小于主链路的链路符号速率。当它较小时,将插入填充符号。

链路符号率:link symbol rate,显示端口主链路提供的应用带宽。

例如: Link rate = 2.7Gbps;1 lane = 270Mbytes per second;2 lanes = 540Mbytes per second

1.7.2 AUX CH的组成

AUX CH由交流耦合双端差分对组成。曼彻斯特II编码被用作AUX CH的信道编码。与主链路的情况一样,时钟是从数据流中提取的。

AUX CH是半双工、双向的。从设备可以切换HPD信号以中断发送端设备,这将提示AUX CH请求事务。

AUX CH在支持的长达15米及更长的电缆长度上提供1Mbps的数据速率。每个事务不超过500us,最大突发数据大小为16字节。

快速AUX事务格式的AUC CH通过HBR(高比特率)电缆提供720Mb/s的数据速率。

HPD:Hot Plug Detect,热插拔检测。

HBR:High Bit Rate (2.7Gbps per lane);HBR2:High Bit Rate 2 (5.4Gbps per lane)。

1.7.3 链接的配置和管理

在检测到热插拔时,发送端设备通过链路训练/调试(training)来配置链路。通过AUX CH在显示端口发射器和接收器之间的握手电路,以正确的链路速率和正确的驱动电流和均衡水平启用正确的通道数。

在链路训练之后的正常操作期间,接收设备可以通过切换HPD信号来通知链路状态的变化,例如,同步性的丢失,从而导致请求中断。发送设备通过AUX CH检查链接状态并采取纠正措施。这种闭环链路操作增强了发送设备和接收设备之间的鲁棒性和互操作性。

由于链路速率与数据流速率解耦,因此即使当传输流的时间发生变化,显示端口链路也可以保持活动和稳定。

1.7.4 分层、模块化体系结构

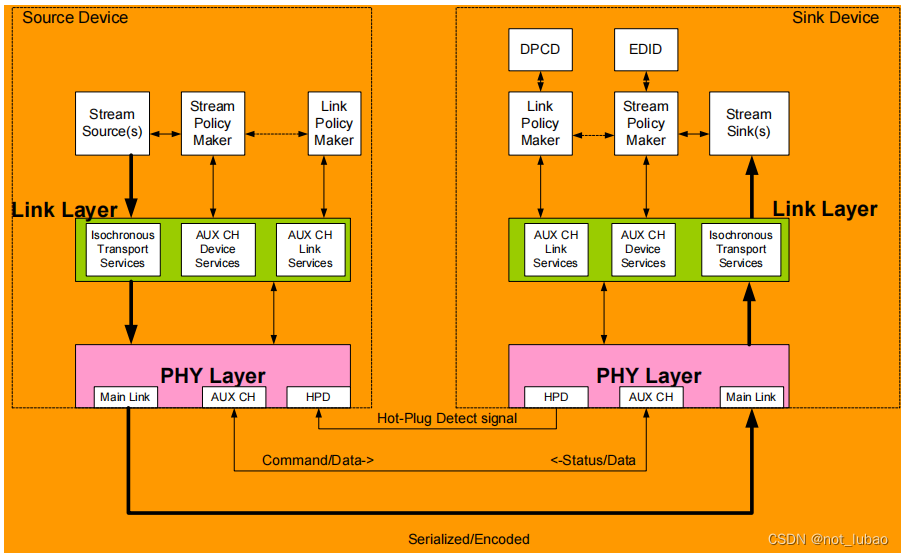

图1-2:显示端口的分层结构

在上图中,接收器设备中的DPCD(显示端口配置数据)描述了接收器的能力,正如EDID描述的接收器设备的能力一样。链接和数据流的政策制定者分别管理链接和数据流。详细信息(状态机、固件或系统软件)是特定实现的。

此外,基于微包的数据传输使显示端口标准能够无缝地扩展到支持多种视听流和其他数据类型。交换机和集线器可用于在多个发送设备和接收设备之间的路线传输数据流。

本文详细解析了显示端口技术,涵盖标准的组成部分、链路层、物理层规范,以及主链路和AUXCH的数据传输机制,包括位和字节排序、链路配置与管理,强调了其分层和模块化体系结构的特点。

本文详细解析了显示端口技术,涵盖标准的组成部分、链路层、物理层规范,以及主链路和AUXCH的数据传输机制,包括位和字节排序、链路配置与管理,强调了其分层和模块化体系结构的特点。

1239

1239

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?