第3章 基本概念

1.CPU内部各寄存器的功能? 数据通路结构?

2.何谓同步控制方式,何谓异步控制?有何主要特征?应用场合? 同步控制中如何引入异步应答的,试举例说明.

3.何谓主从设备,试举例说明。

4.指令?指令系统? 地址码?地址结构?寻址方式?

5.何谓隐式I/O指令?其主要特点是什么? 主机调用外围设备,外设编制可采用那几种方式?

6.微程序控制思想的基本要点是什么?

7.判断下面叙述是否正确,说明理由:串行加法器中的进位链是串行进位链,并行加法器中的进位链只有并行进位链。

8.常用的加法器进位链结构有哪几种?

9.组合逻辑控制器、微程序控制器有何区别?

10.组合逻辑控制器、微程序控制器的时序系统是如何划分的?

11.微命令、微操作、微指令、微指令周期、微程序?

12.1位全加器的结构及关系表达式。

13.并行加法器中的串行进位链结构:Cn = Gn + PnCn-1 并行进位链结构:Cn = Gn + PnGn-1+ … + Pn…P1C0

14.时序信号?时序系统?

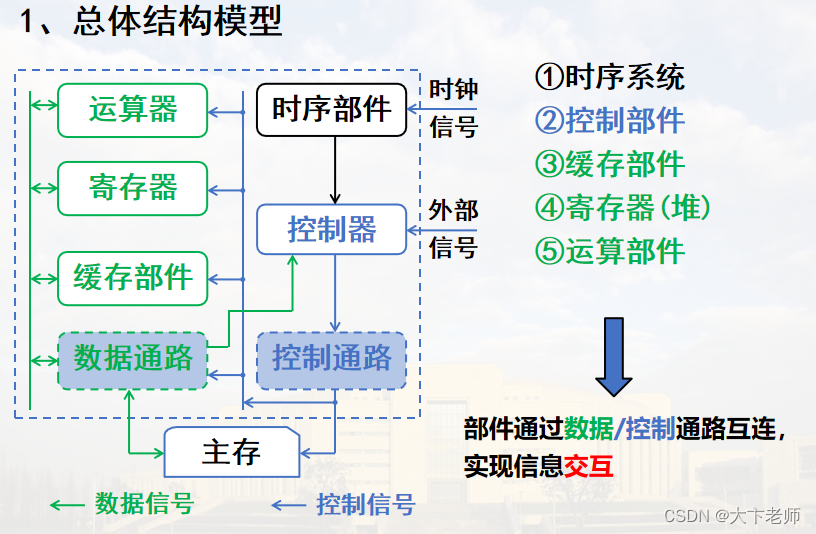

3.1 CPU子系统概述

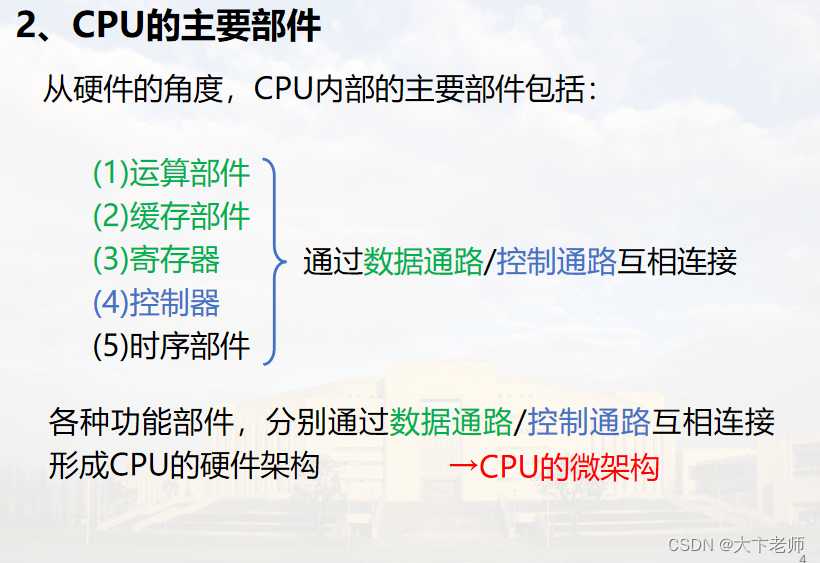

一.CPU的基本结构

通常包含运算部件、缓存部件、寄存器组、微命令产生部件(控制部件)、时序系统,他们通过CPU内部总线(数据/控制通路)连接,实现数据和控制信息的交换

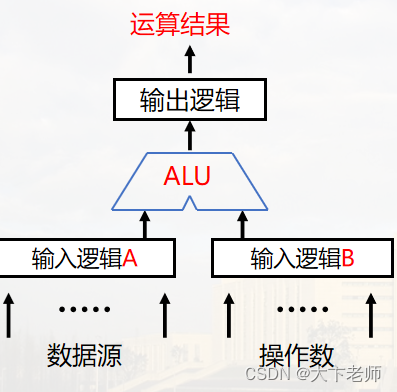

(1)运算部件

对操作数进行运算,主要是算术运算/逻辑运算

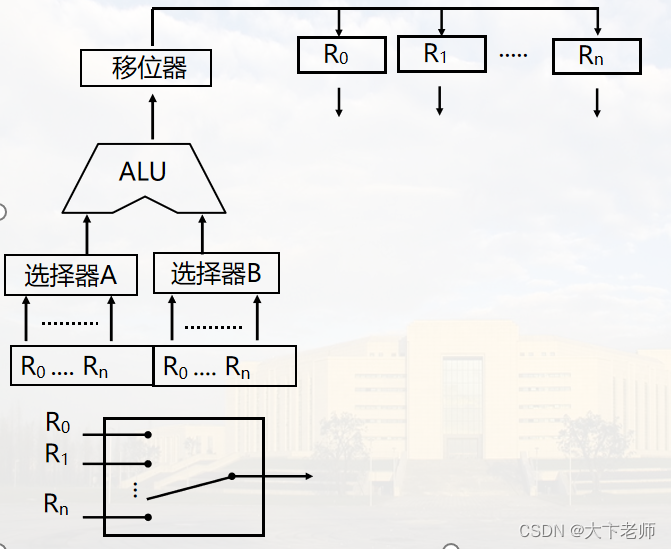

输入逻辑:操作数可以来自各种寄存器,也可以来自CPU内部的数据线,每次运算最多只能对两个数据进星操作,那么有两个输入逻辑:选择器或暂存器,分别悬着两个操作数(数据源和操作数)

输出逻辑 直送、左右移位、字节交换等

算术/逻辑运算部件ALU 设置一个ALU,完成基本的加减运算, 复杂运算由软件完成

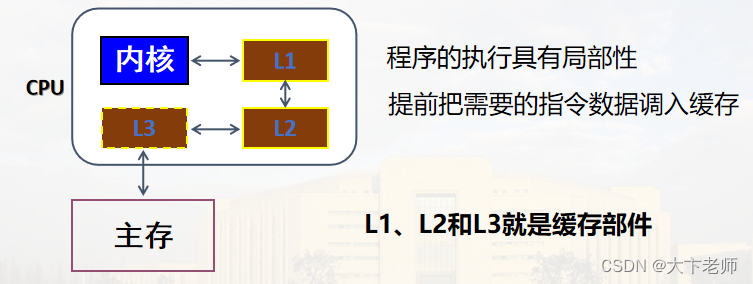

(2).缓存部件

为提高CPU从主存中读取指令/数据的效率,在CPU内部集成了多级缓存部件。

[作用]缓存从主存中读取的部分指令/数据

(3).寄存器组(堆)

存储各种用途的数据信息。

[部件选用]一般用小容量的多端口存储器来构成寄存器组,其中1个存储单元作为1个寄存器。

寄存器的分类,基本类型如下

1.通用寄存器组:多个;

指可通过程序访问、具有多种用途的寄存器,每一个通用寄存器有唯一编号与之对应。

[功能]存放数据(原始数据、中间结果、最终结果等),也可以存放地址进行间接寻址、变址寻址等

例如:累加器AX,基址寄存器BX,计数寄存器CX,数据寄存器DX

2.暂存器

[特征]多个,暂存器不能通过程序访问, 也没有编号,不能在指令中显式使用,只能在CPU工作时内部使用 [主要用途]存放指令执行过程中的中间信息,避免覆盖通用寄存器的内容,这些信息对编程者透明。比如:

(1)从一个主存单元读数据存到另一个单元, 有以下过程 单元-->暂存器-->单元;

(2)为运算器两个输入端提供数据,不能同时直接从其他部件送入ALU, 分两次将操作数送往两个不同的暂存器,两个操作数准备好后才能同时送入ALU运算。

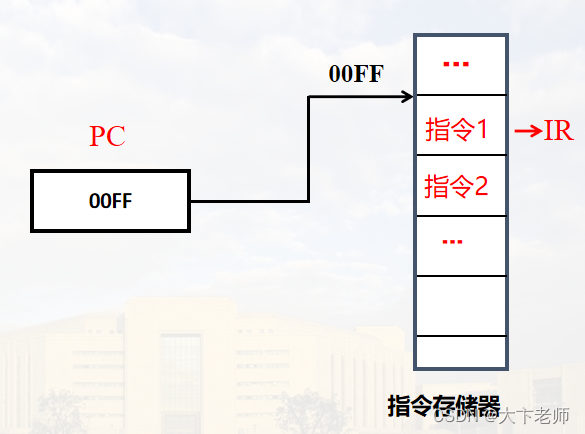

3.指令寄存器(IR)

[主要用途]只有1个,用于存放正在执行的指令代码。它的输出包括操作码信息、地址信息等。是产生微命令的主要逻辑依据。

从存储器(或者指令缓存)中读取到指令以后,就直接存入到指令寄存器中。

4.程序计数器(PC)(指令计数器或指令指针)

[主要用途]仅1个,用来指明指令在存储器中的存放位置,即存储单元的地址码。

[注意]取指令结束后,PC保存的地址码自动修改,增量数取决于现行指令所占的存储单元数,以指向下一条指令的存储单元,因此当现行指令执行完后,PC中存放的是后续指令的地址,修改量取决于指令字长和存储器的编址单位。

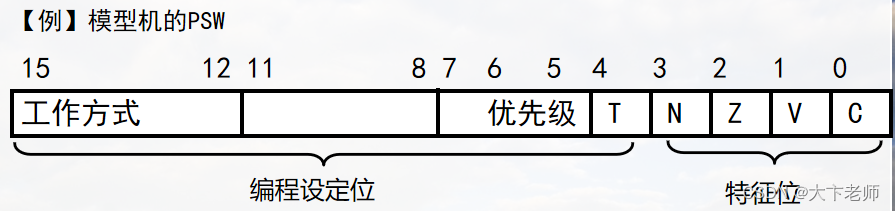

5.程序状态字寄存器(PSW)

[主要用途]仅1个,记录现行程序的运行状态和程序的工作模式

PSW-特征位 也叫标志位,反映CPU的当前状态。 指令执行时,根据情况自动设置这些特征位,作为后续操作的判断依据.

进位位C: 指令执行后,若结果产生进位,则将C置为1,否则置0;

溢出位V: 如果运算结果产生溢出,则将V置为1, 否则置0;

零标志Z: 如果运算结果为0,则将Z置为1, 否则置0;

正负标志N: 如果运算结果为负, 则将N置为1, 否则置0;

奇偶标志P: 如果运算结果中1的个数为奇数, 将P置为1, 否则置0; (Intel8086的规定与此相反) 以上标志位的状态是由指令执行的结果决定的。

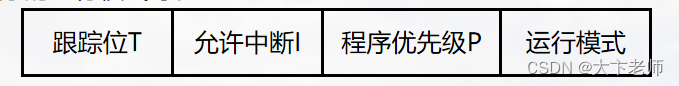

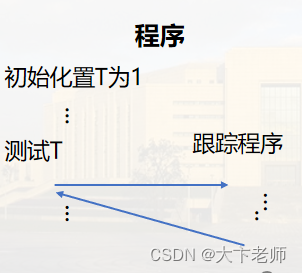

PSW-编程设定位 PSW中某些位或字段可通过程序来设定,以决定程序的调试、对中断的响应、程序的运行模式等。

跟踪位T: 称为断点标志, 主要用于程序调试。 如果编程时, 将T置为1, 且在程序中安排一条测试指令, 当程序执行到该测试指令时, 程序将转入跟踪程序。

中断允许标志或程序优先级字段:

— 中断允许标志I(或TI): 根据当前运行程序与外部中断的紧要程度, 处理器通过对该标志的设置, 决定是否响应中断请求。(在微型计算机中, 一般采用)

— 为每一程序和中断请求设置优先级, 仅当中断请求的优先级高于正在执行的程序的优先级, 才响应中断请求。

工作方式

规定程序的特权级。

用户方式:禁止程序执行某些指令 核心方式:允许程序执行所有指令

PSW在CPU中,反映程序运行状态;控制/状态字在接口中,反映CPU命令、设备状态。

6.地址寄存器(MAR)

CPU访问主存的时候,首先要找到需要访问的存储单元,因此设置地址寄存器来存放目标单元的地址。(并非所有都有)

[主要用途] 只有1个,读写存储器时,先要定位存储单元,因此设置MAR来存放目标单元的地址码。先将有效地址送入MAR,再启动后续的读写操作。

7.数据缓冲寄存器(MDR)

[主要用途] 只有1个,过渡性地存放CPU与主存之间交换的数据。无论是从主存读取的数据,还是写入到主存的数据,都要经过MDR,则有CPU<===>MDR<===>主存。

MAR和MBR都是CPU和主存连接的桥梁

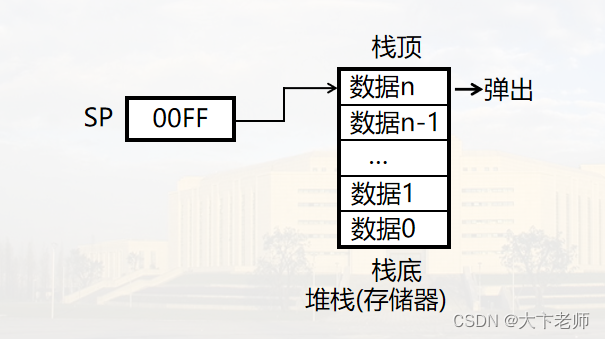

8.堆栈指针(SP)

[主要用途]

仅1个,固定存放堆栈的栈顶单元的地址码。根据这个地址码,去读写堆栈。

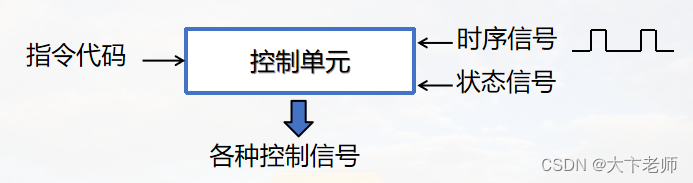

(4).控制器

[主要作用]

根据指令、时钟信号、外部信号等信息,产生各种控制信号(微命令),以便控制各种功能部件协同工作,完成指令的功能。

根据产生微命令的方式,有两类控制单元:

①组合逻辑控制器 组合逻辑硬件电路→控制信号 (组合逻辑控制方式)

②微程序控制器 微程序译码→控制信号 (微程序控制方式)

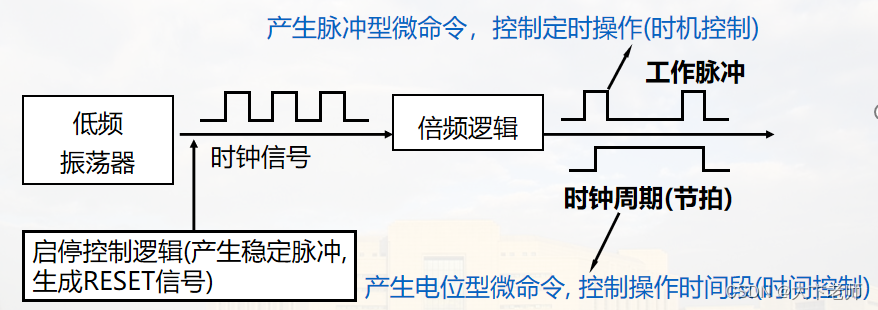

(5).时序系统

要在正确的实践产生所需的控制信号 来控制CPU中各部件工作,在时钟驱动方式下必须有时间信号支持

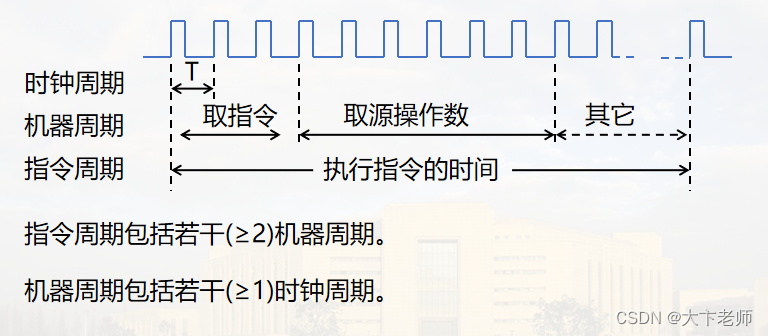

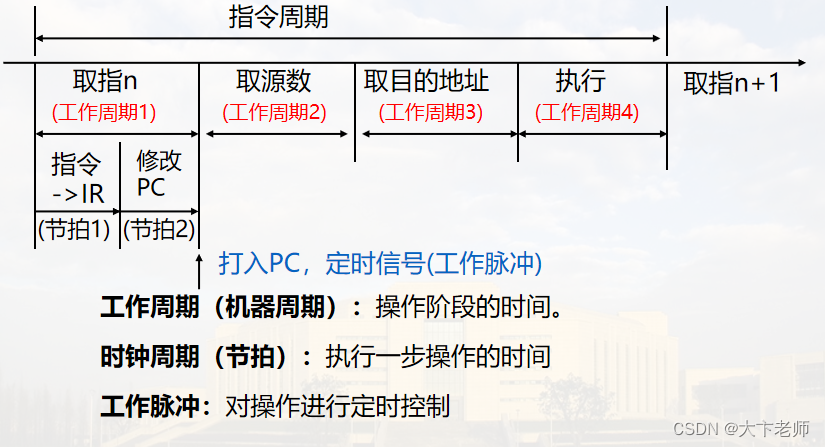

[时序信号]周期、节拍、脉冲等频率型信号序列

[时序系统/时序发生器]产生时序信号的部件,由1个低频振荡器和倍频逻辑组成,振荡器是一个脉冲源,能输出平吕布稳定的基准时钟脉冲,也叫外频。

低频振荡器:它是一个低频脉冲源,能输出固定频率的基准脉冲信号(外频),作为系统时钟信号

系统时钟信号经过倍频放大以后,产生执行指令所需要的各种时序信号:

①节拍信号,即CPU时钟周期信号;

②工作周期信号,即机器周期信号;

③指令周期信号。

指令操作分为取指、取数、执行等阶段,每个操作阶段又分为若干步,如打入IR、PC等。

(6).CPU内部的数据通路的结构

CPU内部由许多部件构成, 如运算器、微命令发生器、各种寄存器、时序控制逻辑等。 就数据信息的传送, 需要为数据的传送提供(设计)传送的通路 (即通信线路)。

问题: 如何设计数据通路?

(寄存器中的数据怎样送往ALU;ALU的结果怎样送往寄存器;寄存器之间的数据如何传送等。 )

不同功能、性能的处理器, 其数据通路是不同的。 总体来说, 有两种典型的数据通路结构:单总线通路和多总线通路。

单总线通路 — 设置一组数据通信总线, 所有数据传送均通过该总线进行; — 结构简单、但不能实现多组数据并发(并行传送);

多总线通路 — 设置多组数据通信总线, 可实现不同数据在不同的通路上传送; — 结构复杂、但能实现多组数据并行传送;

不同结构即是在复杂性与性能之间的选择

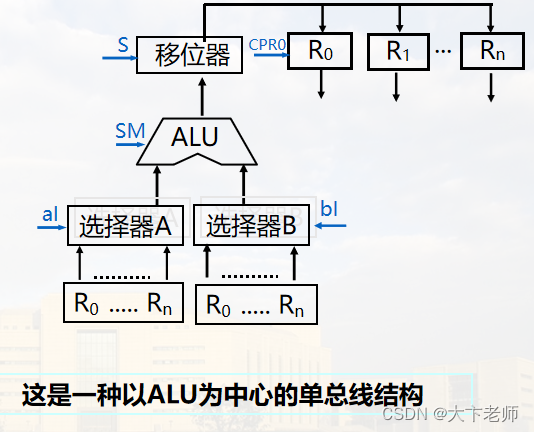

(1) 单组内总线、分离(立)的寄存器结构

主要特点:

各寄存器有独立的输入口和输出口

数据总线为单向, ALU只能通过移位器向总线发送数据, 而不能直接从总线接收数据;

寄存器可接收总线上的数据,但不能直接向总线发送数据;

ALU通过选择器接收寄存器的数据。

根据上述特点, 有以下数据通路完成相应功能:

① 寄存器 ——>运算器 寄存器 ——>选择器——>运算器(由选择控制信号)

② 运算器 ——>寄存器 运算器——>移位器——>寄存器(由移位控制信号)

③ 寄存器 ——>寄存器 寄存器——>ALU——>移位器——>寄存器

— 需要的主要控制信号

寄存器输入选择信号(A、B)

移位器功能选择信号(直传、移位)

寄存器打入脉冲

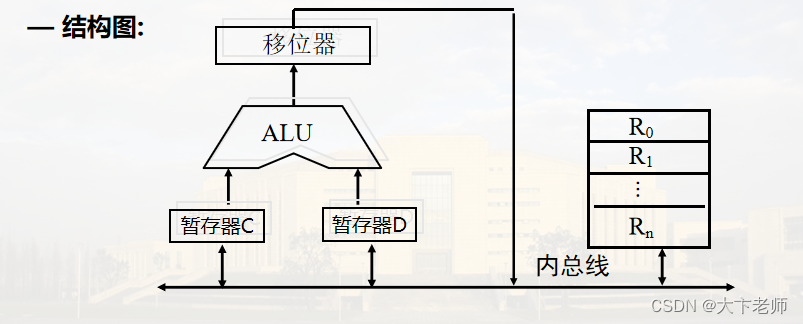

(2) 单组内总线、集成寄存器结构

1.与第一种方式的主要区别在于寄存器的结构

2.CPU内部集成小型的存储器, 存储器的每一个单元作为一个寄存器使用(称为寄存器组),存储单元位数就是寄存器的字长

3.一组双向数据总线连接ALU和寄存器组

4.在两个输入端设置暂存器取代了(独立寄存器结构中的)选择器

主要特点:

数据总线为双向, 运算器ALU既能向总线发送数据, 也能直接从总线接收数据(由暂存器接收);

各寄存器可从总线接收和向总线发送数据;

— 完成 R0 + R1 R2 , 步骤如下:

R0 -->内总线 --> 暂存器C

R1 --> 内总线 -->暂存器D

执行加法

相加结果经移位器(直送) -->内总线

内总线 -->R2

(3).多路总线结构

以上两种CPU数据通路结构中都只有一路数据总线,其优点是结构简单规整、控制方便、但是每个节拍内只能完成一次基本的数据传输操作,即将数据从一个来源地送往一个或多个目的地,效率低,如果想要提升则一般要设置多路。

二.CPU工作原理

1、主要功能

处理指令-控制指令的执行顺序;

执行操作-产生控制信号控制部件工作;

控制时间-控制各步操作的时序;

数据运算-算术和逻辑运算;

2、执行指令的流程

读取指令-根据PC中的指令地址,从主存(缓存)中读取指令,放入指令寄存器IR 指令译码-CPU根据IR保存的指令,将指令分解v恒威操作码和地址码等,即通过控制器进行、产生控制信号; 指令执行-寻址、取数、运算; 后续工作-保存结果、响应外部请求等;

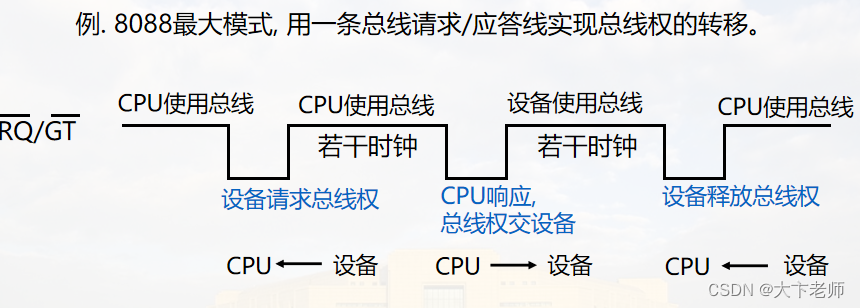

3、部件的控制方式(时序控制方式)

CPU是计算机内部技术最复杂的子系统,如何控制这些部件协同工作,完成指令功能?

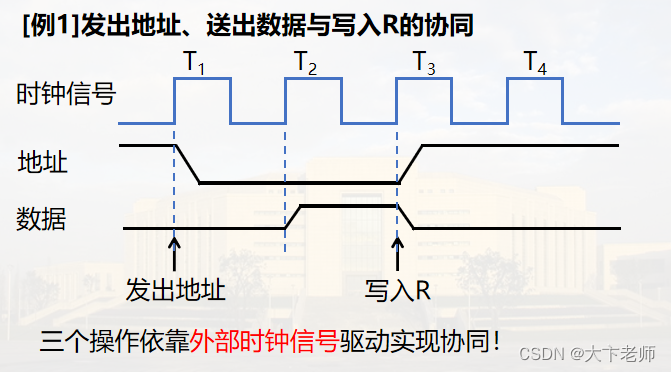

①同步控制方式

②异步控制方式

(1)同步控制

同步控制方式是指用统一的时序信号(由CPU或者其他设备提供)对于各项操作进行控制

时钟周期作为基本的时序单位,固定不变

② 特点

1.有明显时序时间划分;

2.时钟周期时间固定;

3.各步操作的衔接、各部件之间的数据传送受严格同步时钟定时控制。

③ 优缺点

1.时序关系简单, 时序划分规整, 控制不复杂;

2.控制逻辑易于集中, 便于管理。

3.时间安排不合理(缺点)。

④ 采用同步控制的一些条件

1.发送、接收部件(或设备)传送时间确定; 2.各部件速度相近, 传送距离较近。 3.一次通信时间不太长

⑤ 应用场合:

CPU在工作时,各部件都要严格受控于统一信号,所有部件的动作都要时钟信号触发,用于CPU内部、设备内部、系统总线操作。

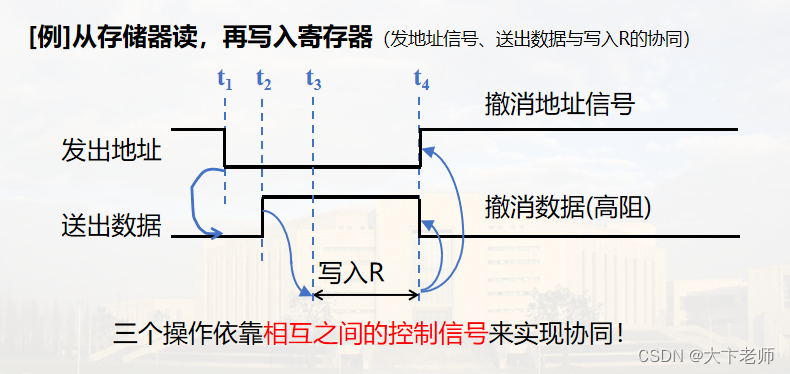

(2)异步控制

① 定义:各项操作按不同需要安排时间, 不受统一时序控制。

② 特点:无统一时钟周期划分, 各操作间的衔接和部件之间的信息交换采用应答方式。

③ 优缺点:

优点:时间安排紧凑、合理; 缺点:控制复杂。

④ 应用场合:

用于异步总线操作(各挂接部件速度差异大、传送时间不确定、传送距离较远等)。

(3) 扩展的同步控制

① 不同指令安排不同时钟周期数

1.既有一套时序系统, 但不同指令又有不同时序

2.指令周期长度可变, 时钟周期长度不变。(可用计数器指示时钟周期数的变化)。

3.时序及控制电路非常复杂(一般不采用)。

② 总线周期中插入延长周期

总线周期经总线传送一次数据所用的时间(送地址、读/写)

③ 同步方式引入异步应答

以固定时钟周期作为时序基础, 引入应答思想。

本文详细阐述了CPU内部各组件的功能,如寄存器、运算部件、缓存、指令系统、数据通路结构,以及同步控制与异步控制的区别及其应用场景。还介绍了微程序控制器、加法器进位链结构以及CPU工作原理,包括执行指令流程和控制方式的选择。

本文详细阐述了CPU内部各组件的功能,如寄存器、运算部件、缓存、指令系统、数据通路结构,以及同步控制与异步控制的区别及其应用场景。还介绍了微程序控制器、加法器进位链结构以及CPU工作原理,包括执行指令流程和控制方式的选择。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?