一、问题缘由

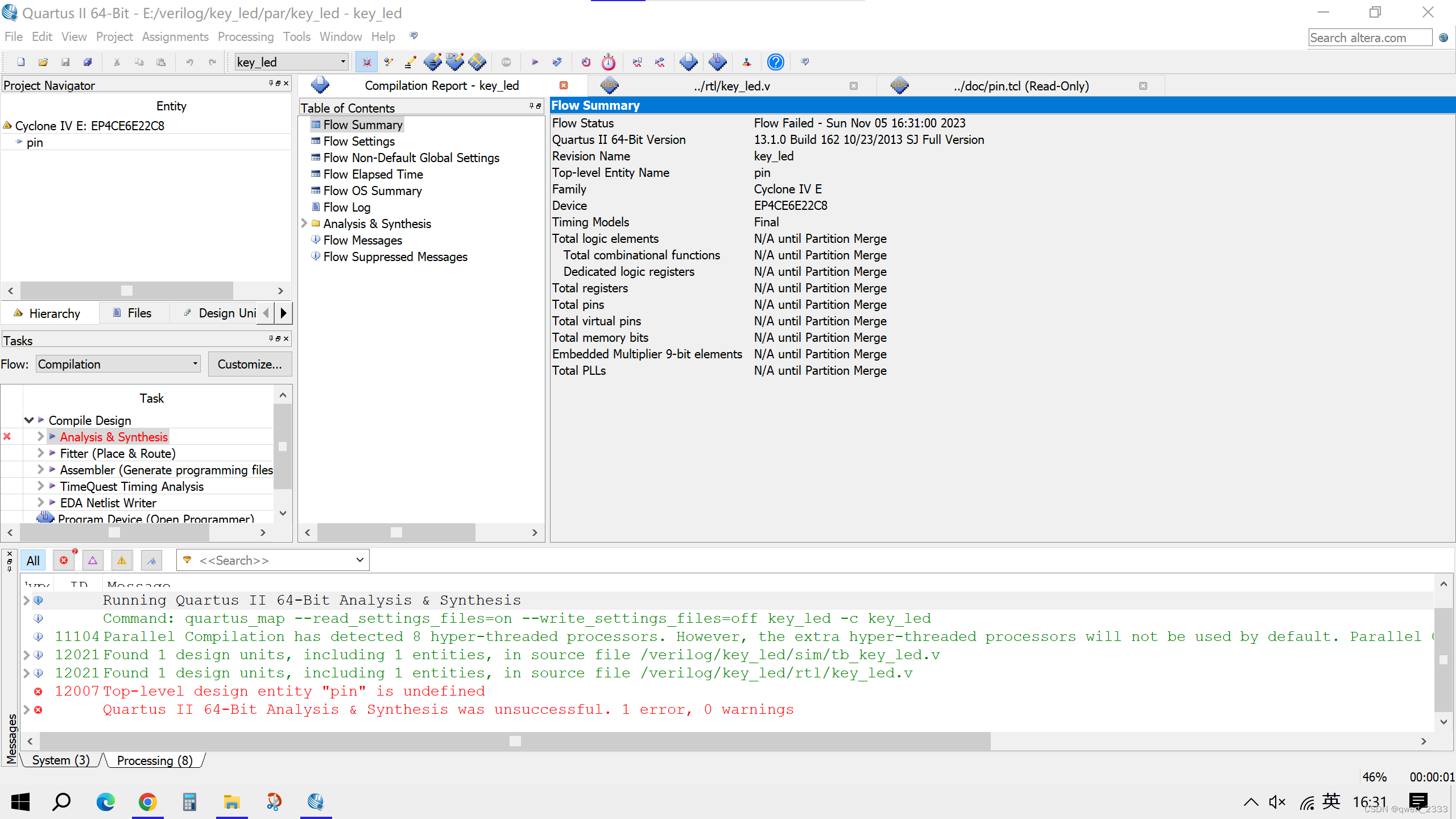

QuartusII13.1有时会在Start Analysis & Synthesis时莫名其妙地报这个错误

Error (12007): Top-level design entity "pin" is undefined

Error: Quartus II 64-Bit Analysis & Synthesis was unsuccessful. 1 error, 0 warnings

然后我百思不得其解,明明我只是入门FPGA,耍一耍QuartusII13.1,这个pin.tcl也装上了,但是这个软件却认为我没有把这个装上去。

二、解决路径

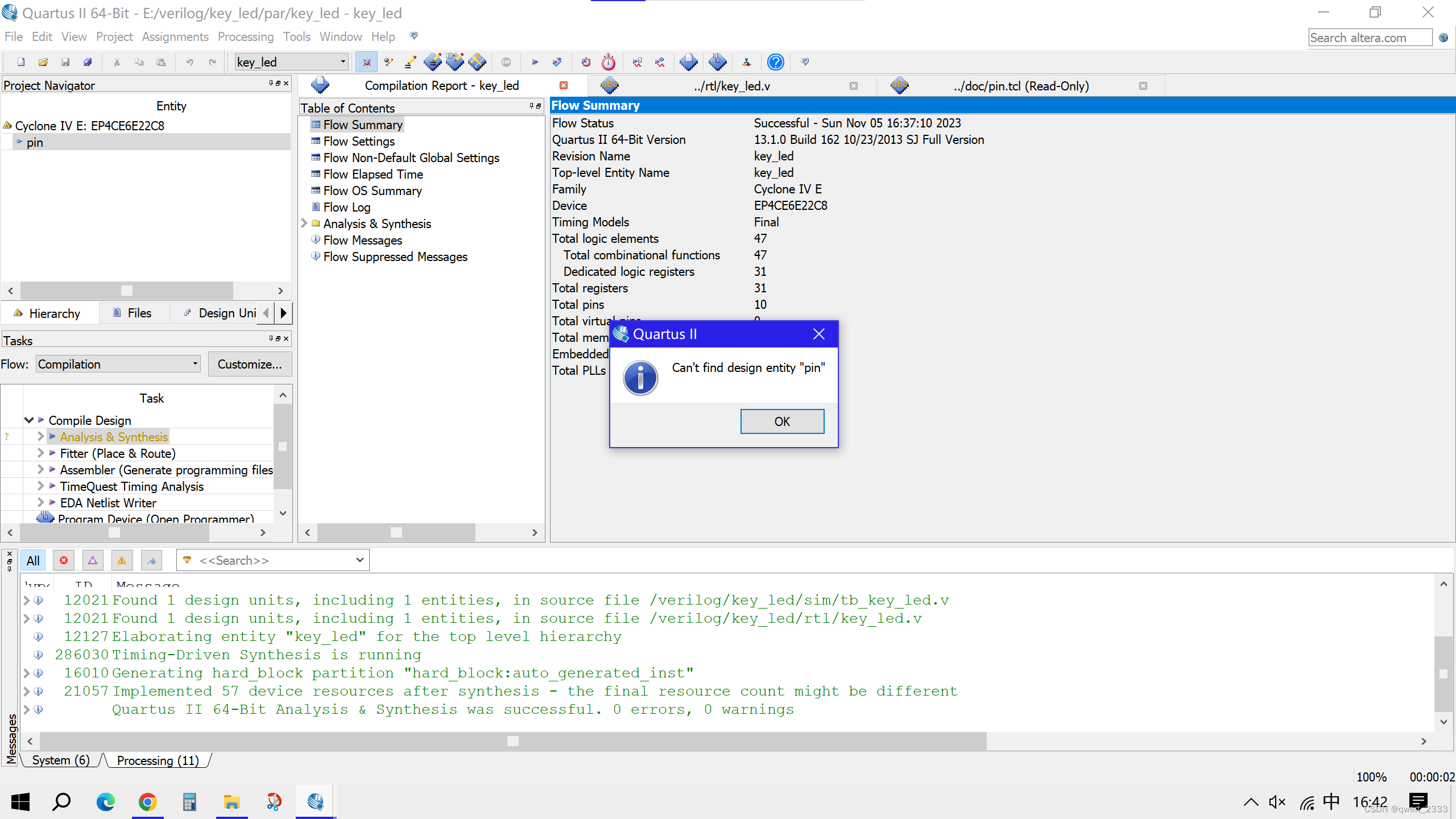

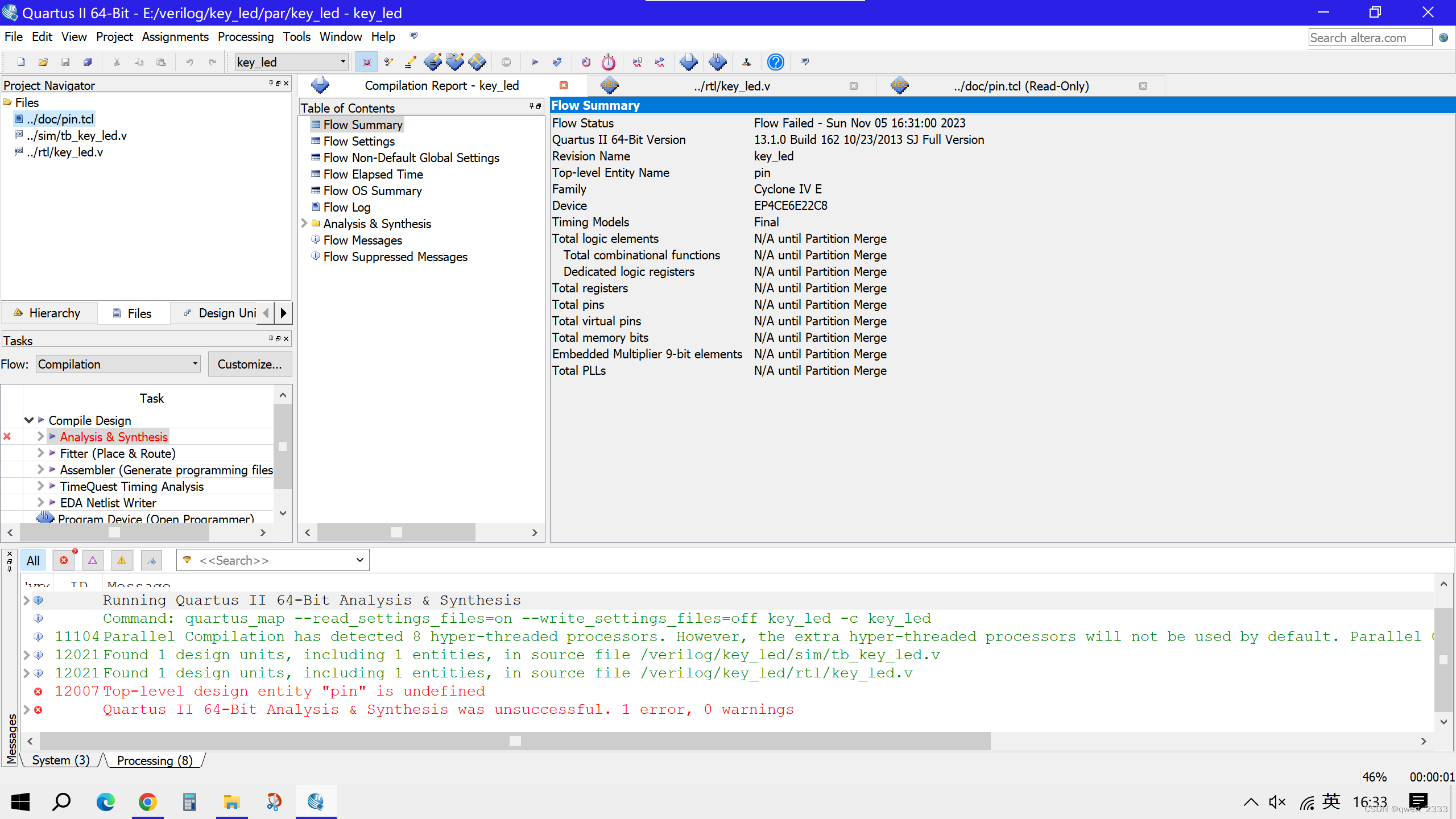

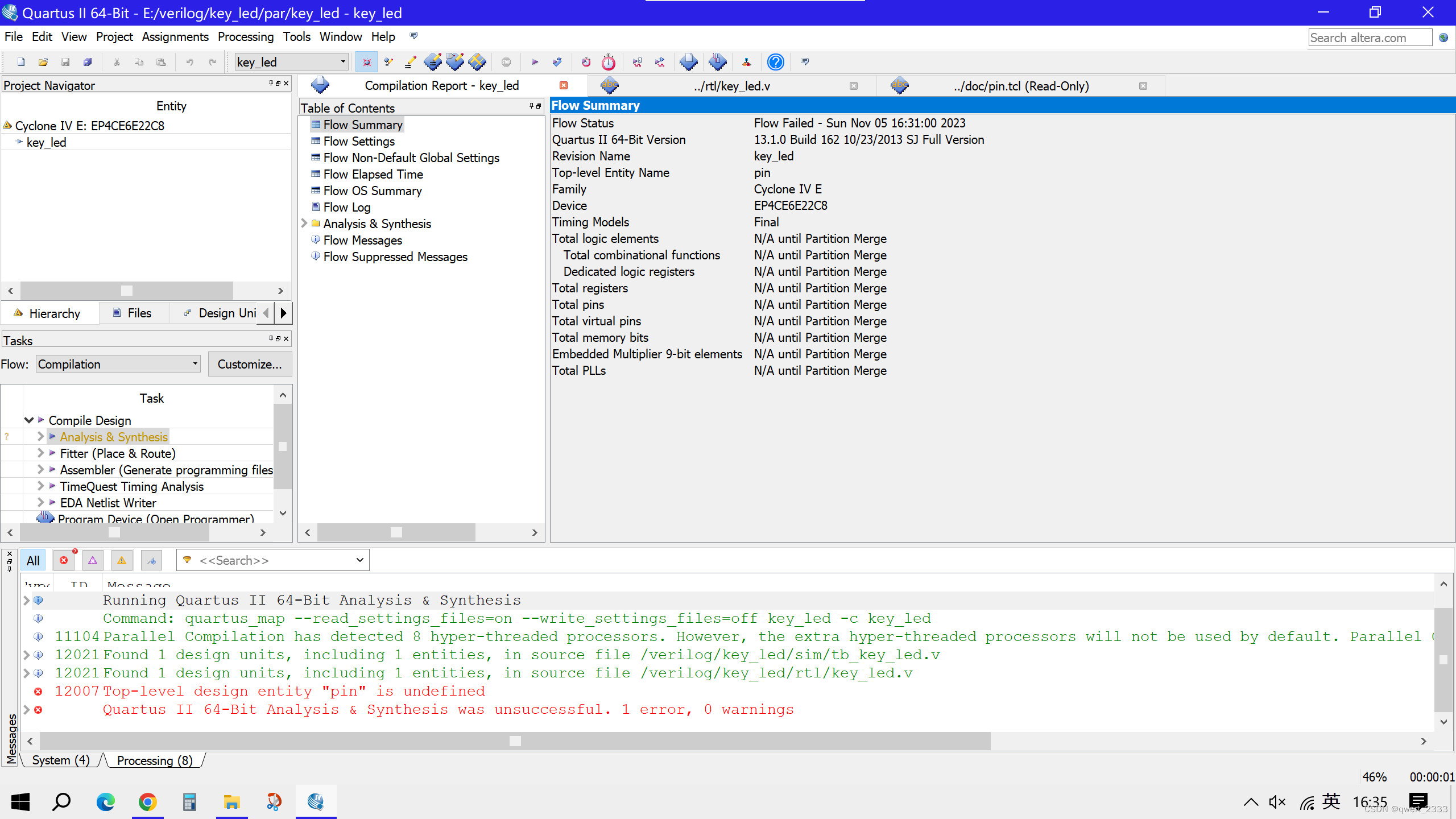

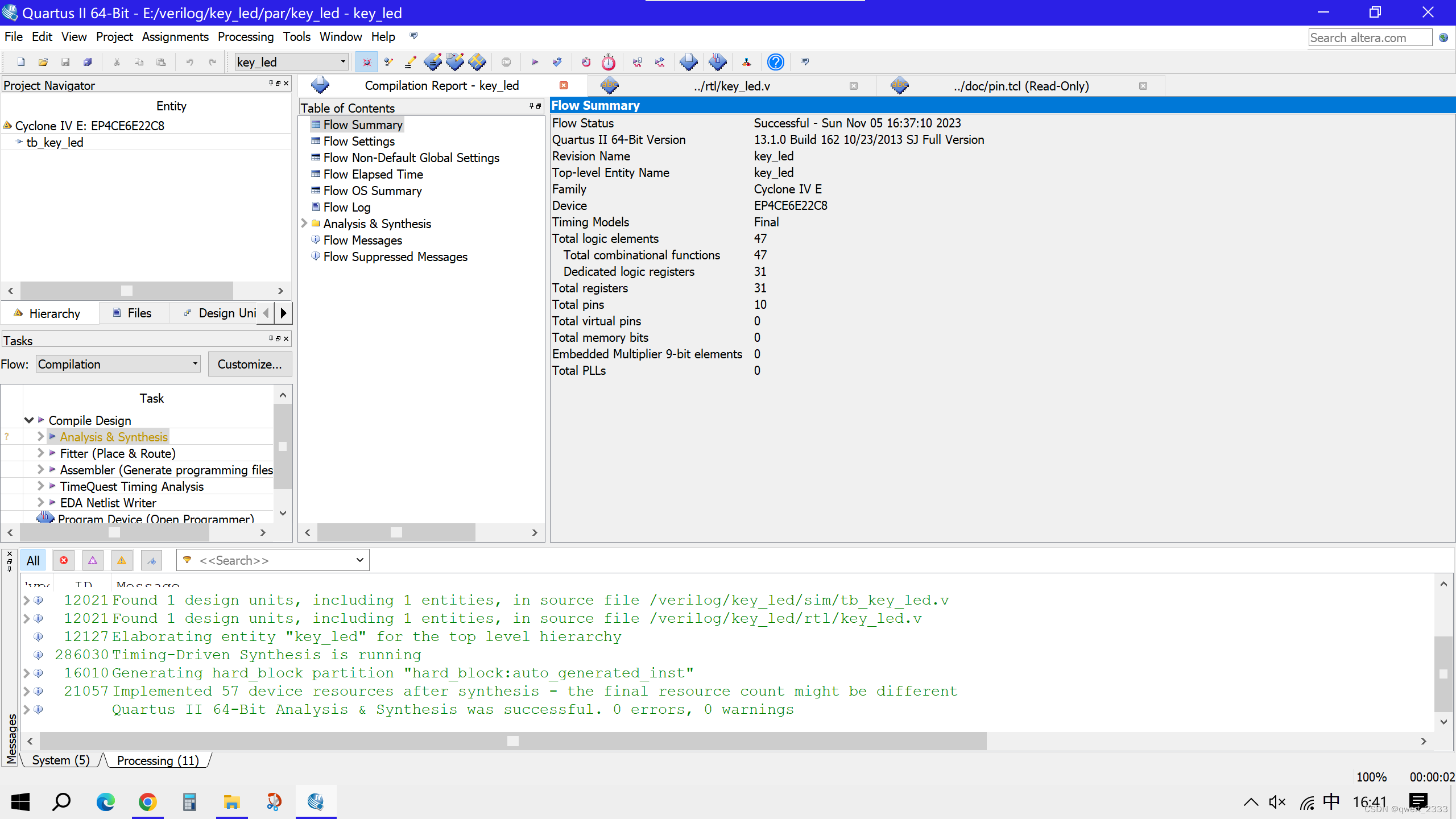

后来我又重新新建了一个同样的工程,十分参考正点原子的放置格式,结果就成功了,对比可知hierarchy的文件不一样了,因此推断更改掉顶层文件应该就可以解决这个问题了。

三、解决方法

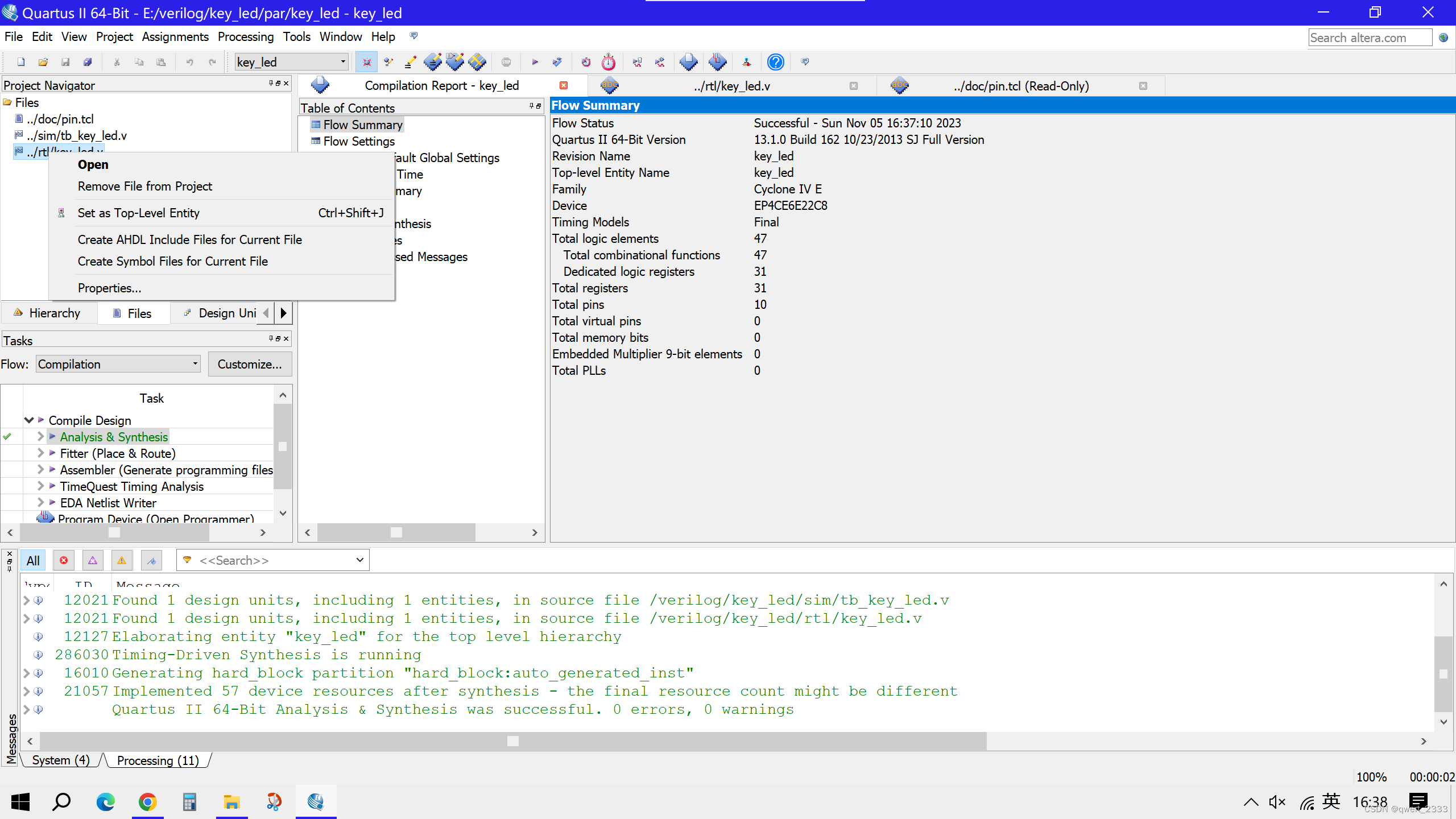

所以回到file那里右键key_led.v文件,选择set as top-level entity就行了,或者直接快捷键ctrl+shift+j即可解决。

解决问题!

6万+

6万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?