在电子工程、通信工程、自动控制、遥测控制、测量仪器、仪表和计算机等技术领域,经常需要用到各种各样的信号波形发生器。随着集成电路的迅速发展,用集成电路可很方便地构成各种信号波形发生器。用集成电路实现的信号波形发生器与其它信号波形发生器相比,其波形质量、幅度和频率稳定性等性能指标,都有了很大的提高。

波形发生器是能够产生大量的标准信号和用户定义信号,并保证高精度、高稳定性、可 重复性和易操作性的电子仪器。函数波形发生器具有连续的相位变换、和频率稳定性等优点,不仅可以模拟各种复杂信号,还可对频率、幅值、相移、波形进行动态、及时的控制,并能够与其它仪器进行通讯,组成自动测试系统,因此被广泛用于自动控制系统、震动激励、通讯和仪器仪表领域。

2硬件电路设计

本方案是基于AT89C52与DAC0832的单缓冲方式接口电路来设计。单缓冲式接口电路具有过程简单,容易实现。由于本设计运用汇编的编程语言,导致用独立式键盘来实现简单控制。本方案所产生的信号频率稳定性高,精确度高。而且在硬件方面它所选的元器件比较常见。其主要流程图和模块如图1所示。

![]()

![]()

![]()

![]()

图1软硬件结合设计框图

2.1主要芯片介绍

2.1.1单片机AT89C52

AT89C52是一个低电压,高性能CMOS 8位单片机,片内含8k bytes的可反复擦写的Flash只读程序存储器和256 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,

![]()

![]()

片内置通用8位中央处理器和Flash存储单元,AT89C52单片机在电子行业中有着广泛的应用。

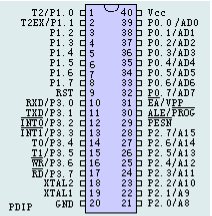

AT89C52为8位通用微处理器,采用工业标准的C51内核,在内部功能及管脚排布上与通用的8xc52相同,其主要用于会聚调整时的功能控制。功能包括对会聚主IC 内部寄存器、数据RAM及外部接口等功能部件的初始化,会聚调整控制,会聚测试图控制,红外遥控信号IR的接收解码及与主板CPU通信等。图2为AD89C52单片机的管脚图。

图2 AT89C52管脚图

其各管脚功能为:

P0口:P0口是一组8位漏极开路型双向I/O 口,也即地址/数据总线复用口。作为输出口用时,每位能吸收电流的方式驱动8个TTL逻辑门电路,对端口P0写“1”时,可作为高阻抗输入端用。在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。在Flash 编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。

P1口:P1是一个带内部上拉电阻的8位双向I/O口,P1的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑门电路。对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口。作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流(IIL)。与AT89C51 不同之处是,P1.0 和P1.1还可分别作为定时/计数器2 的外部计数输入(P1.0/T2)和输入。

P2口:P2 是一个带有内部上拉电阻的8 位双向I/O 口,P2的输出缓冲级

![]()

![]()

可驱动(吸收或输出电流)4个TTL逻辑门电路。对端口P2写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口,作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流(IIL)。在访问外部程序存储器或16位地址的外部数据存储器时,P2口送出高8位地址数据。在访问8位地址的外部数据存储器(如执行MOVX @RI 指令)时,P2口输出P2锁存器的内容。Flash 编程或校验时,P2亦接收高位地址和一些控制信号。

P3口:P3口是一组带有内部上拉电阻的8位双向I/O口。P3口输出缓冲级可驱动(吸收或输出电流个TTL逻辑)4门电路。对P3口写入“1”时,它们被内部上拉电阻拉高并可作为输入端口。此时,被外部拉低的P3口将用上拉电阻输出电流(IIL)。P3口除了作为一般的I/O口线外,更重要的用途是它的第二功能。P3口还接收一些用于Flash闪速存储器编程和程序校验的控制信号。

RST:复位输入。当振荡器工作时,RST引脚出现两个机器周期以上高电平将使单片机复位。

ALE/PROG:当访问外部程序存储器或数据存储器时,ALE(地址锁存允许)输出脉冲用于锁存地址的低8位字节。一般情况下,ALE仍以时钟振荡频率的1/6输出固定的脉冲信号,因此它可对外输出时钟或用于定时目的。要注意的是:每当访问外部数据存储器时将跳过一个ALE脉冲。对Flash存储器编程期间,该引脚还用于输入编程脉冲(PROG)。如有必要,可通过对特殊功能寄存器(SFR)区中的8EH 单元的D0位置位,可禁止ALE操作。该位置位后,只有一条MOVX和MOV指令才能将ALE激活。此外,该引脚会被微弱拉高,单片机执行外部程序时,应设置ALE 禁止位无效。

PSEN:程序储存允许(PSEN)输出是外部程序存储器的读选通信号,当AT89C52由外部程序存储器取指令(或数据)时,每个机器周期两次PSEN有效,即输出两个脉冲。在此期间,当访问外部数据存储器,将跳过两次PSEN信号。

EA/VPP:外部访问允许。欲使CPU仅访问外部程序存储器(地址为0000H—FFFFH),EA 端必须保持低电平(接地)。需注意的是:如果加密位LB1被编程,复位时内部会锁存EA端状态。如EA端为高电平(接Vcc端),CPU则执行内部程序存储器中的指令。Flash 存储器编程时,该引脚加上+12V的编程允许电源Vpp,当然

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?