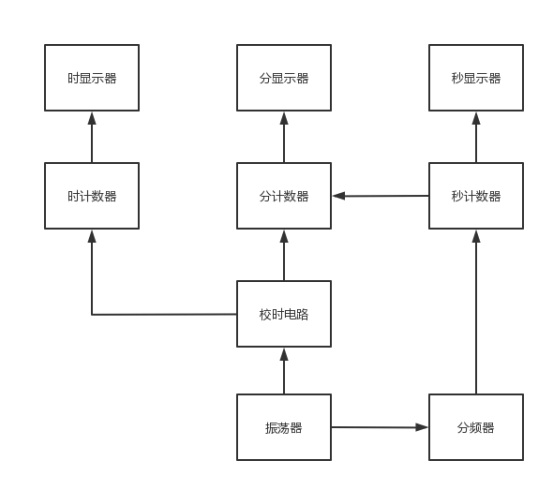

设计框图

数字钟电路的基本组成框架图如图一所示,它主要由多谐振荡器、计数器、译码器和数码显示器4个部分组成。

图一 数字钟电路的基本组成(方框图)

2、设计方案

数字钟是一个将“时”,“分”,“秒”显示于人的视觉器官的计时设计装置。他的计时周期为24小时,显示满刻度为23时59分59秒。因此,一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”,计数器、校时电路和振荡器组成。数字钟实际上是一个对标准频率进行计数的计数电路,由于计数的起始时间不可能与标准时间一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定,通常使用石英晶体振荡器电路。

三、单元电路设计与参数计算1、单元电路的设计

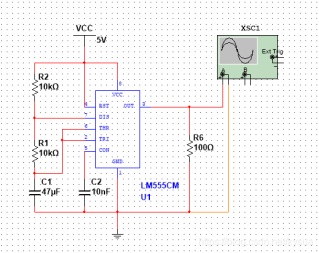

1.1时钟模块

考虑到数字钟对精度要求细撸适敝幽?槭怯�555计时器组成的振荡电路,其在电路中直接产生频率为1HZ的脉冲信号。图3.1.1为由555计时器所构成的。

图3.1.1时钟模块

1.2分频计数器

设计的60和24进制加法计数器都大于一个74LS160N的计数范围,所以需要级联。当且仅当秒的个位计数到10的瞬间,即输出为1010时,向本位发送一个清零信号,并同时向十位发送一个进位脉冲。但由于74LS160N的清零方式为异步清零,这种清零方式会导致清零的不可靠。所以必须要把脉冲调整到一个较低的周期,才会产生有效地清零和进位信号。两片74LS160N的预置是同步的,利用预置端的ABCD四个端口来实现清零。把A-D接地后,当置入控制器LOAD为低电平时,在CLK上升沿作用下,输出端QA-QD会与数据输入端A-D相一致。通过采用预置的方式,可以确保清零的稳定。但为了使清零和进位同步进行,在清零的输出端需要引出一根线,加上非门引入下一级计数器的输入端。这种可以实现多重清零的方式,也可以实现24进制用10进制显示,而且清零和进位的可靠性与同步性得到了极大地提高。

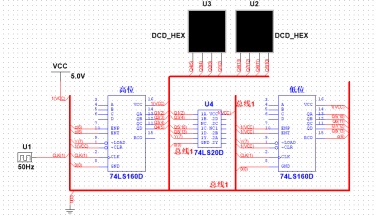

1.3秒计数器

由于时钟模块分频后可直接产生1Hz的标准脉冲时钟信号,所以可以直接把所得的1Hz信号作为秒位计数器的时钟信号。使用两片同步加法计数器74LS160N构成60进制加法计数器作为秒计时器,同时在设计的时候,也应用到了74LS20N这个双4输入与非门集成电路,其在电路中充当与非门的作用。在秒的个位计数到10的瞬间,向十位发送一个进位脉冲。秒的十位加法计数器在计数到6的瞬间,向74LS20N发送清零信号。这样就构成了一个级联而形成的60进制带进位与清零的加法计数器。图3.1.3为秒计时器的电路图。

图3.1.3秒计数器

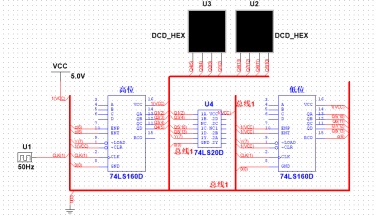

1.4分计数器

按照同样的方法,可以构成分位的计数器。图3.1.4为秒计时器的电路图。

图3.1.4分计数器

1.5时计数器

秒分频计数器采用两片74LS160和一片74LS20组成,74LS160是十进制计数器,也就是说只能记住十个数字,计数完成后自动清零,同时产生一个进位信号,而74LS20内部由两组4输入与非门组成;秒分频计数器是60进制的计数器当低位的

![]()

变为0011的同时高位的

![]()

变为0010时,将高位

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?