用于信号处理应用的连续时间Sigma Delta ADC中低功耗压控振荡器使能量化器的设计

摘要

利用Tanner EDA工具在180nm CMOS技术下,对连续时间Sigma Delta ADC中基于低功耗压控振荡器(VCO)的量化器进行了精确设计。所提出的架构包括环路滤波器、VCO量化器以及反馈路径中的数模转换器(DAC)。所设计的环路滤波器中使用的运算放大器(OPAMP)提供40dB增益、70度相位裕度和79.06MHz的单位增益带宽,功耗为3毫瓦。通过VCO量化器环路结构降低了VCO的偶次谐波。高阶环路滤波器采用有源电阻和基于电容的积分器实现,VCO量化器则使用15级多级环形振荡器和D触发器(DFF)寄存器实现,具有低相位噪声的优点,工作频率范围为100千赫。整个电路的显著功耗为3毫瓦。

关键词

运算放大器(OPAMP),连续时间Sigma Delta模数转换器(ADC),非理想性问题,量化器

一、引言

混合集成电路设计趋势正在迅速发展,因为它带来了许多进步,并实现了在硅片上高效集成数字逻辑和模拟组件,从而将多种信号处理任务转移到数字域。这一现象的一个显著应用体现在数据转换器领域,即数模转换器(DACs)、模数转换器(ADCs),其中混合信号设计正积极研究连续时间 ∑∆ ADC架构。一种新兴的模数转换器结构——连续时间 ∑∆ ADC结构,目前已成为众多研究领域的焦点,能够提供出色的功率效率[5]。

传统的模拟连续时间∑∆模数转换器在环路中包含一个作为量化器的高速、低噪声比较器电路,因此在纳米尺度技术中带来了设计挑战。在纳米级工艺下,由于随着工艺尺寸缩放导致电源电压降低,模数转换器的设计变得更加困难,并需要复杂的模拟功能模块。[8]而基于压控振荡器(VCO)的量化方式可以在CMOS技术中轻松实现,并适用于高速应用。[5]

由于具有独特且简化的信号处理特性,压控振荡器实现的量化已变得非常流行。

近年来,已提出多种技术来缓解由压控振荡器非线性调谐曲线引起的失真。基于压控振荡器的ADC主要使用数字电路,从而有利于工艺尺寸缩放。连续时间 ∑∆模数转换器正在成为在无线电、无线接收机、音频、通信等众多应用中实现模数转换器的先进研究方向。[6]

本文的其余部分组织如下:第二部分详细介绍了启用压控振荡器的架构概述,并讨论了各种提出设计的重要性。第三部分介绍了基本电路设计和基于压控振荡器的模数转换器架构。第四部分讨论了所提出的基于压控振荡器的连续时间 ∑∆ ADC拓扑结构。第五部分列出了先前提出工作的预期结果和成果,结论在第六部分给出。

II. 连续时间∑∆模数转换器的简要概述

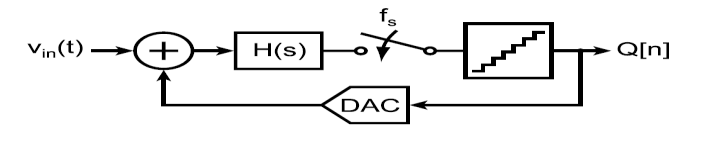

连续时间∑∆模数转换器(ADC)最显著的优势在于其固有的抗混叠滤波能力。这种滤波能力的实现是因为其输入模拟信号首先被送入连续时间环路滤波器,然后再由压控振荡器量化器进行采样,如图1.(a)所示;而在离散时间 ∑∆模数转换器中,输入模拟信号在送入环路滤波器之前就已经完成采样,如图1.(b)所示。对于其他任何类型的离散时间模数转换器(如逐次逼近型、流水线型、闪速型等)也是如此,采样总是在ADC输入之前发生。

连续时间 ∑∆模数转换器固有的抗混叠滤波能力也已被广泛用作在无线系统中修改实际滤波和编码数字比特的手段。

然而,在相同技术下,连续时间∑∆模数转换器的时钟频率可以提高一个数量级,而不会带来显著的性能损失。

不幸的是,设计抗混叠滤波器会引入失真和最小噪声,其缺点是面积消耗和高功耗。最近发表的连续时间滤波器发现,功耗可能根据所需的噪声、线性度和带宽从10毫瓦到超过100毫瓦不等。同时,有源滤波器的面积可能根据滤波器阶数从0.1mm²到超过0.1mm²,广泛变化。鉴于设计连续时间 ∑∆模数转换器时涉及的显著功耗和面积开销,如表I所示。

| 参考文献 | 带宽(MHz) | 功耗(mW) | 面积(平方毫米²) |

|---|---|---|---|

| [5] | 10 | 66 | - |

| [6] | 10 | 16 | 0.36 |

| [9] | 20 | 87 | - |

| [11] | - | 20 | 8.6 |

| [12] | 1.1 | 62 | 5.76 |

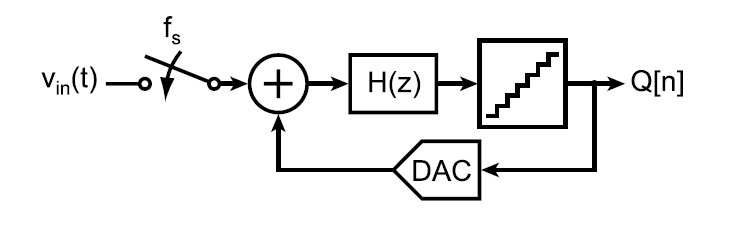

如图2所示,展示了主流ADC拓扑结构的分辨率与带宽调查。该图显示了不同ADC拓扑结构之间的比较,展示了有效位数(ENOB)与输入带宽的对比研究。

III. 系统架构

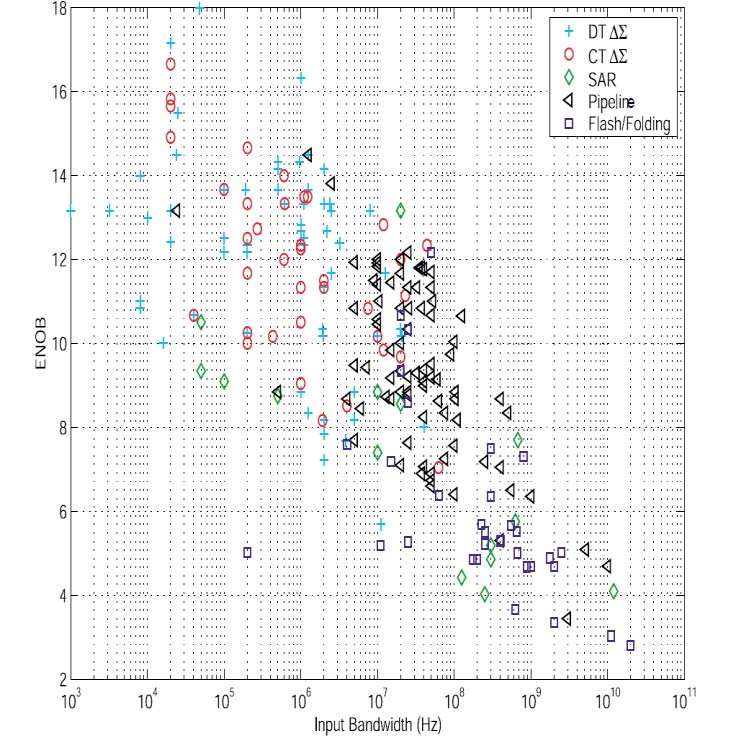

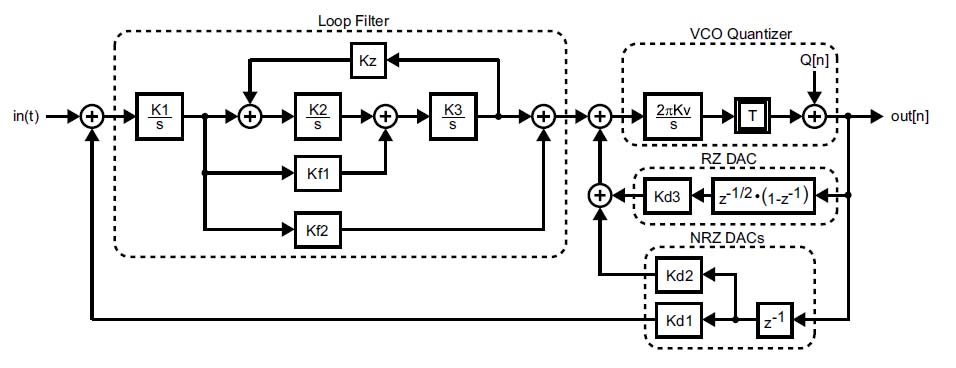

连续时间∑∆模数转换器的系统架构如图3所示。该模数转换器由环路滤波器、基于压控振荡器的量化器和反馈数模转换器组成。低通环路滤波器提供噪声整形和线性度,从而在具有优异的高能效特性的同时降低量化噪声。压控振荡器的作用是将模拟输入电压或电流转换为期望的输出频率,即Vout = K Vin,因此基于压控振荡器的模数转换器能够实现高速运行并具有可忽略的延迟。

在数模转换器的计数部分,每个相位输出连接到一个 DAC单元,并共同连接以提取反馈信号。非归零和归零 DAC主要用于压控振荡器量化器中以管理单调性。

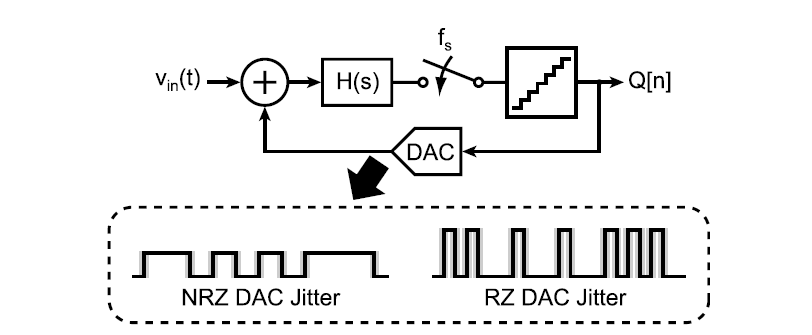

尽管具有信号处理优势,但由于DAC电荷调制直接出现在ADC输入端(如图4所示),连续时间 ∑∆模数转换器也存在对时钟抖动高度架构敏感性的问题。由于RZ DAC 在每次采样时的调制超过DAC电荷的两倍,因此其抖动敏感性远高于NRZ DAC,从而导致信噪比下降。

最近的研究表明,通过采用多位量化器和非归零反馈 DAC实现,可显著降低时钟抖动引起的信噪比退化[5,10]。

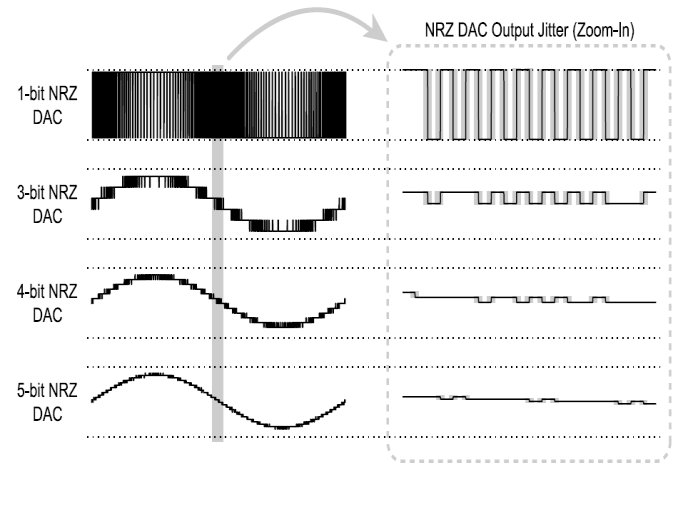

图5显示,抖动仅调制逐样本发生变化的最低有效位的 DAC电荷。增加DAC位数可减少其引入的误差电荷。因此,在这些高度数字化环境中,连续时间∑∆模数转换器的混合信号设计在最新深亚微米技术下实现高分辨率、带宽和功率效率时将面临新的挑战。[3]

IV. 提出的连续时间∑∆模数转换器拓扑结构

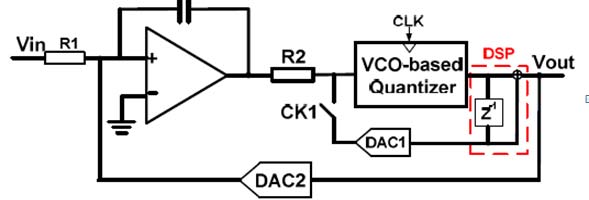

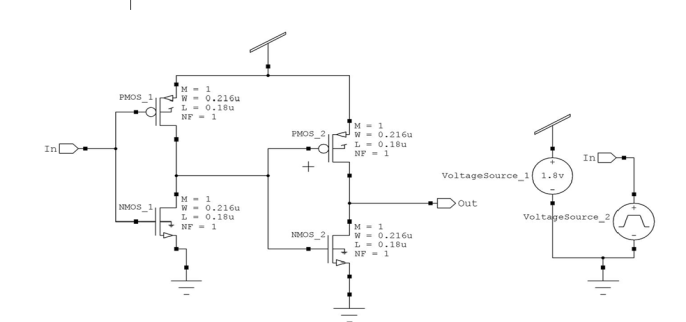

在模数转换器(ADC)中,压控振荡器(VCO)现在已成为混合信号设计中备受关注的课题。设计了一种基于连续时间∑∆ ADC的压控振荡器量化器原型,用于将模拟输入信号转换为数字数据,从而降低非线性。环路滤波器、压控振荡器量化器和数模转换器等模块采用2.5V和1.8V的工作电压进行设计。图6展示了所提出的基于连续时间∑∆ ADC的VCO框架。

A. 环路滤波器

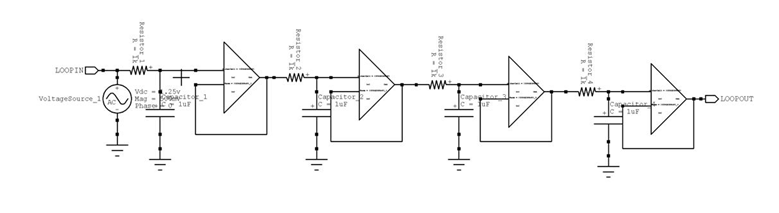

在 ∑∆模数转换器中,噪声整形特性由环路滤波器进行分析。环路滤波器在其带宽范围内根据增益限制来抑制压控振荡器的非线性特性。随着环路滤波器阶数的增加,可以获得更高阶的噪声整形能力。本文采用电阻电容积分器实现四阶环路滤波器,如图7所示。所使用的积分器有三种不同的拓扑结构,分别为有源RC、Gm‐C和MOSFET‐电容积分器,其中由于有源RC积分器具有良好线性度和更高信号摆幅,因此更具优势。

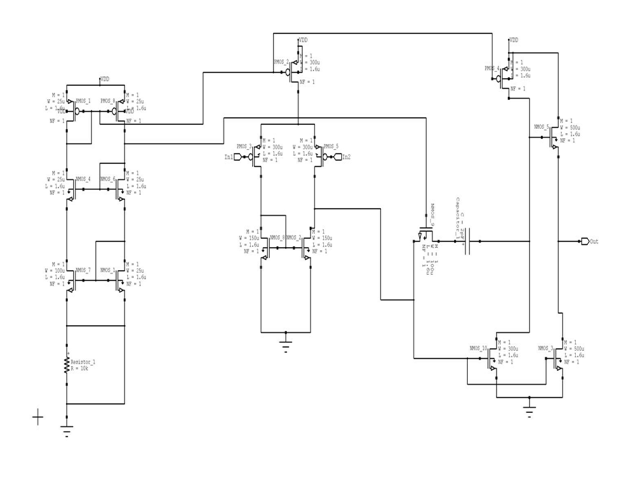

在积分器中,放大器采用两级运算放大器实现,第一级为差分级,第二级为共源级。从输入到共源级的路径通过耦合电容 Cc连接,如图8所示。

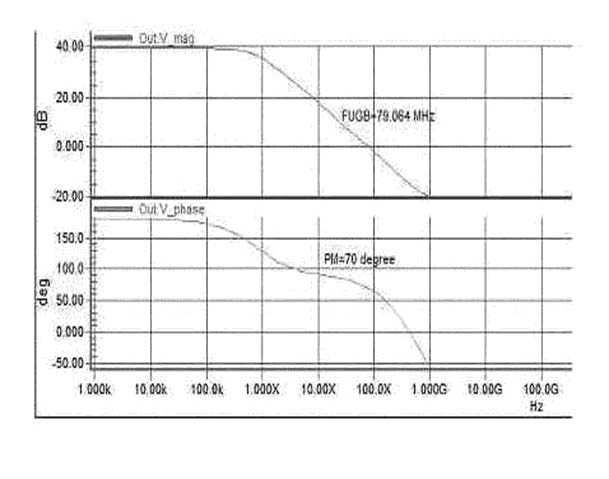

使用Tanner EDA工具在0.18微米CMOS工艺下对两级运算放大器进行仿真得到的结果如图9所示。

两级运算放大器的设计要求是相位裕度必须大于 60°,以实现高稳定性。该运算放大器在1.8伏特功率(VDD)下实现了70°的相位裕度、40分贝的直流增益和79.06兆赫的单位增益带宽。

B. 压控振荡器量化器

基于VCO的ADC架构属于时间域ADC。基于压控振荡器的量化器将模拟输入信号转换为数字形式的数据。压控振荡器产生一个连续时间信号,其信号频率与平均模拟输入信号成正比。量化器在每个采样周期对信号进行量化,并生成相应的数字输出。基于VCO的ADC主要有两种架构:一种是计数器型架构,另一种是相位检测器型架构。计数器型架构存在诸多问题,例如由于计数器复位问题导致噪声整形特性减弱、高功耗和面积较大。一种避免计数器复位问题的方法是使用1位量化器替代计数器。此时用两个 D触发器(D‐FF)和一个异或门代替计数器,这些电路足以在VCO结构的各个相位中完成一位量化。

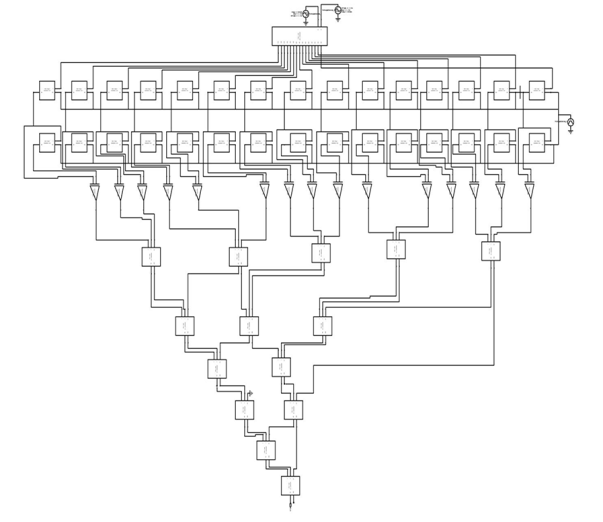

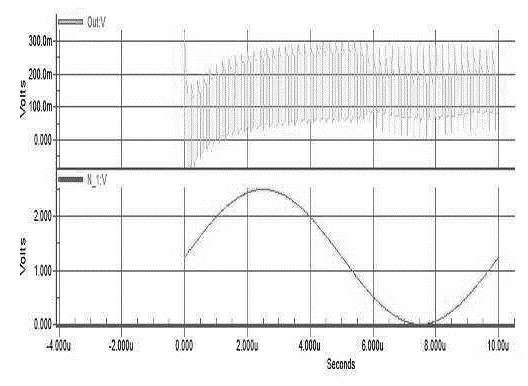

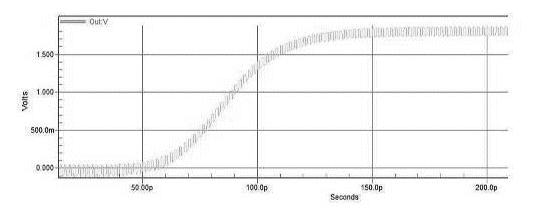

此处VCO量化器由15级环形振荡器(RO)、两组D触发器阵列和一个异或门阵列组成,如图10所示。对系统设计人员而言,满足面积、功耗和RO电路速度等规格指标是一项重大挑战。为了实现VCO电路的精确性能,必须获得正确的幅度和相位噪声。D触发器限制了VCO的先前状态,这些状态通过异或门进行比较,从而检测VCO的跳变。最终输出等于处于跳变状态的元件数量,该数量由VCO的控制电压控制。该VCO量化器在0.18微米CMOS工艺下进行仿真,工作频率为100KHz,输入电压和1.25V幅度偏移如图11所示。功耗为3毫瓦。

C. 反馈数模转换器

反馈路径的首要组成部分是1位DAC,它将输出的数字信号转换为模拟信号。DAC的主要任务是使ADC的数字输出等于模拟输入,从而使积分器的输出可能为零值。Σ‐Δ转换器使用多位量化器和多位数模转换器(DAC)来重建模拟信号。对于高分辨率DAC而言,精度是其面临的主要问题之一,为此采用单比特系统以克服精度问题。在1位 DAC中,线性度通过参考信号之间切换的精度来检验,高开关精度可使系统非常线性。图12显示了采用1.8V供电电压的1位DAC的基本原理结构,其中一个反相器的输出作为另一个反相器的输入,系统接收脉冲输入并获得相应的模拟输出,且具有如图13所示的低功耗特性。

V. 实验结果

采用Tanner EDA工具,在0.18微米CMOS工艺下集成了系统各组成部分,设计了一款西格玛‐德尔塔模数转换器。其中关键组件运算放大器具有40dB的开环增益和70°的相位裕度,有助于积分电路的稳定工作。基于该运算放大器设计并仿真了一个有源RC四阶环路滤波器。随后设计了一个高速压控振荡器量化器,采用15级环形振荡器,并结合D触发器阵列和异或门。所提出的压控振荡器量化器在100千赫采样频率和1.25伏特幅度下实现,功耗低至3毫瓦,产生相应输出结果后送入反馈路径中的一位数模转换器(DAC)电路。该过程反复迭代,最终在输出端获得数字信号脉冲。表II中列出了启用压控振荡器的架构比较结果,展示了与先前工作的各项对比数据,其折线图如图14所示。我们还提供了压控振荡器功耗与不同技术之间的对比图表,便于快速了解。

| Ref. | 技术 (μm) |

操作频率(兆赫)

VCO | VCO 功率 (mW) | Gain (dB) | 相位裕度 (度) | 电源电压 (V) |

Order of loop

滤波器 |

|---|---|---|---|---|---|---|---|

| [1] | 0.18 | 2.5 | - | - | - | 1.8 | - |

| [6] | 0.09 | 0.1–4 | 1.3 | 58 | 55 | - | 1 |

| [9] | 0.13 | 225 | 18 | 63 | 55 | 1.5 | 4 |

| [10] | 0.13 | 10 | 20 | 50 | - | 1.2 | - |

| [11] | 0.13 | 640 | 20/18 | - | - | 1.2 | 3 |

| This work | 0.18 | 100千赫 | 3 | 40 | 70 | 1.8 | 4 |

VI. 结论

从上述结果可以看出,基于压控振荡器的高性能低功耗西格玛‐德尔塔模数转换器架构已在纳米级CMOS技术范围内被精确设计。该方法通过环路滤波器40 dB的增益降低了失真,从而自动改善了压控振荡器非线性。与传统工作关注高分辨率和信噪比相比,上述结果和讨论表明,在100千赫频率下,噪声抑制能力显著提高,同时线性度也得到增强。采用压控振荡器的量化器在180纳米CMOS技术下的计算功耗为3毫瓦。

369

369

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?