1.DAG(Directed Acyclic Graph)

许多重要的局部优化技术都是从将基本块转换为DAG[15]开始的。例如,基本的代码块,对应的DAG如图9所示。

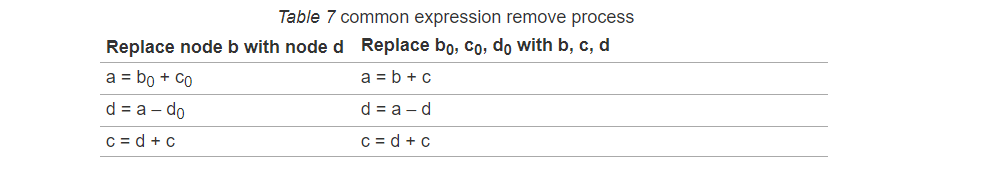

如果b不在块退出时活动,那么我们可以执行“common expression remove”,如下表所示。

删除b后,从底部到顶部遍历DAGs(按深度优先顺序搜索遍历二叉树),得到上表第一列。

可以想象,“公共表达式删除”可以应用于IR或机器码中。

DAG类似于一个树,其中操作码是节点,操作数(寄存器和const/immediate/offset)是叶子。它也可以用list表示为树中的前缀顺序。例如,(+ b, c), (+ b, 1)是IR DAG表示。

除了DAG优化之外,编译器书籍[15]的8.5.5节还提到了“kill”寄存器。该优化方法也应用于llvm的实现。

2.Instruction Selection

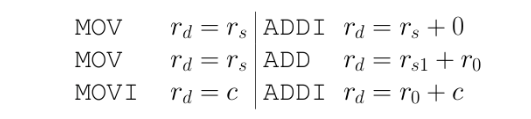

后台的主要功能是在指令选择阶段将IR代码转换为机器码,如图10所示。

Fig.10:对应的机器指令

对于机器指令的选择,最好的解决方案是用DAG表示IR和机器指令。为了简化视图,在图11中跳过了寄存器叶。rj + rk是IR DAG表示法(用于符号表示法,而不是

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

726

726

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?