28335特性介绍

- 高性能静态CMOS技术

高达150MHZ(6.67ns的周期时间);1.9V / 1.8内核 ,3.3V I/O设计

- 高性能32位CPU

IEEE-754单精度浮点单元

哈佛总线结构

快速中断响应处理

使用C/C++ 和汇编语言

- 6通道的DMA(用于ADC、McBsp、ePWM、XINTF和SARAM)

- 16位或32位外部接口XINTF

- 片上存储器

256K*16 Flash 34K*16 SARAM

8K*16 Boot ROM(支持软件引导模式SCI、SPI、CAN、I2C、McBSP、XINTF和并行IO)

- 时钟和系统控制

支持动态锁相环PLL; 片载振荡器; 安全装置定时模块

- GPIO0~GPIO63引脚可以连接到八个外部内核中断其中的一个

- 支持58个外设中断的PIE模块(外设中断扩展)

- 3个32位定时器

- 串行端口外设

2个局域网控制器CAN模块

3个SCI模块(SCIA、SCIB、SCIC)

2个McBSP模块(可配置为SPI)——一个SPI,一个I2C

- 12位,16通道模数转换ADC

80ns转化率;2*8通道复用输入器;两个采样保持;单一/同步转换

- 字节序:小端模式

- 温度选项:A:-40~85 S:-40~125 Q:-40~125

冯诺依曼结构和哈佛总线结构区别:

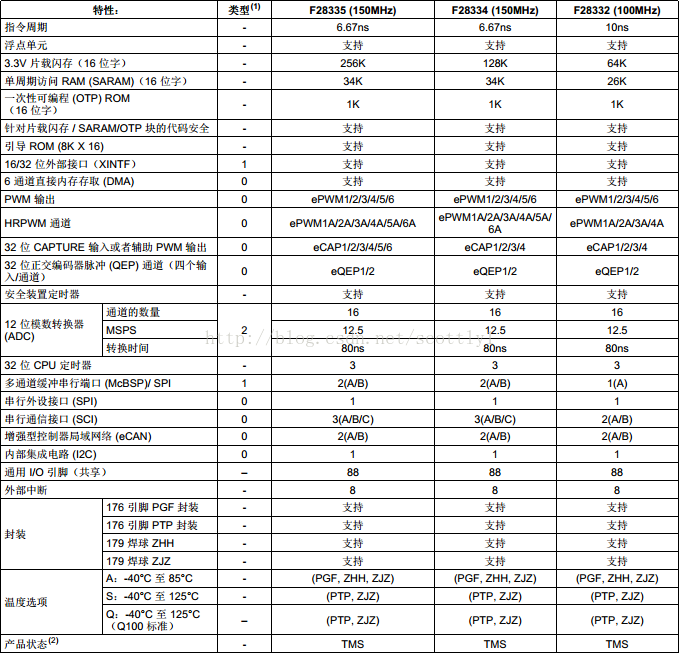

下面来一张官方的表:

JTAG:

2485

2485

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?