1、JTAG 基本原理

JTAG是Joint Test Action Group的缩写,它是一种国际标准测试协议,主要用于芯片或印制电路板的边界扫描和编程。

JTAG接口是一种用于连接和调试嵌入式系统的标准接口。

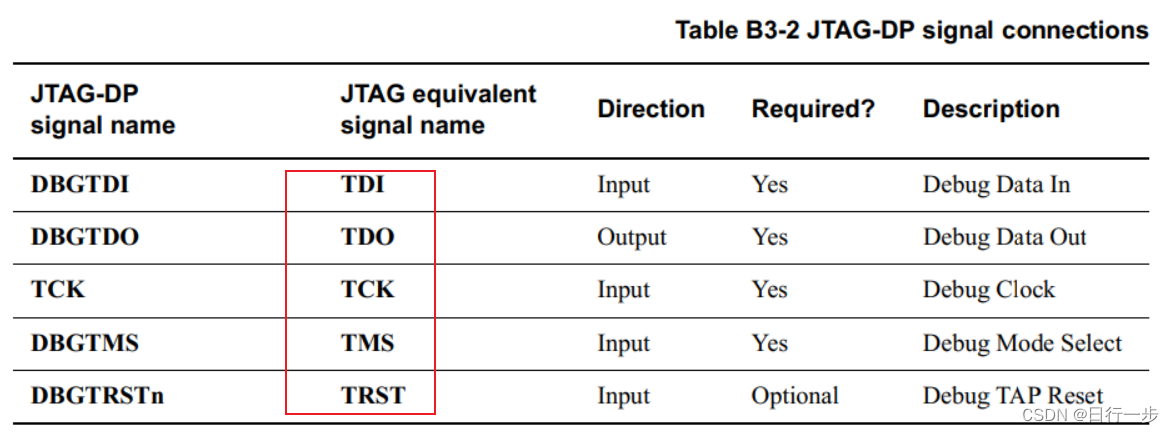

1.1、JTAG接口包括以下几个信号:

- TMS(Test Mode Select):用于设置测试模式和测试状态机的状态。通过 TMS 信号,可以控制 TAP 在不同的状态间相互转换。TMS 信号在 TCK 的上升沿有效。

- TCK(Test Clock):用于提供时钟信号,控制测试状态机的运行。

- TDO(Test Data Out):用于从测试状态机中输出数据。

- TDI(Test Data Input):用于向测试状态机输入数据。

- TRST(Test Reset Input): RST可以用来对TAP Controller进行复位(初始化)。不过这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。 因为通过 TMS 也可以对 TAP Controller 进行复位(初始化)。

参考:debug_interface_v5_2_architecture_specification.pdf

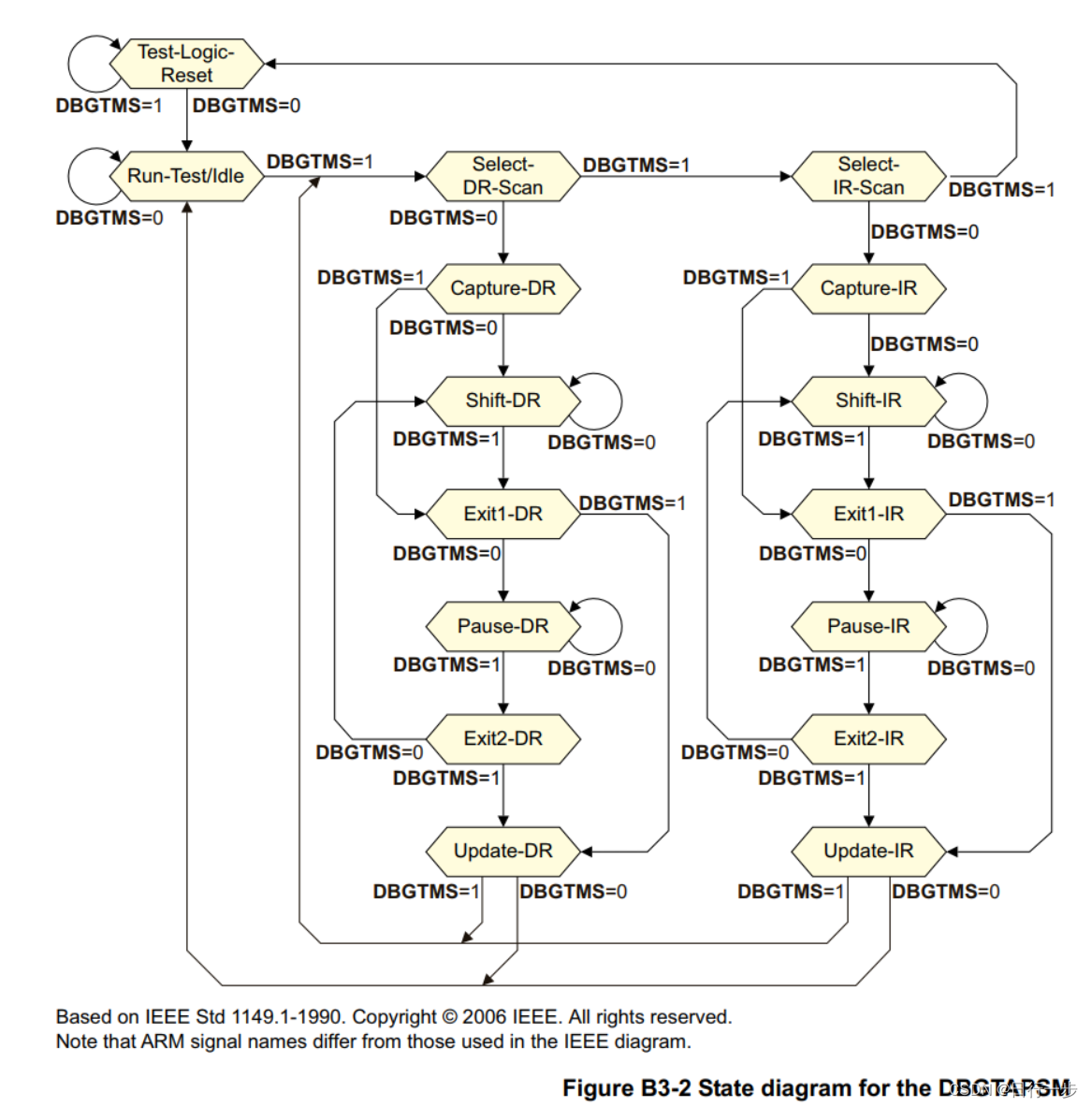

1.2、The Debug TAP State Machine (DBGTAPSM)

TAP(TEST ACCESS PORT) 是一个通用端口,通过TAP 可以访问芯片提供的所有数据寄存器(DR:Data Register)和指令寄存器(IR: Instruction Register)。对TAP的控制是通过TAP controller来完成。

参考:debug_interface_v5_2_architecture_specification.pdf

2、JTAG 的应用

- 在线调试:通过JTAG接口,可以将调试器连接到目标嵌入式系统,以便在系统运行时进行调试和故障排除。

- 边界扫描:JTAG接口支持边界扫描测试,可以检测和识别硬件故障,例如断路、短路、连接不良等。

- 在系统编程(In-System Programming):JTAG接口可以用于在系统运行时对目标嵌入式系统进行编程和更新。

- 芯片级调试:JTAG接口可以用于连接调试器到芯片内部,以便进行更详细的调试和故障排除。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?