最近用到了FPGA,使用它的时候下了一个新的软件vivado,vivado的使用真是让我有点头疼,查阅了一些资料,然后这里也给大伙提供一下安装和使用的流程,和大伙一起进步。

文章目录

前言

本篇所用到的所有文件都在下面网盘里面提供给大伙,可以先下载下来再看下面的文章进行安装使用等操作。

夸克网盘

链接:小白兔的礼物——Vivado

提取码:eEqN

解压密码:hbljdxbt

vivado 2023.2安装

Xilinx注册

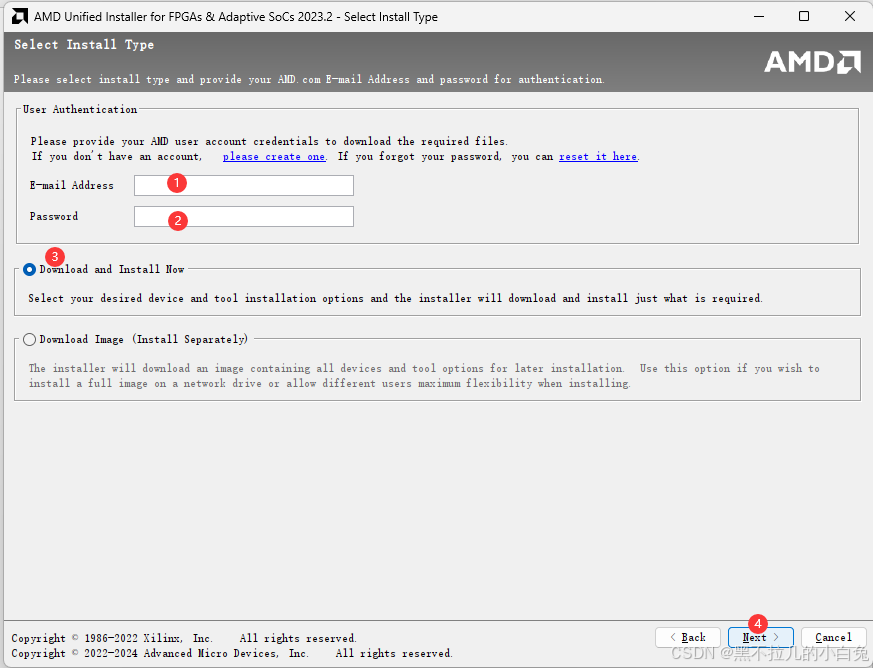

AMD公司的产品在下载的时候都需要填写账号密码,所以我们要先去官网进行一个注册操作。

跳转链接:创建账户

安装包下载

大伙可以在官网里面下载自己想要的版本,或者也可以直接下载上面网盘里面的版本,基本都是一样的。

跳转链接:下载

安装软件

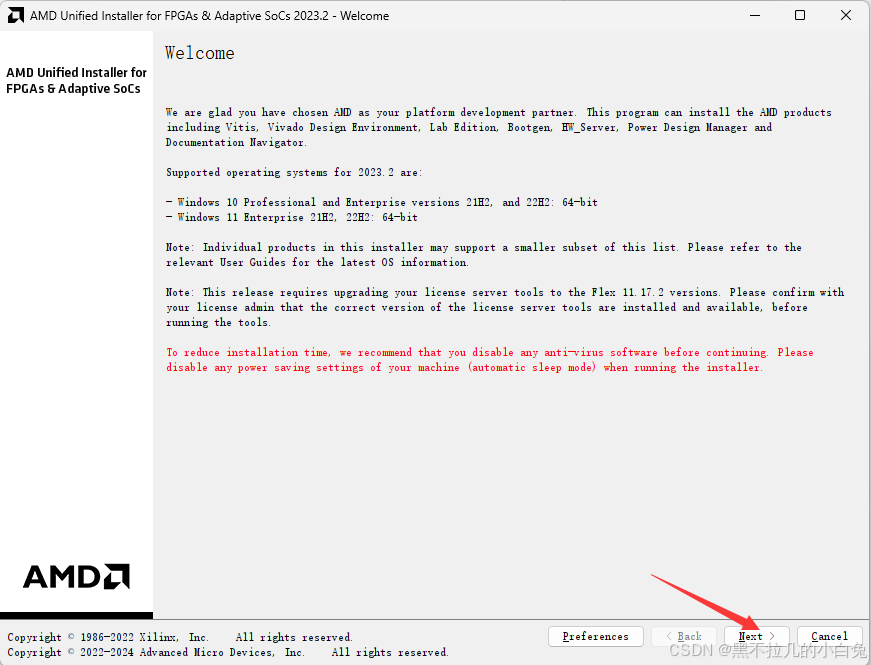

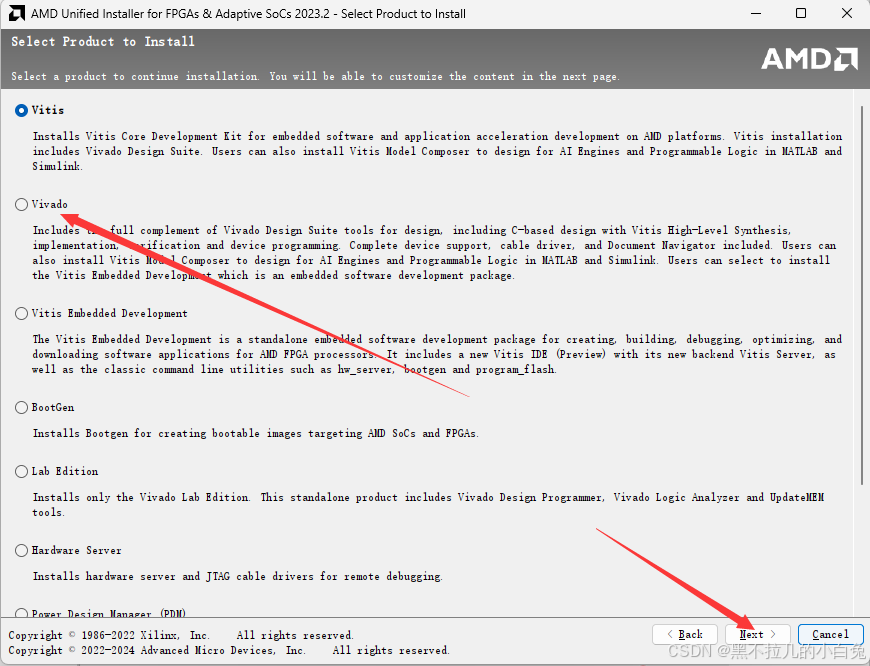

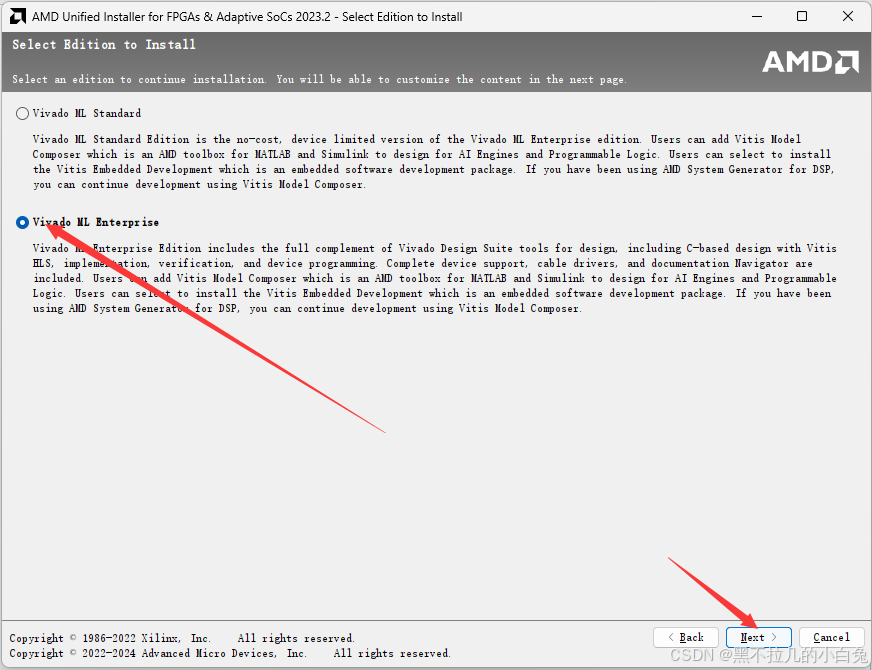

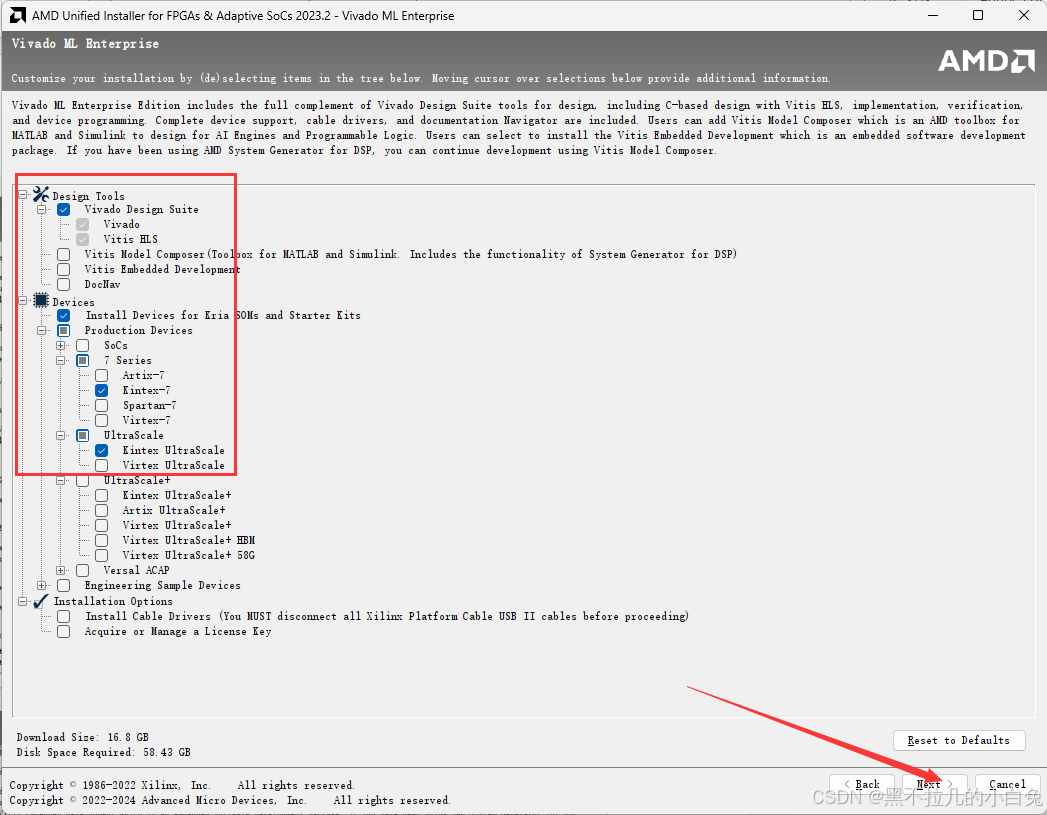

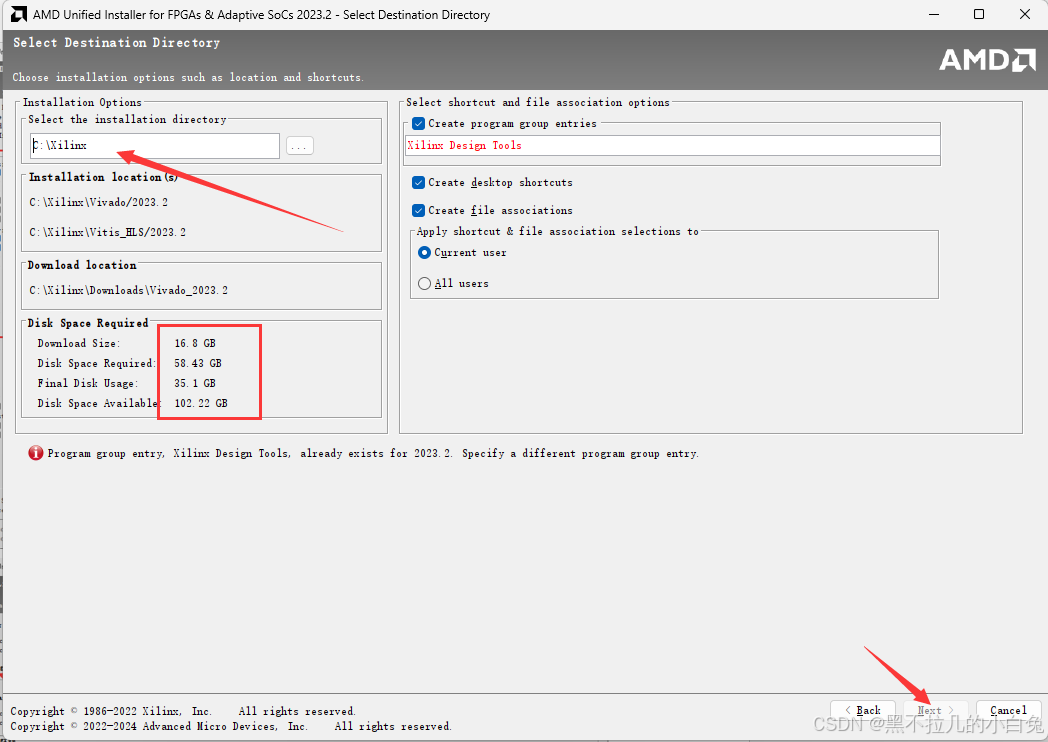

下载完成后运行安装程序, 根据图片箭头指引进行安装。

注意:安装文件存放路径不能有中文字符:

注:这部分选项大伙自行选择,这里只是提供一下需要下的。

OK,到这里安装就结束了,下面就只需要注册一下就行了。

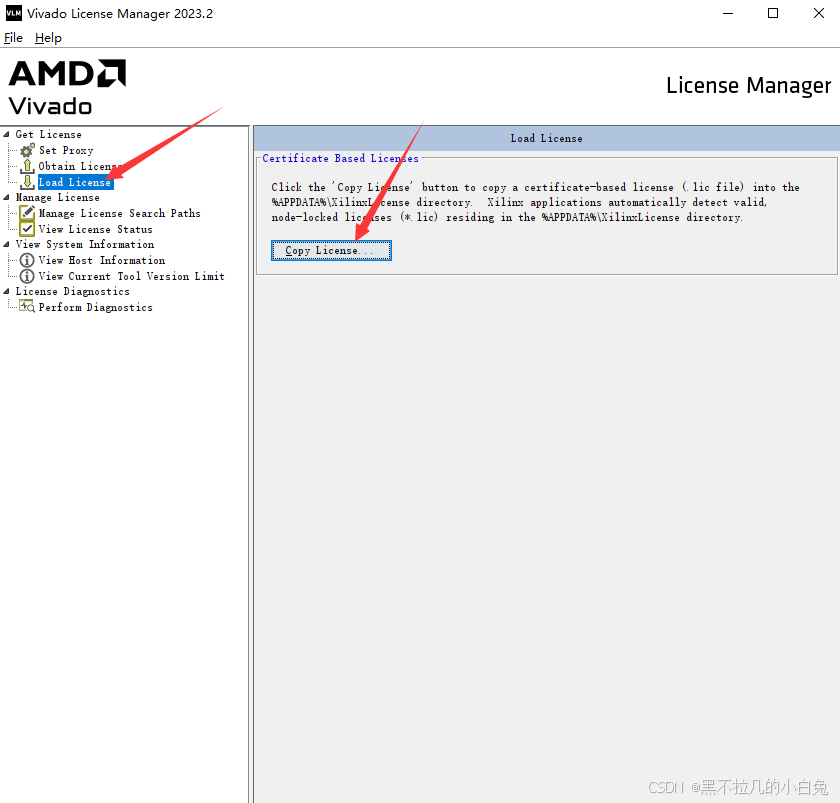

注册

大伙导入网盘里的两个lic文件就行了。

vivado 使用教程

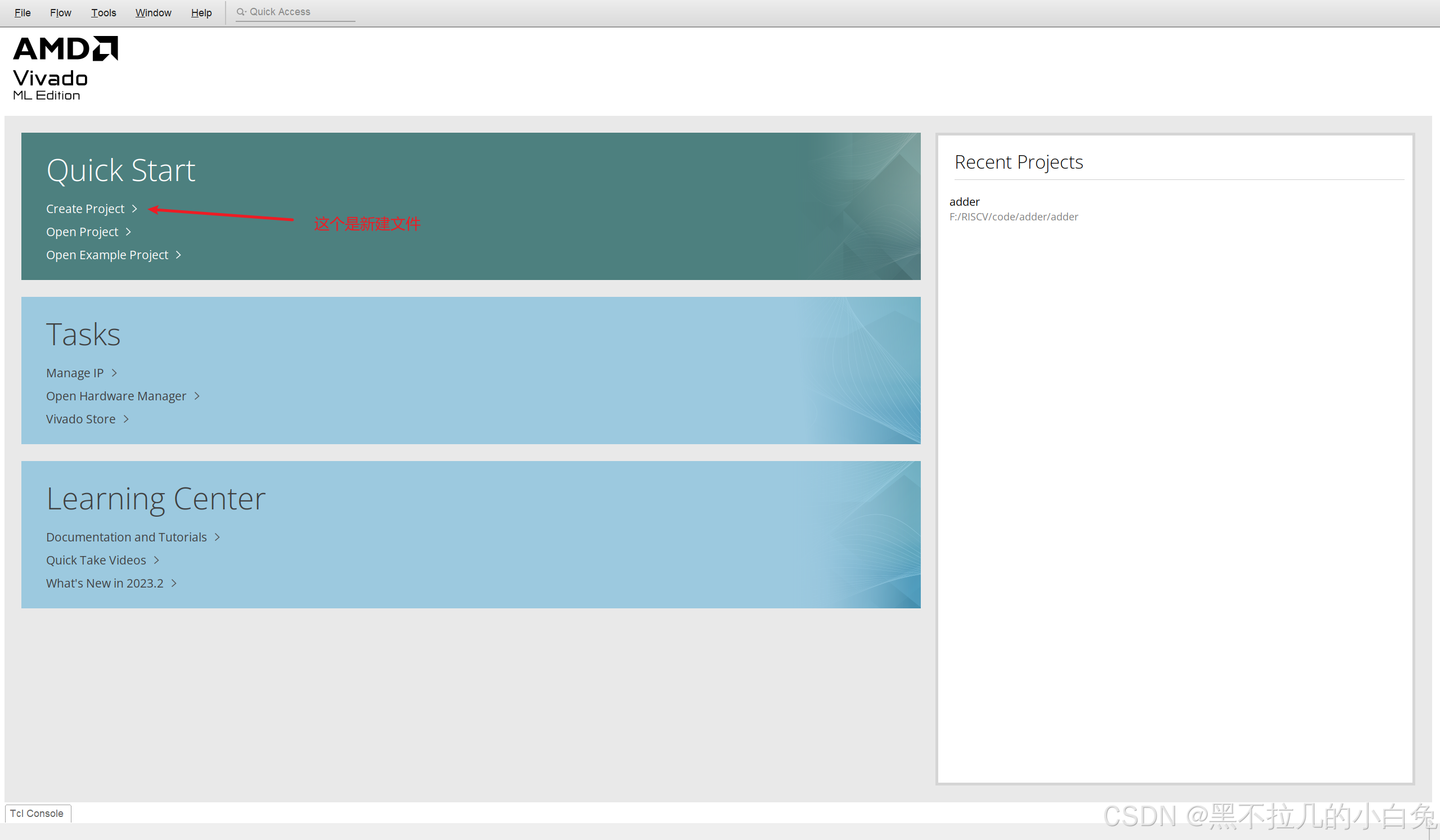

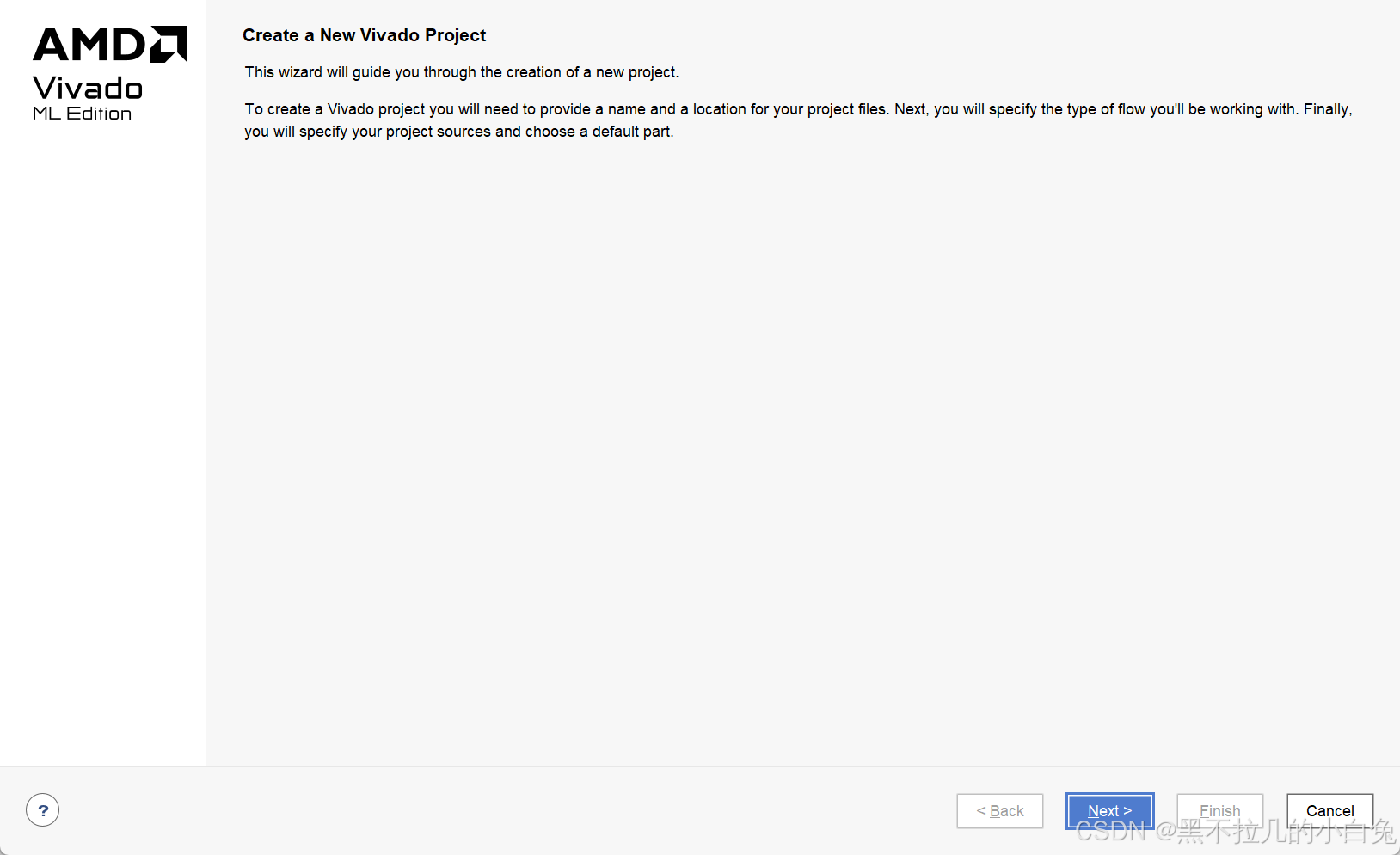

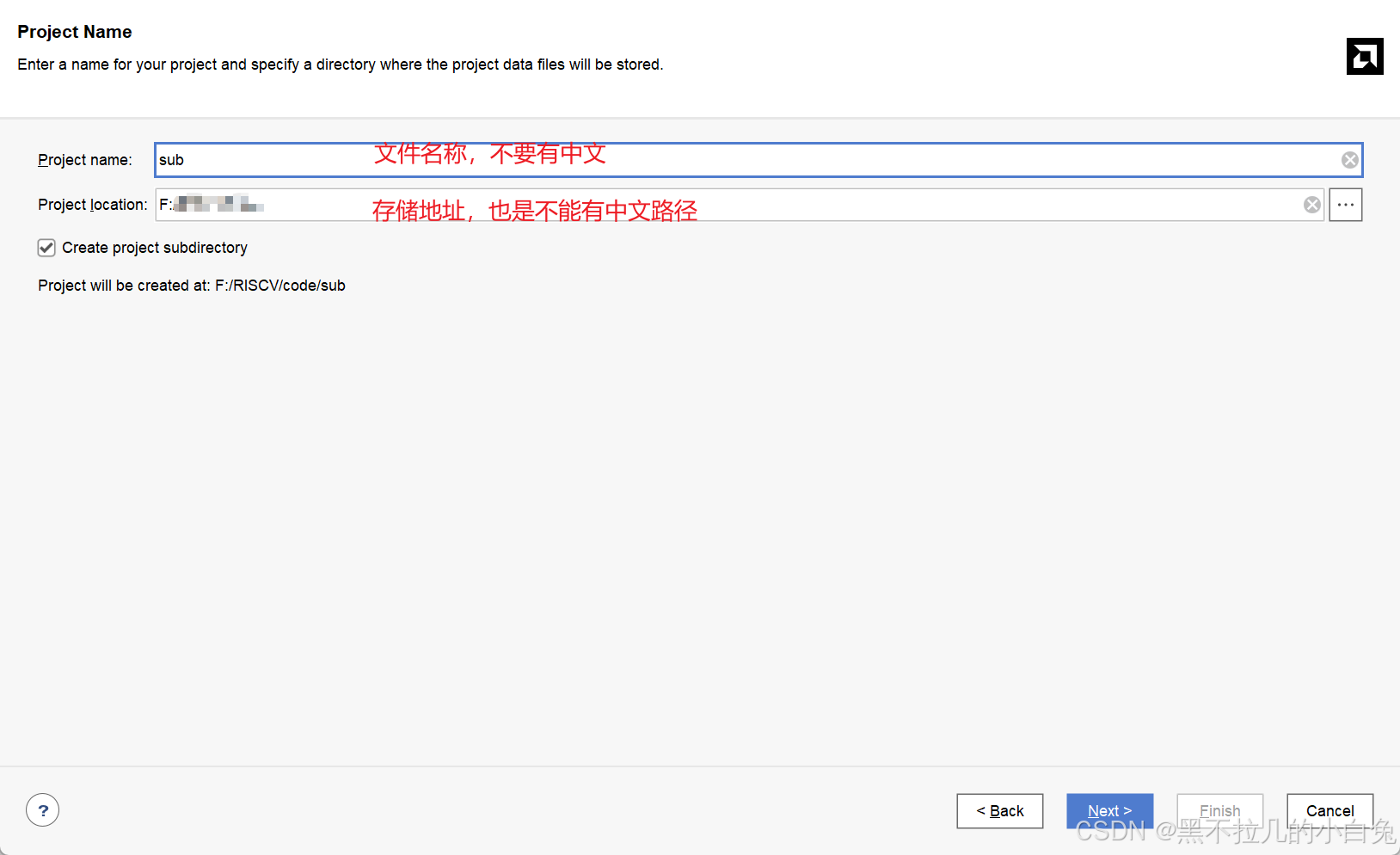

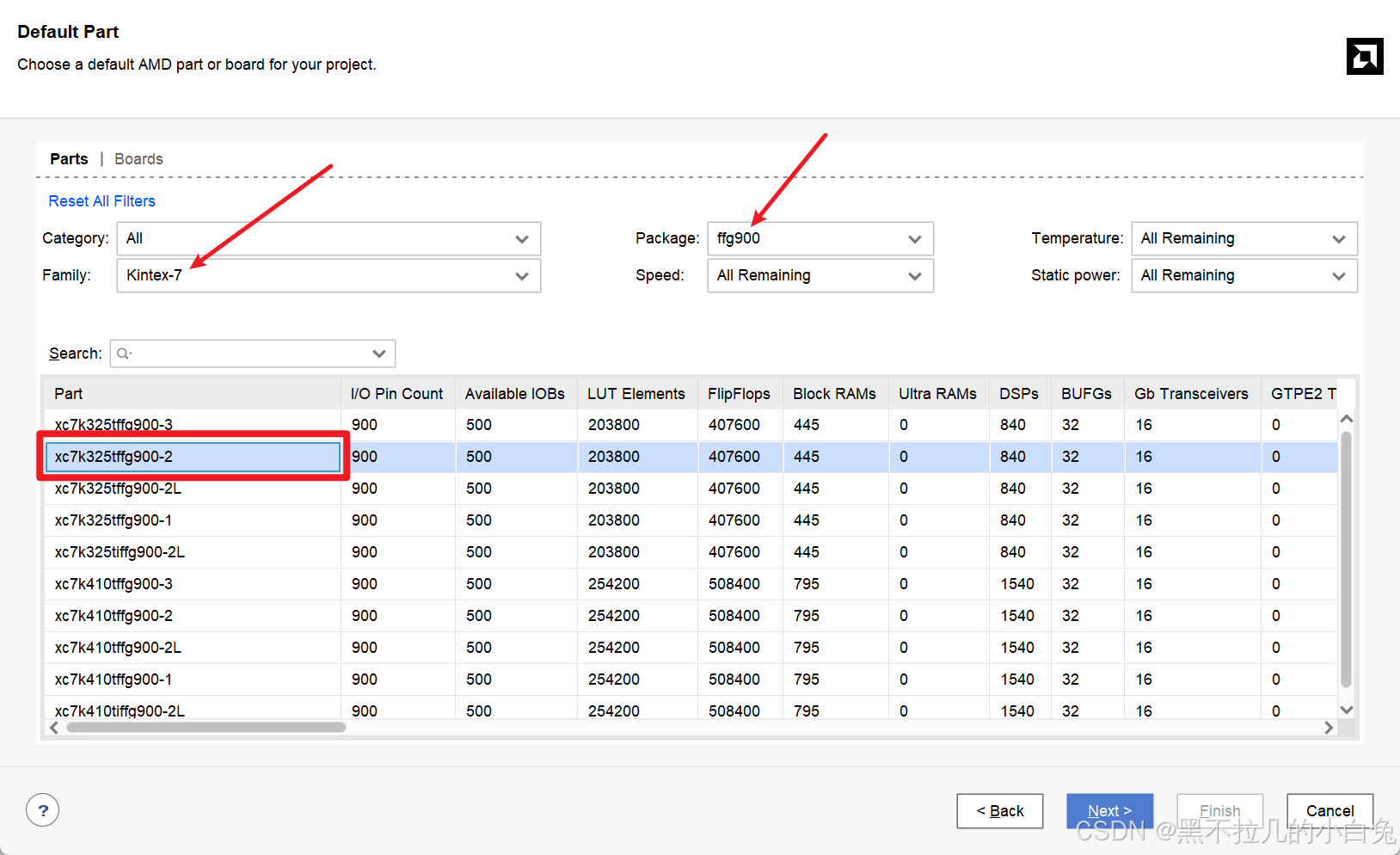

新建项目

这里就教大伙写一个乘法器的模块来带大伙用一下这个软件。

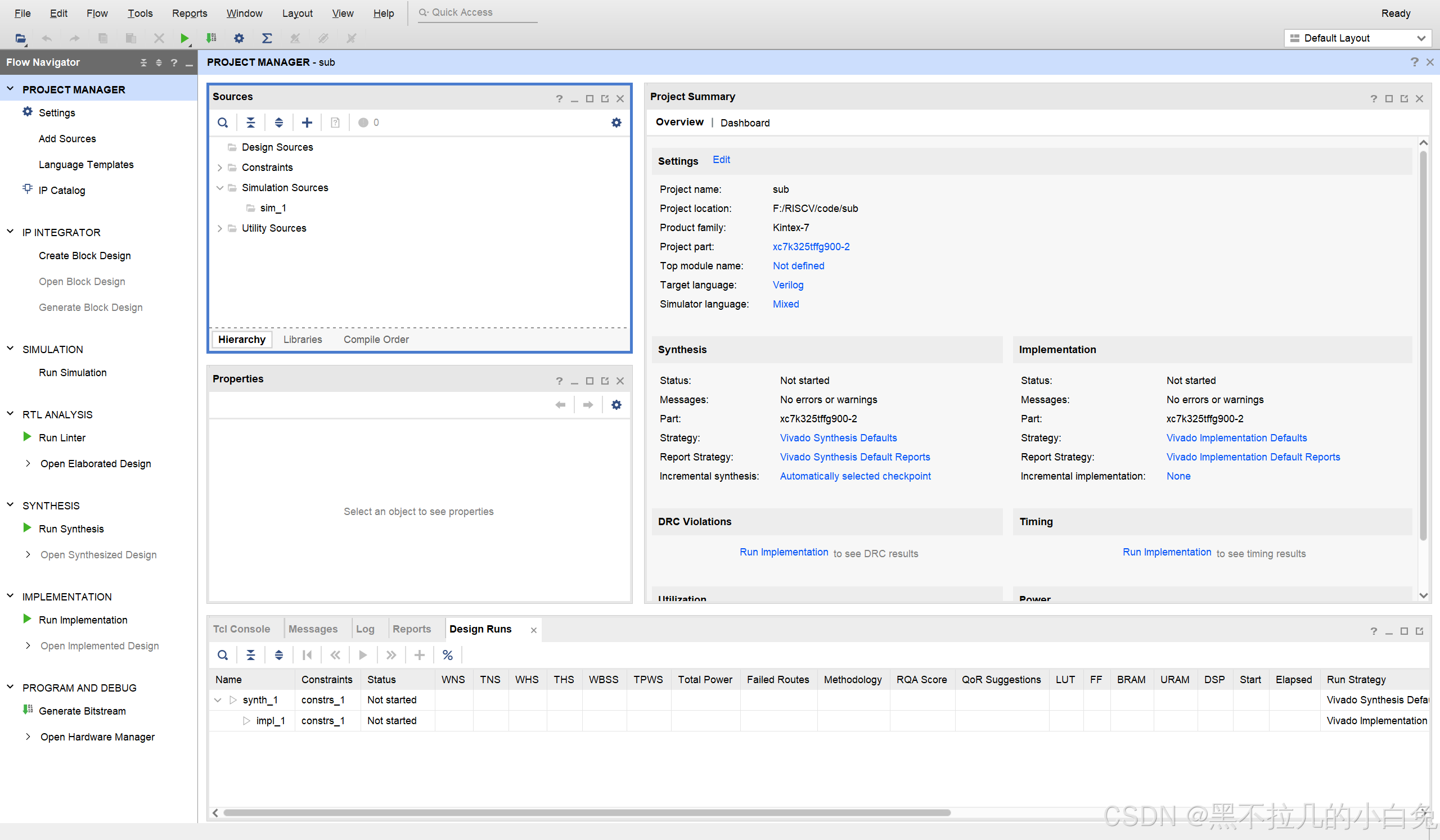

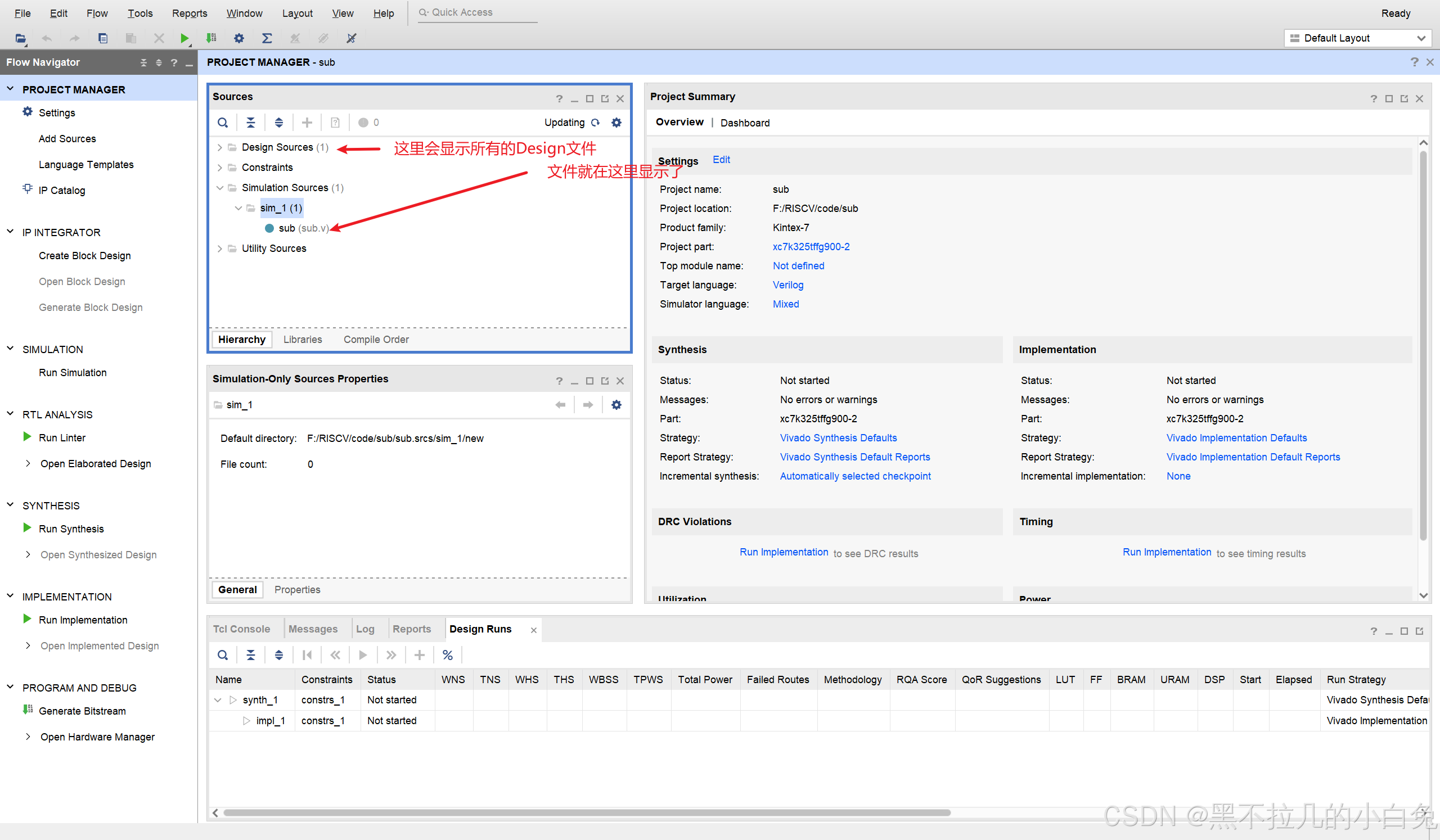

然后我们建出来的东西就是这么个界面 ——

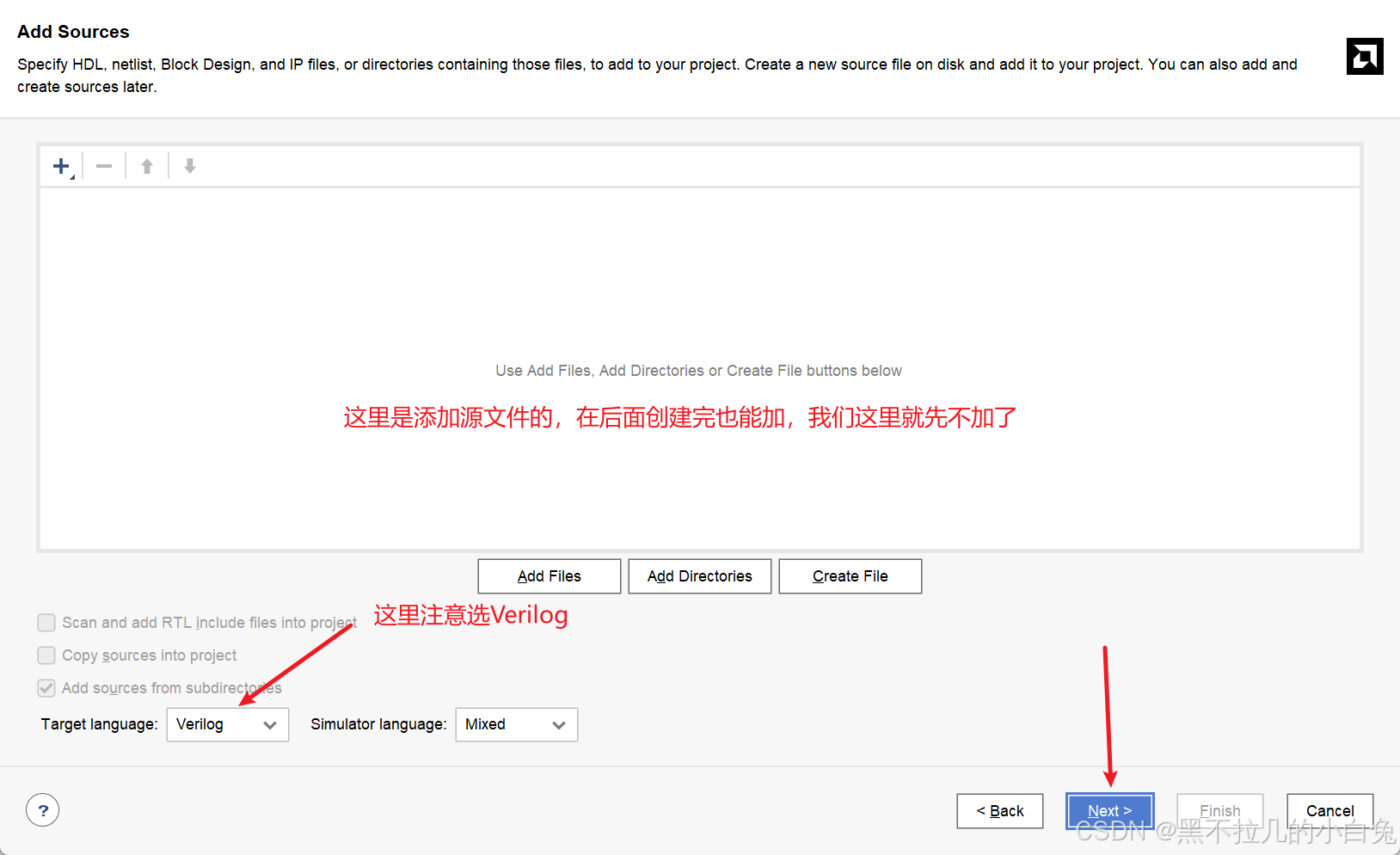

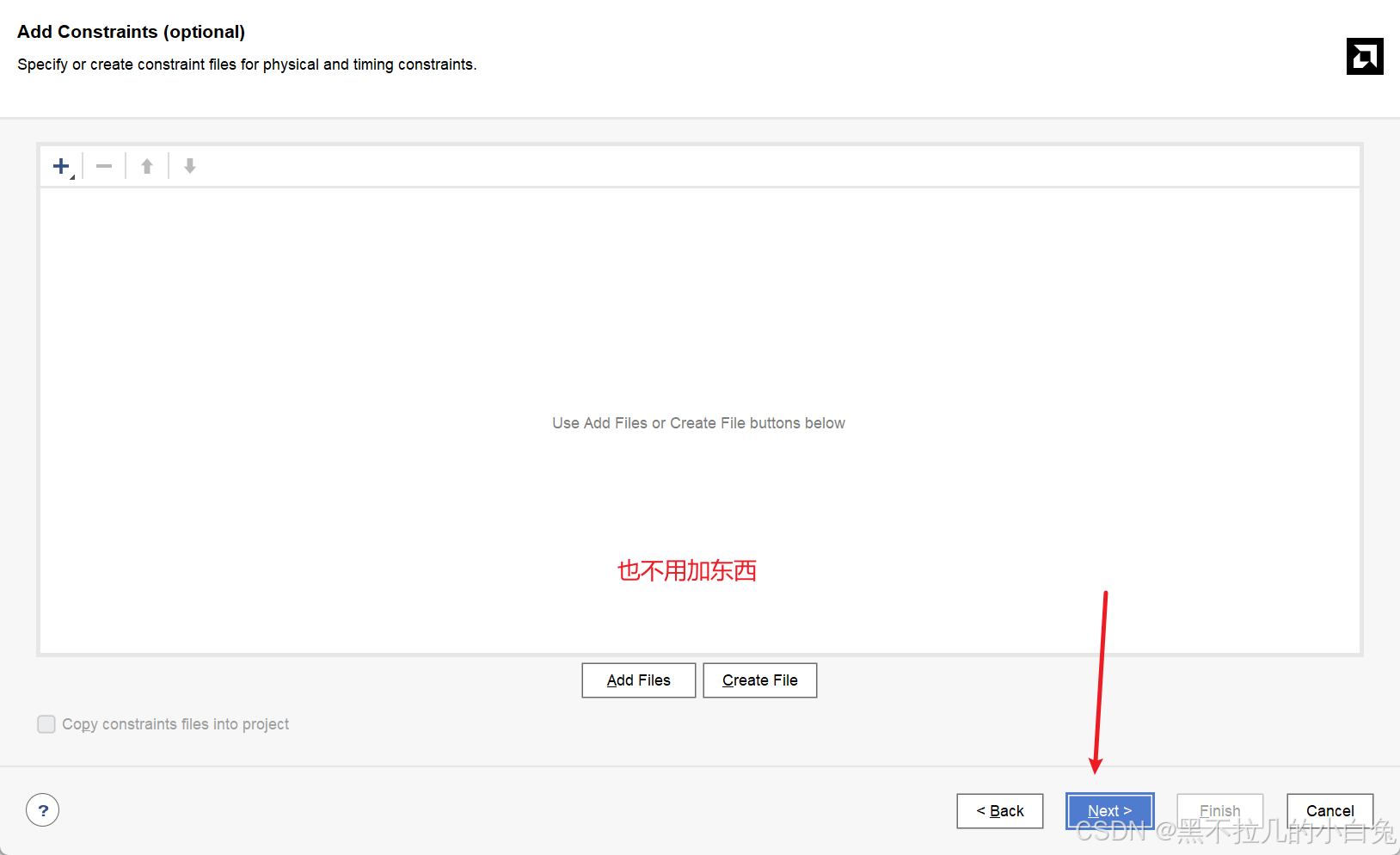

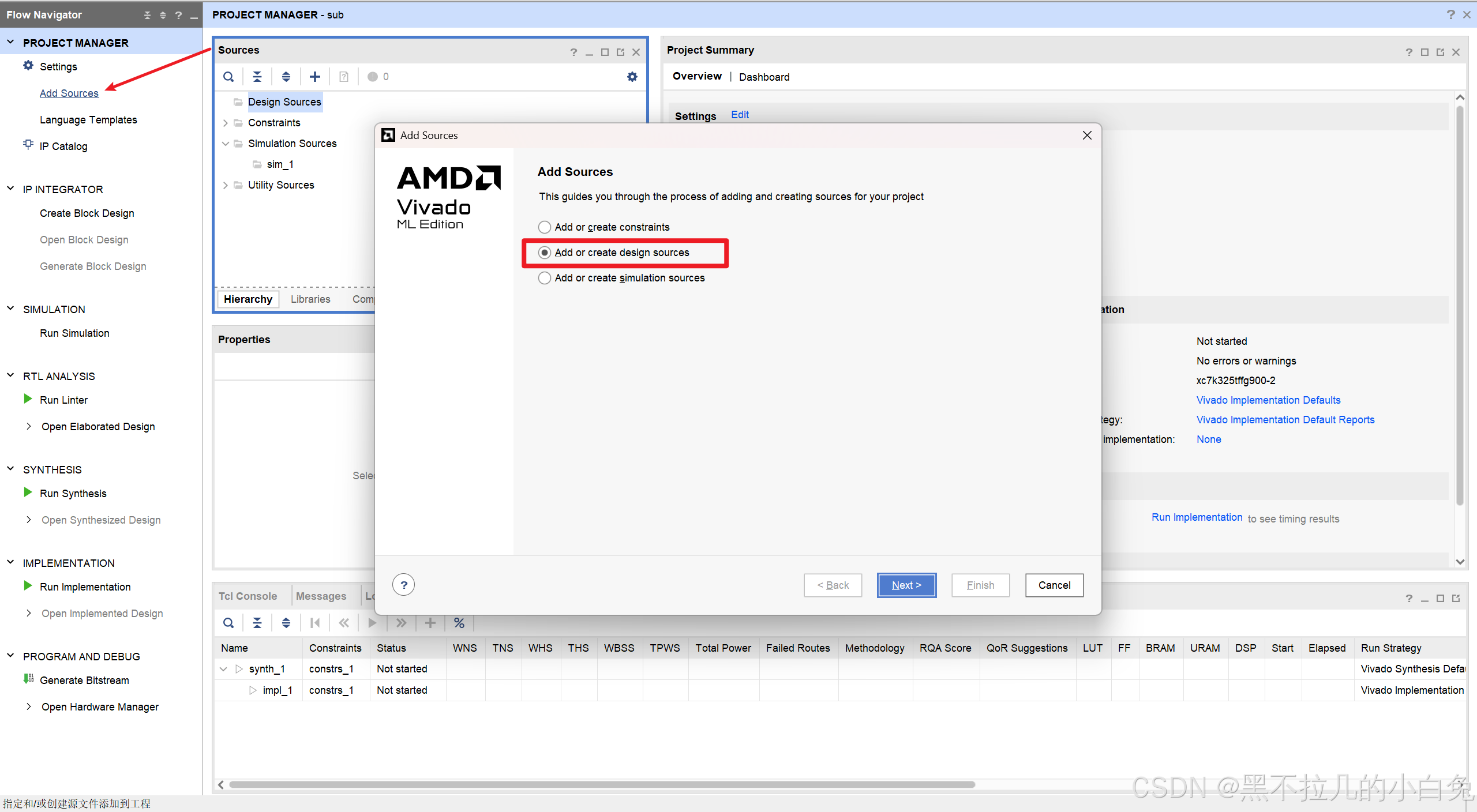

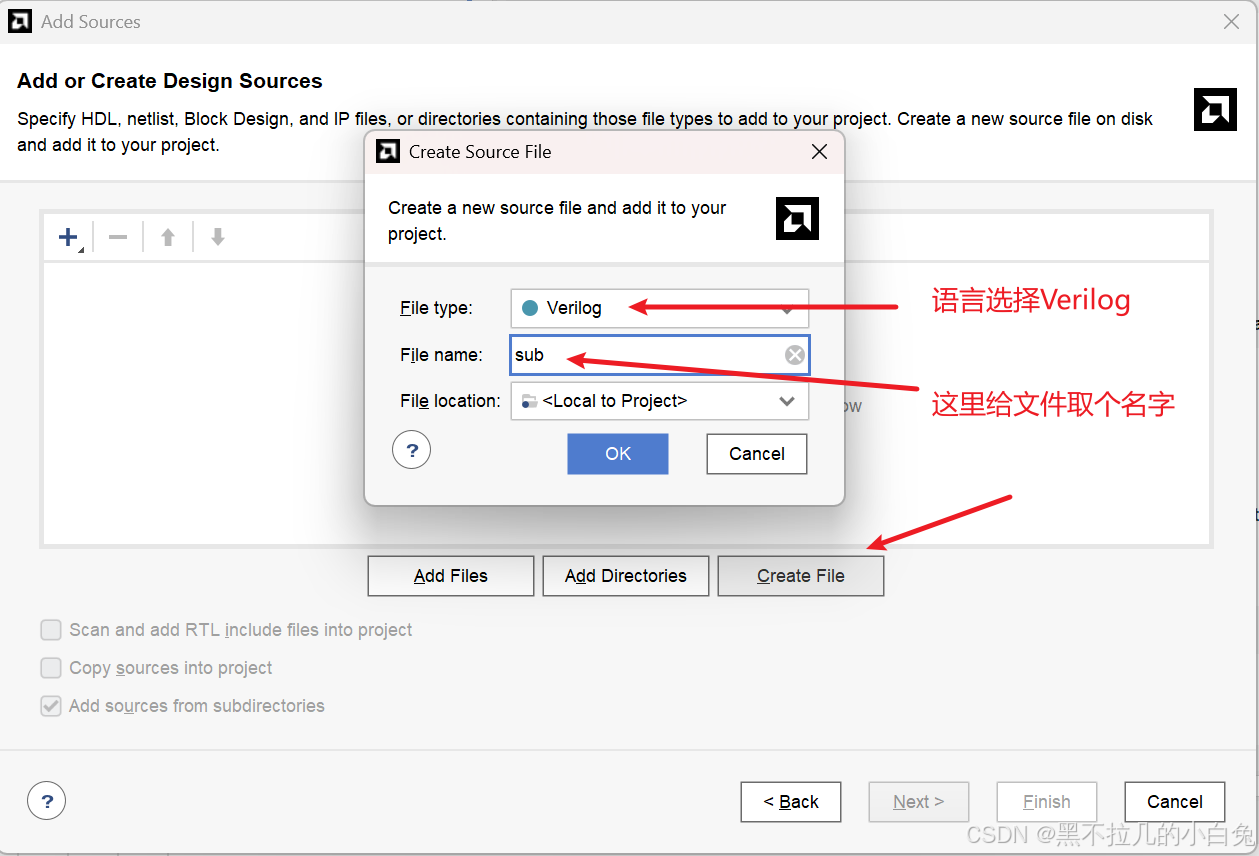

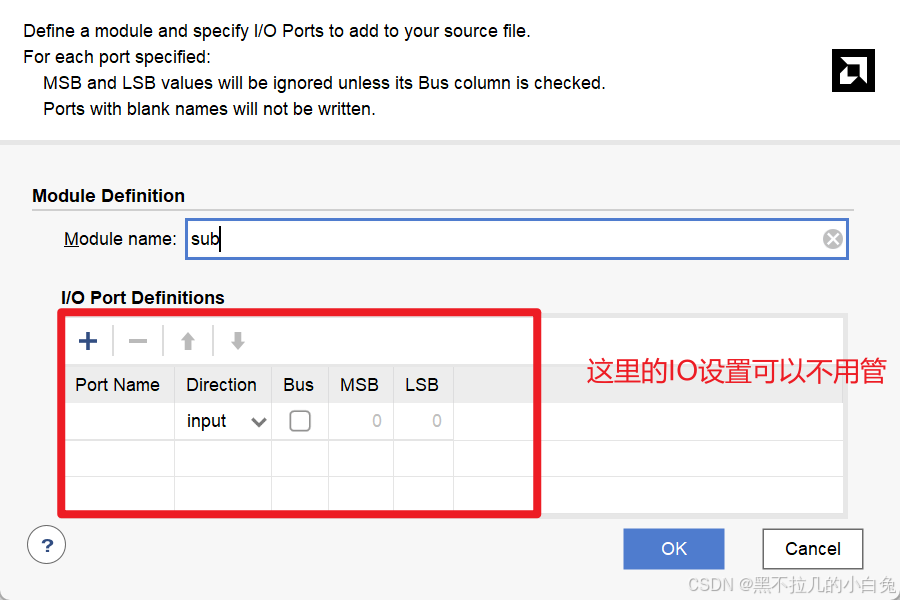

添加源文件

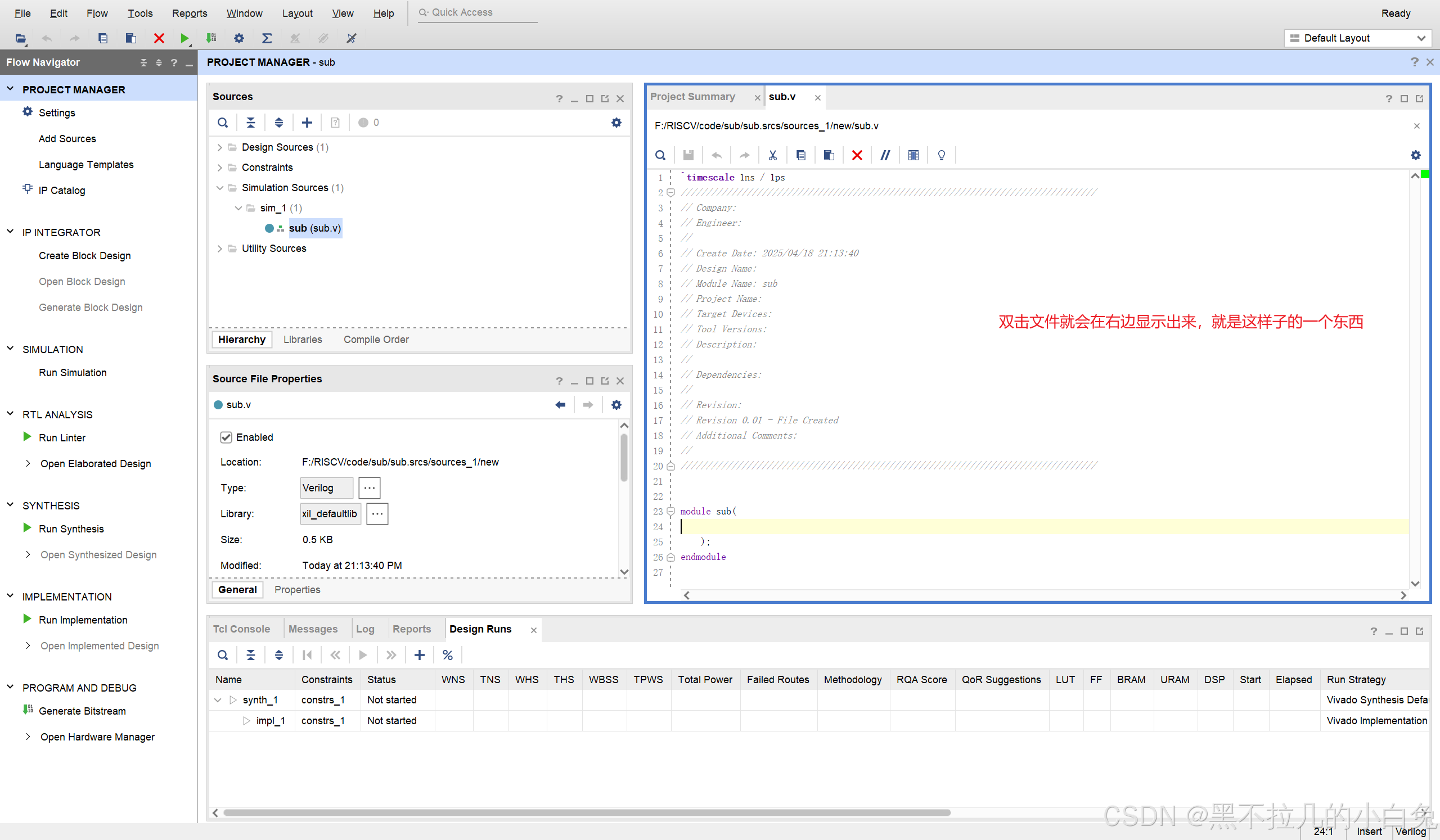

Design文件编写

module sub(a, b, y); //这里的括号里写端口列表

input [31:0]a, b; //参数声明

output [32:0]y;

assign y = a * b; //assign语句

endmodule

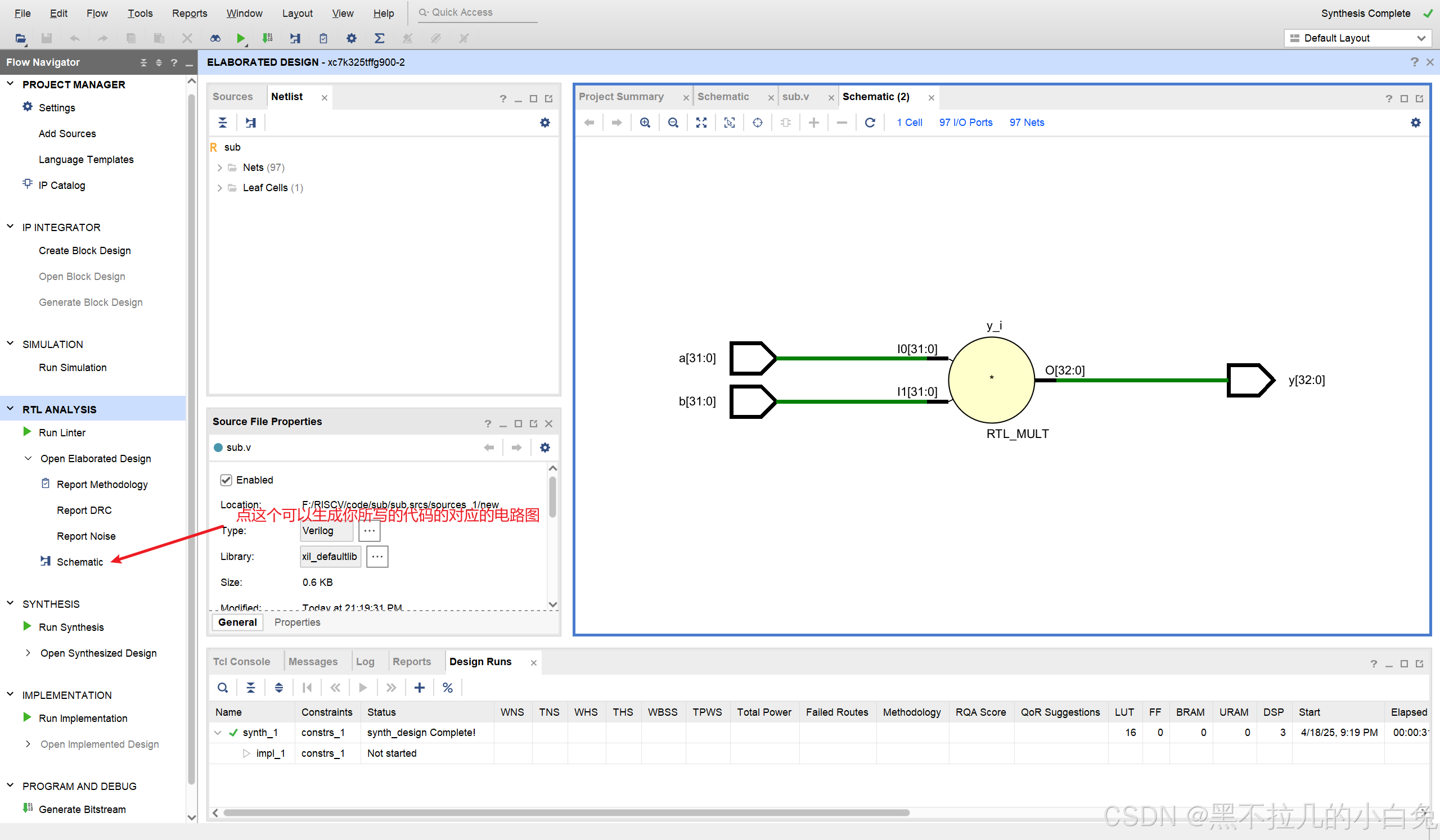

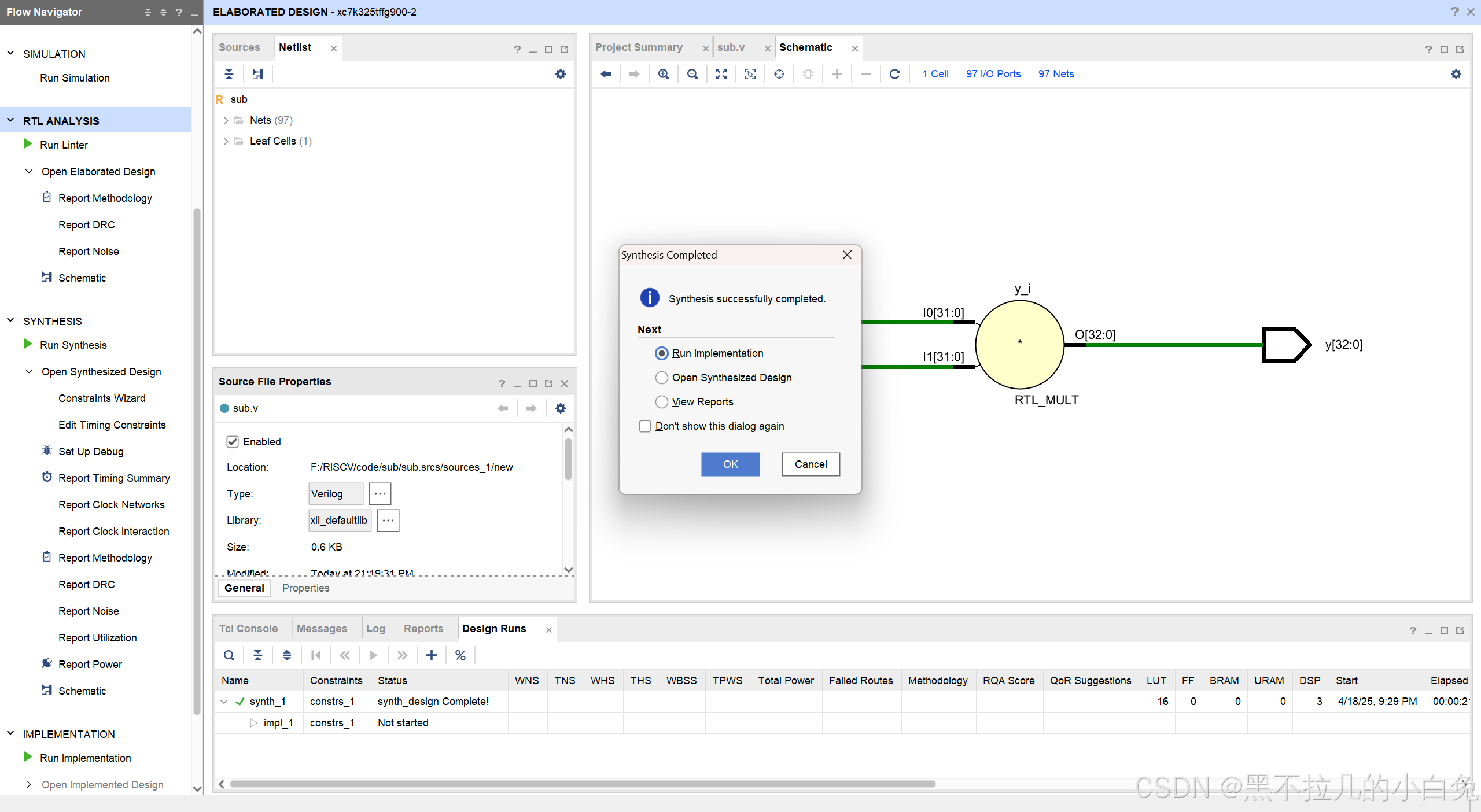

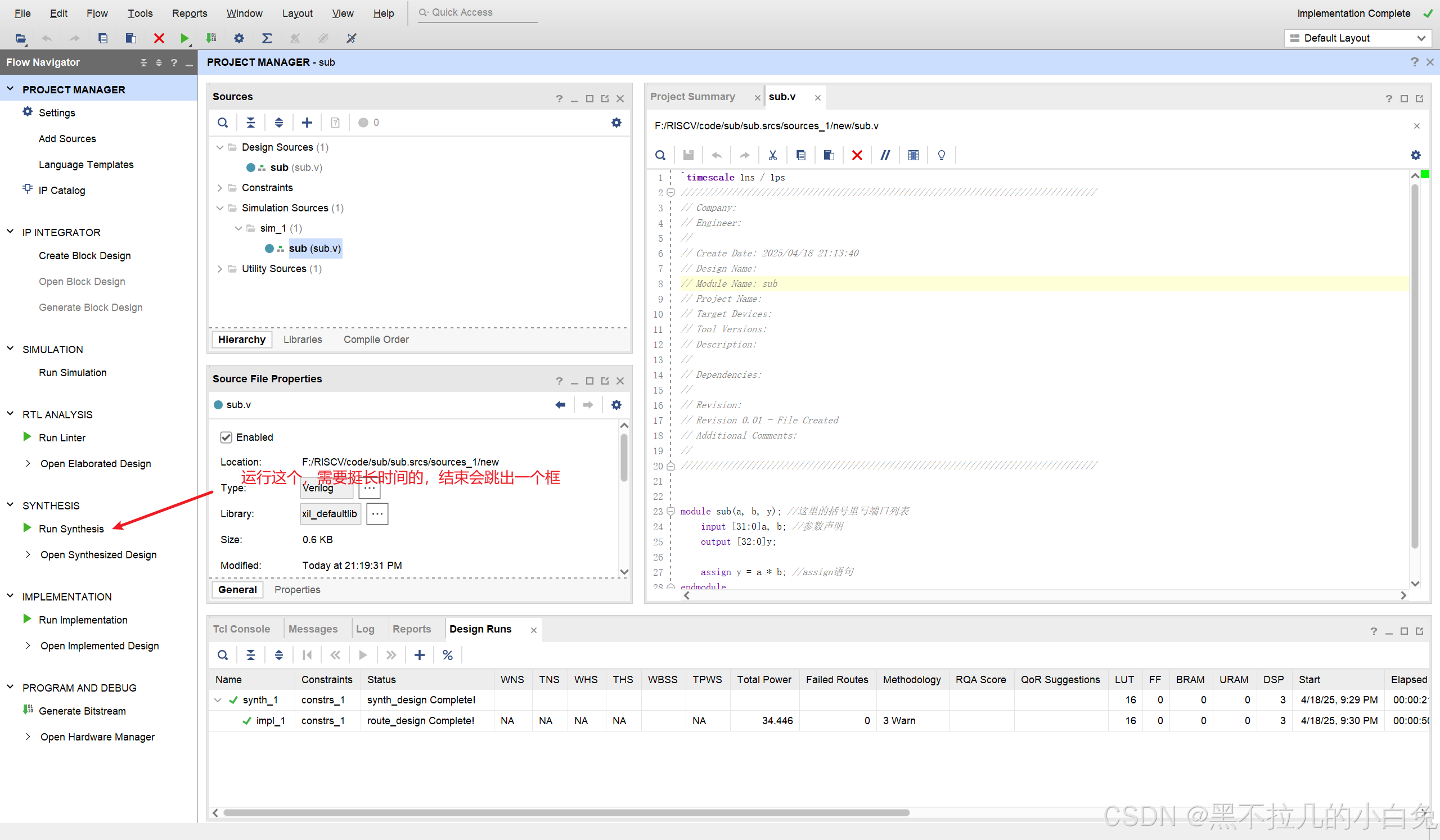

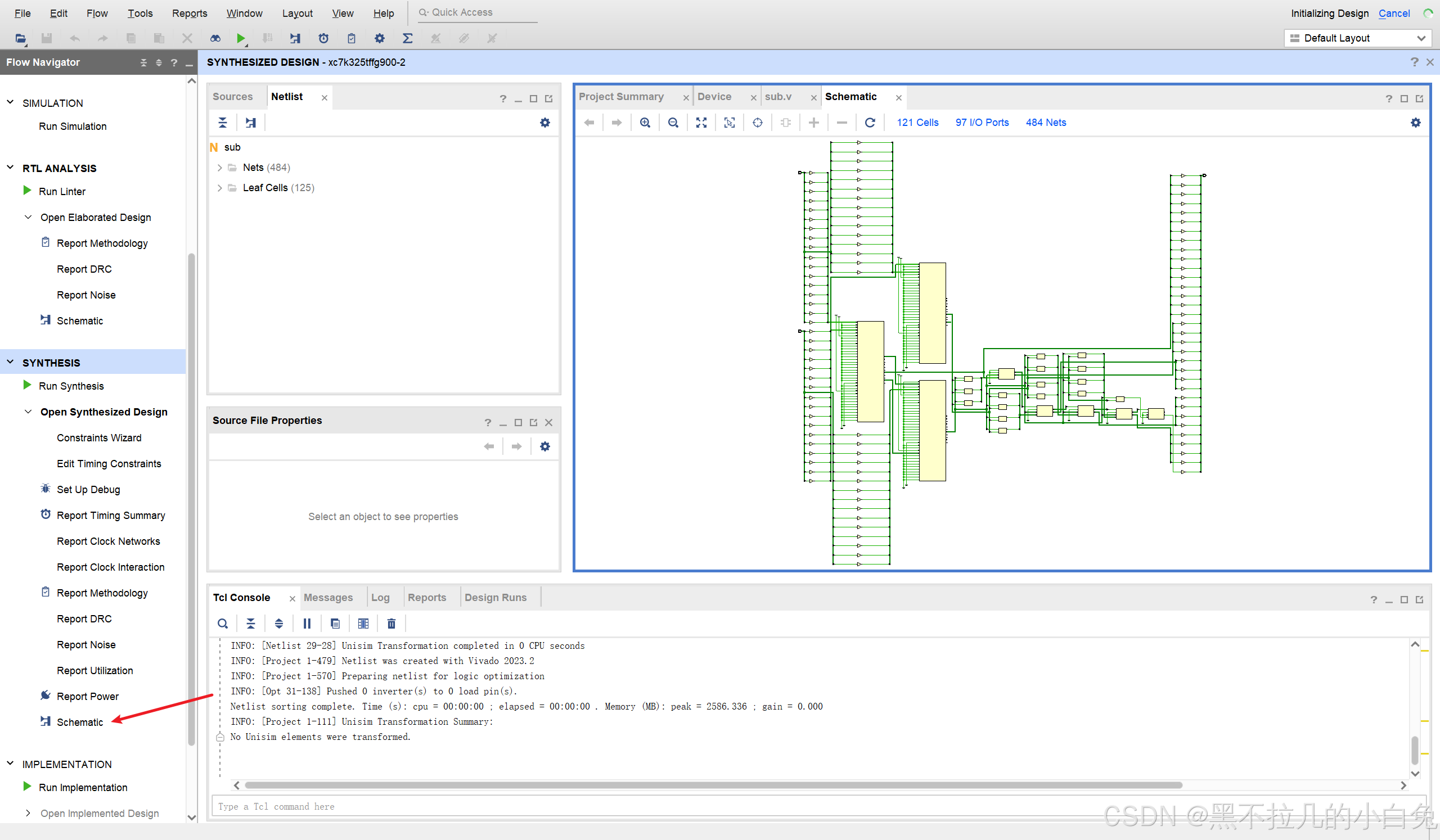

电路图查看

基本上这些没有报错,这个代码就是没问题的。

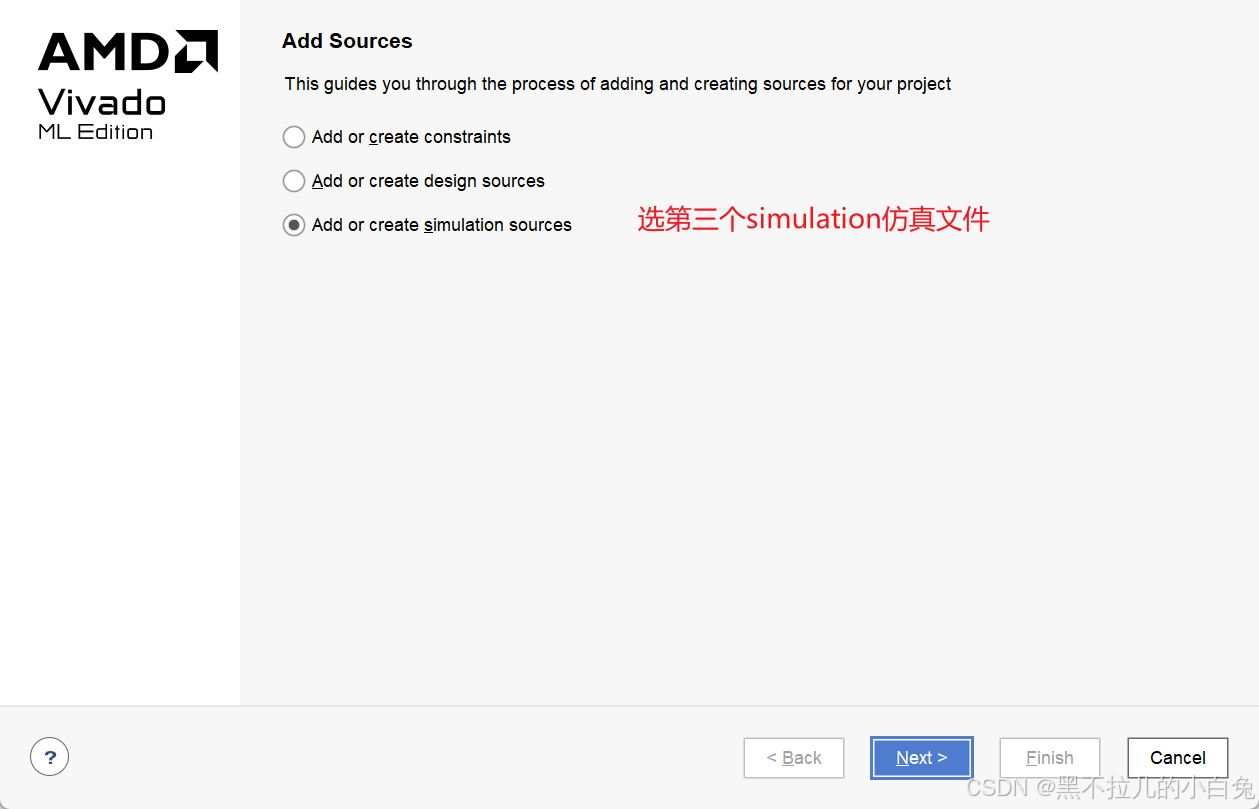

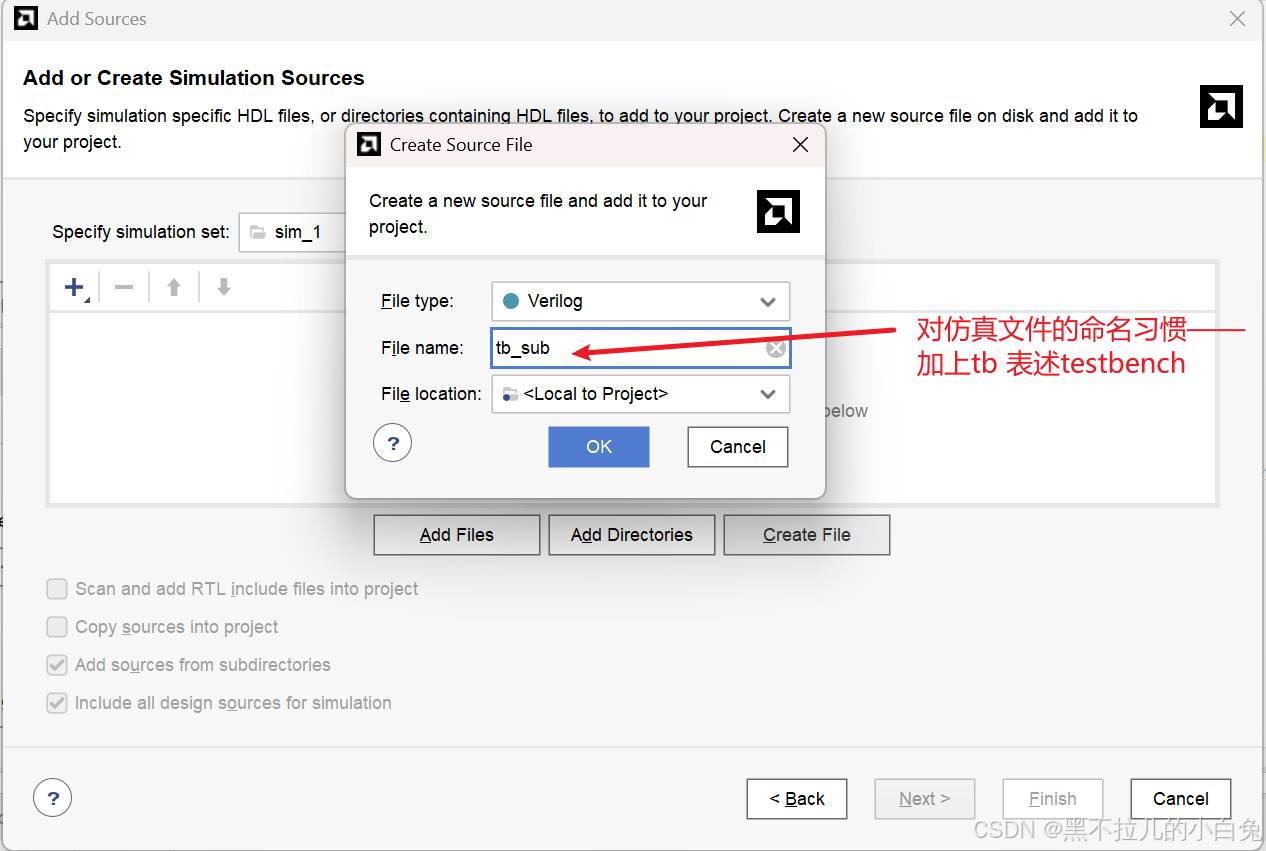

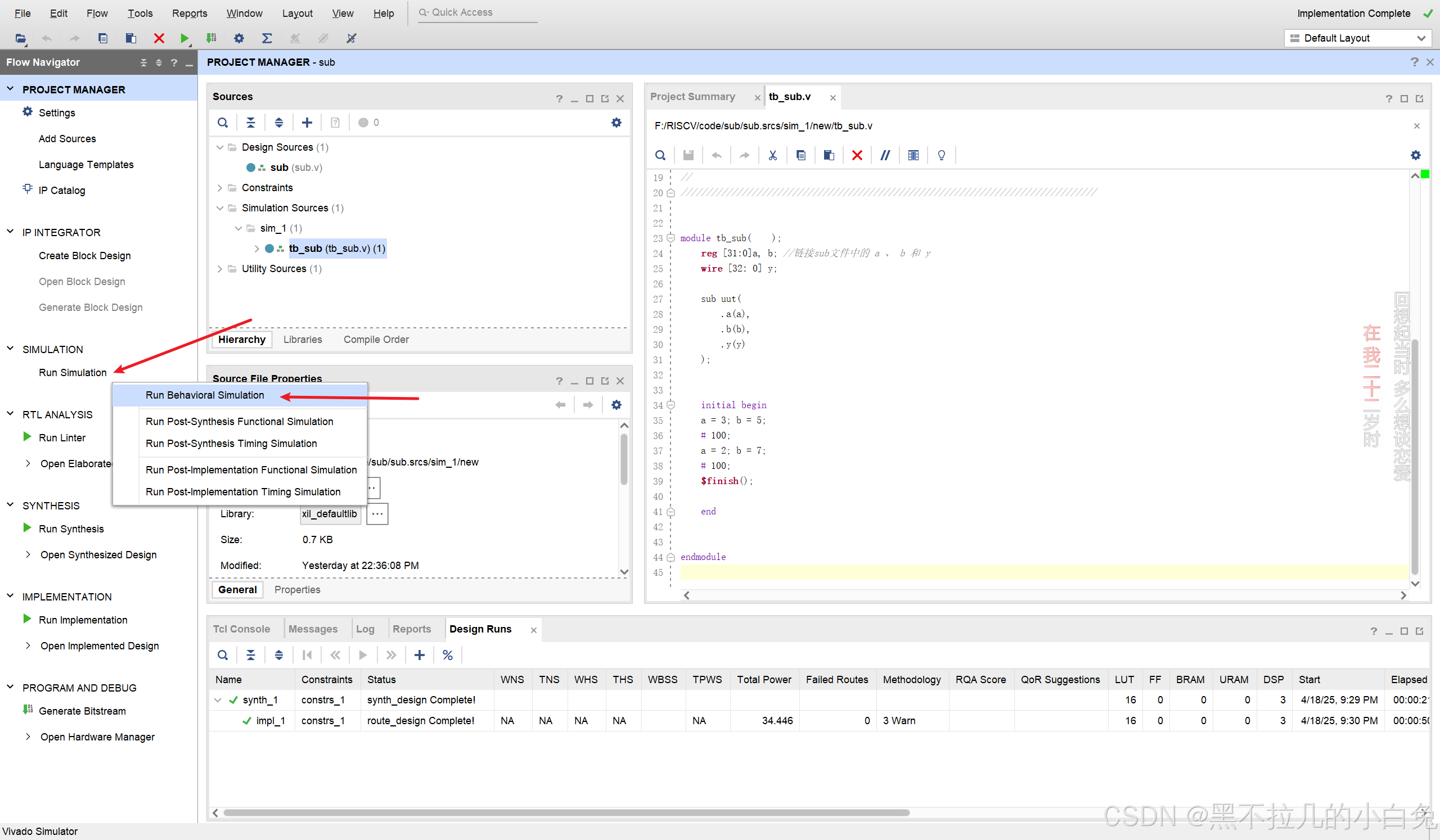

testbench 仿真代码编写

module tb_sub(); // 定义测试模块(无需端口)

reg [31:0]a, b; // 声明32位输入信号a和b(驱动被测模块)

wire [32:0] y; // 声明33位输出信号y(接收被测模块结果)

// 实例化被测模块sub,命名为uut

sub uut(

.a(a), // 连接测试模块的a到子模块的a

.b(b), // 连接测试模块的b到子模块的b

.y(y) // 连接测试模块的y到子模块的y

);

initial begin // 初始化测试过程

a = 3; b = 5; // 测试用例1:a=3, b=5

#100; // 等待100个时间单位

a = 2; b = 7; // 测试用例2:a=2, b=7

#100; // 再等待100个时间单位

$finish(); // 结束仿真

end

endmodule

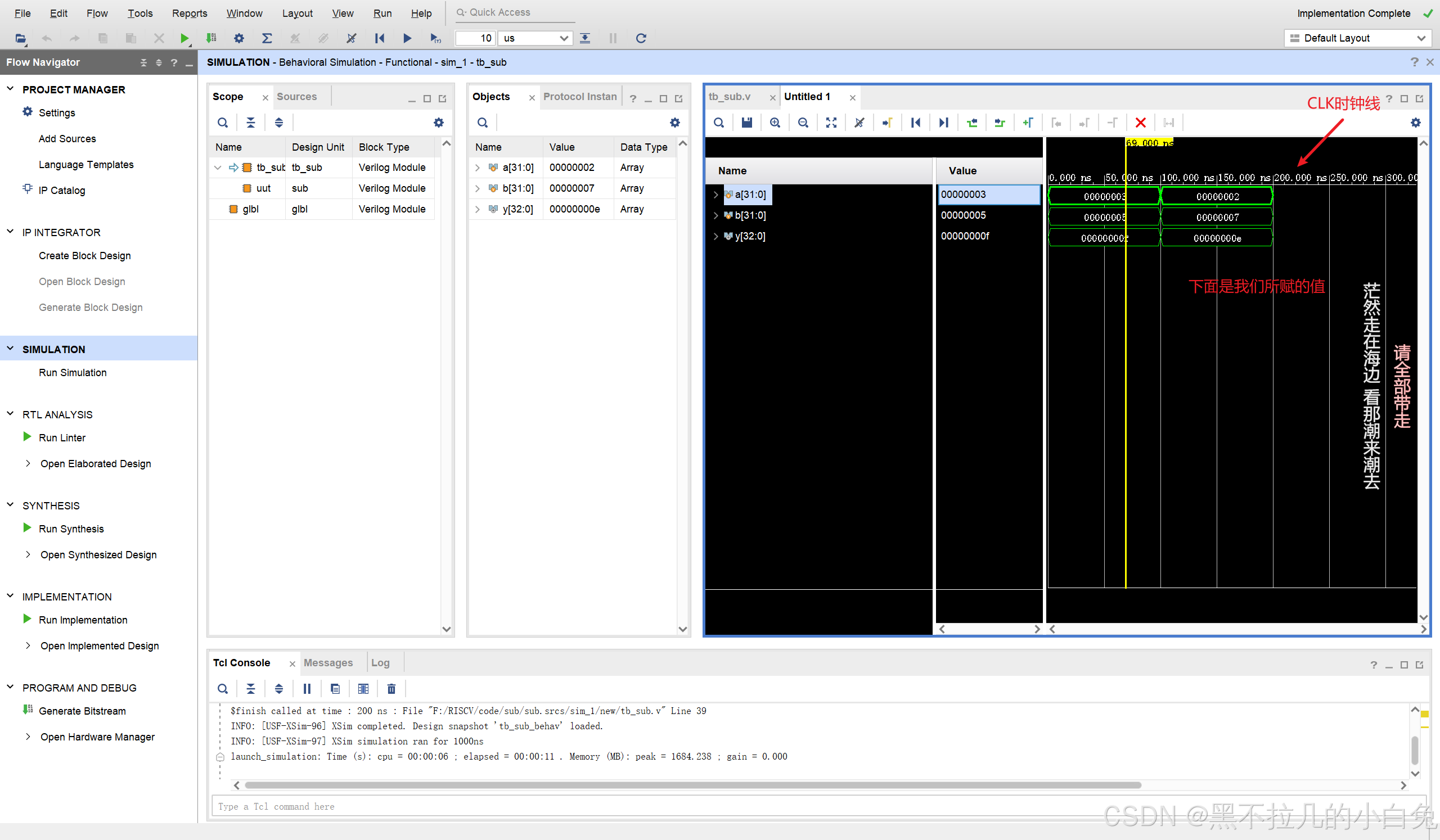

仿真图

总结

这一期带大伙用一下Vivado这个软件,然后给大伙练了一个 sub 模块的代码编写和仿真。

感谢大伙观看,别忘了三连支持一下

大家也可以关注一下我的其它专栏,同样精彩喔~

下期见咯~

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?