一、SCAN 和 JTAG

SCAN(扫描)技术是集成电路测试领域的一种方法,主要用于边界扫描测试(Boundary Scan)。它是在集成电路设计中引入的一种测试结构,允许测试人员通过在芯片的输入/输出引脚上设置和读取特殊寄存器(边界扫描寄存器,BSR)的内容,来间接测试电路板上的互联和芯片内部功能块。这种方式可以在不接触其他内部节点的情况下测试整个电路板的连接性,极大地提高了测试覆盖率和可诊断性。

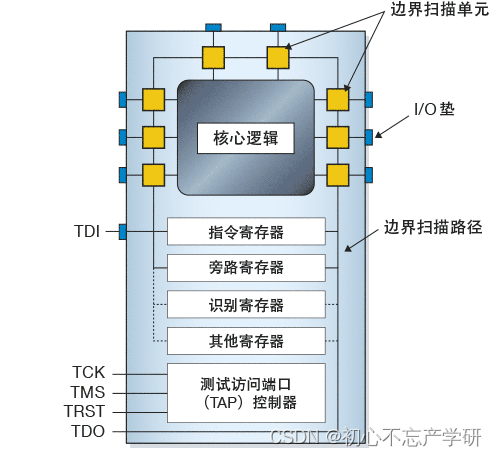

JTAG(Joint Test Action Group,联合测试行动小组)则是开发并推广边界扫描测试标准的一个组织。JTAG制定的标准,即IEEE 1149.1标准,为边界扫描测试提供了统一的硬件接口和协议规范。JTAG接口通常包含四个主要信号线:Test Mode Select (TMS),Test Clock (TCK),Test Data In (TDI) 和 Test Data Out (TDO)。通过这些信号线,可以实现对边界扫描寄存器的串行访问和控制,进行电路板级的测试和调试。

所以, SCAN和JTAG的关系在于:

JTAG是实现SCAN测试技术的一个标准协议和接口规范。

SCAN是边界扫描技术的核心,而JTAG是边界扫描技术应用于现代电子设备的一种具体实现形式。

区别在于:

SCAN更多指的是边界扫描技术本身,是一种通用的概念和方法论。

JTAG则是一个特定的标准和接口,它使得SCAN技术能够在广泛的电子设备中实现标准化应用,并不仅仅局限于边界扫描测试,还扩展到调试、编程等多种用途。

此图片来源于网络

二、SCAN设计规则

在集成电路设计中,SCAN(扫描)设计规则主要是用于实现可测试性设计(Design for Testability, DFT)的一种技术。SCAN设计规则涵盖了在集成电路设计阶段将传统寄存器替换为可扫描寄存器,以及如何将这些可扫描寄存器构成扫描链的过程。以下是详细的SCAN设计规则概述:

设计原则和步骤

可扫描寄存器替换:

普通寄存器改造:将原本用于正常数据传递的寄存器(D触发器)改造成可扫描的寄存器。这意味着每个寄存器增加一个扫描输入端(SI)和一个扫描输出端(SO),以及一个扫描使能端(SE)。

添加MUX(多路选择器):在每个可扫描寄存器的输入端(D输入)前加入一个MUX,MUX的一个输入端连接到正常的系统数据线,另一个输入端连接到扫描输入端(SI)。通过扫描使能信号(SE),可以选择是正常工作模式还是扫描模式。

扫描链构建:

串联连接:所有可扫描寄存器的扫描输出端(SO)连接到下一个寄存器的扫描输入端(SI),以此类推,直到形成一条连续的扫描链。在扫描链的起始和结束位置通常设有全局扫描输入(Shift-in, SI)和扫描输出(Shift-out, SO)端口,供测试仪控制和读取数据。

扫描控制信号:

扫描使能(SE):全局的扫描使能信号用于切换电路进入扫描模式或正常工作模式。在扫描模式下,数据通过扫描链进行移位操作,而在正常工作模式下,寄存器通过D输入接收数据并在时钟上升沿存储数据。

捕获(Capture)、重置(Reset)、保持(Hold)、更新(Update)等额外的测试状态,根据JTAG或其它测试协议进行定义和控制,以完成不同的测试操作,如加载测试向量、捕获电路响应等。

扫描链长度和扇出控制:

扇出限制:为了避免在长扫描链中出现驱动能力和信号完整性问题,需要对扫描链的扇出(即单个寄存器的下一级级联的寄存器数量)加以限制。

分割和层次化:大型设计中,可能需要将扫描链分割为多个层级或组别,通过扫描路径选择器(Multiplexer)连接,以降低扇出和简化测试过程。

测试模式和设计约束:

测试模式定义:设计时需要明确各种测试模式下的操作流程和状态转移,包括初始化、扫描操作、退出扫描模式和执行测试等。

保持设计约束:在引入SCAN设计时,需要确保不影响芯片在正常工作模式下的功能和性能,例如,不能因为增加扫描功能而导致额外的功耗、面积开销过大或者时序约束被破坏。

具体的应用场景

缺陷检测:通过加载测试向量到扫描链,可以检验电路内部节点和互连的正确性。

故障定位:在发生故障时,可以通过提取扫描链中的响应数据,定位潜在的缺陷位置。

总的来说,SCAN设计规则是集成电路设计者在设计初期就需要考虑的重要环节,目的是增强芯片的可测试性,简化和自动化测试过程,降低成本,提高产品质量和可靠性。

三、可测试性的设计

在数模混合芯片设计时,除了SCAN(扫描)技术之外,还有多种可测试性设计(Design-for-Testability, DFT)技术用于确保芯片在设计阶段就能实现高效和可靠的测试。以下是几种常用的数模混合芯片DFT技术:

嵌入式自测试(Built-In Self-Test, BIST):

BIST技术允许芯片在出厂或现场自行执行测试序列,无需外部测试设备干预。在数模混合芯片中,BIST可用于模拟电路如PLL、ADC/DAC的自我测试,通过内置的测试模式生成器和响应分析器来评估电路性能。

冗余设计:

使用冗余的数字和模拟组件(如冗余的比较器、电流源、振荡器等)可以在主功能元件出现故障时启用备用元件,同时也可以通过对比主备元件的输出来进行在线监测和故障诊断。

模拟内建自修复(Analog Built-In Self-Repair, ABISR):

类似于数字领域的SRAM BISR,ABISR允许在检测到模拟电路故障时,通过内部逻辑切换到预先储备的备份资源,恢复或改善电路性能。

模拟/混合信号边界扫描(Analog/Mixed-Signal Boundary Scan, AMS BS):

类似于数字边界扫描,AMS BS扩展了边界扫描技术,使其能够用于模拟和混合信号电路的测试。通过特殊的模拟边界扫描单元,可以测试模拟信号路径、电源网络和混合信号接口等。

电流监控和注入技术:

在模拟和混合信号电路中,可通过设计专门的电流监控和注入电路,用来检查和控制电流水平,以测试和验证电路的电流消耗和信号强度。

模拟和混合信号测试向量生成(ATPG, Analog Test Pattern Generation):

ATPG算法用于生成针对模拟和混合信号电路的测试向量,通过模拟信号注入和响应测量来探测和定位故障。

敏感性分析和蒙特卡洛仿真:

在设计阶段利用敏感性分析和蒙特卡洛仿真技术预测电路对各种参数变异的敏感性,优化电路以增强其对工艺波动的稳健性,提高测试覆盖范围。

设计时考虑测试点和测试通道:

在模拟和混合信号电路设计中,预留测试点和测试通道,方便测试仪器接入,以直接获取关键节点的信号,进行离线或在线测试。

这些技术的组合应用可以显著提高数模混合芯片的可测试性,缩短测试周期,降低测试成本,并提高产品的质量和可靠性。

464

464

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?