目前,硅(Si)interposer技术被用于存储器和处理器系统,以实现多芯片的紧密集成并提升系统整体性能和带宽。尽管基于Si interposer的集成具有诸多优势,但在高速链路设计中仍面临新的挑战。这些关键挑战需在高速收发器和Si interposer互连设计的早期阶段解决,以妥善处理芯片集成到Si interposer时产生的信号与电源完整性问题。

实现Si interposer技术需要多项关键组件,包括硅通孔(TSV)、高密度布线以及芯片与硅载体之间的高密度互连(使用ubump)。ubump倒装焊互连使得硅载体的布线密度高于有机或陶瓷基板,同时支持高性能信号与电源连接。然而,ubump的较小高度使得硅芯片中电感器的特性依赖于Si interposer内部的电荷分布。Si interposer的高密度布线导致电源网络具有较高的电阻性。

在高速链路中,电感器和电容器是提升高速接口性能的关键元件。例如,片上电感器在低抖动LC-VCO(压控振荡器)的设计中至关重要。均衡器和终端电路模块也使用电感器以增加带宽并改善发射器与接收器的匹配。电感器通常采用CMOS工艺的顶层金属层制造,因此其品质因数更多受限于衬底损耗而非导体电阻率。为了进一步提高品质因数并确保电学模型的准确性,通常会在衬底中电感螺旋下方添加由下层金属层和多晶硅构成的图案化屏蔽层。然而,引入Si interposer后,需在Si interposer中采用类似的屏蔽机制,以最小化电感器与interposer的相互作用并保持电感器的品质因数。

随着电源噪声裕度的降低,必须使用片上CMOS和金属-绝缘体-金属(MIM)去耦电容器,以有效抑制高频电源噪声和电源引起的抖动。封装上电容器也需用于通过抑制封装电感引起的中频电源阻抗峰值来改善系统电源完整性。第二个挑战在于如何优化这些片外去耦电容器以抑制中频噪声和电源抖动。若封装或interposer上的去耦电容器未充分优化,中频噪声和电源抖动可能限制系统的最高数据速率。

采用interposer的高速信号传输系统

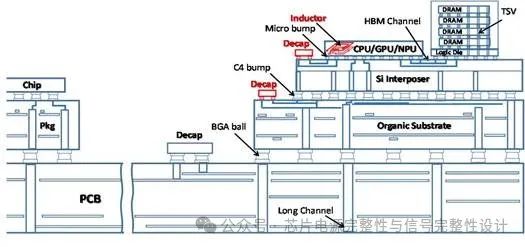

图1展示了采用Si interposer的典型高速系统(2.5D IC)概念图,包含网络芯片和HBM(高带宽内存)技术。假设CMOS芯片通过ubump技术安装在interposer上,而interposer通过可控塌陷芯片连接(C4)技术安装到有机封装上。有机封装采用球栅阵列(BGA)封装。系统中可包含一个或多个处理器(CPU、GPU或NPL)以及多个横向放置于Si interposer上的HBM模块。细间距布线实现了处理器与HBM之间的高密度互连。

图1: 高带宽内存(HBM)模块中采用interposer的高速系统截面图。

根据应用场景,硅载体可充当整个系统的一级封装。例如,处理器通过Si interposer中的互连与HBM系统中的DRAM通信。另一方面,Si interposer上的处理器可通过硅通孔、封装、板级走线和过孔与另一有机封装上的处理器通信。高速串行通道可支持PCI Express接口、高清多媒体接口(HDMI)或多种网络接口。

处理器与四个HBM之间的HBM interposer通道由密集互连构成,长度仅为数mm,间距紧密且电阻较高。该接口采用单端信号(时钟除外),且接收端通常未端接以节省功耗。串行接口的通道仅使用Si interposer中的TSV连接到有机封装和板级走线。通道损耗和色散较小,因此无需复杂的信号调理。

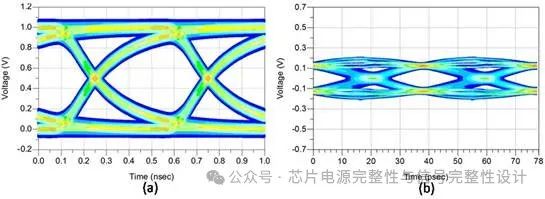

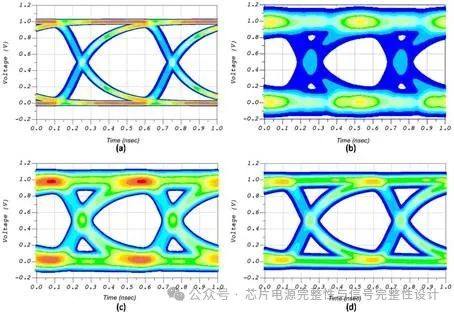

串行器/解串器(SerDes)接口采用差分信号和匹配端接,以在长距离通道中实现可靠通信。由于数据速率和通道损耗差异显著,并行与串行接口采用不同的信号技术,并对噪声和抖动的敏感度不同。图2(a)和(b)分别展示了2 Gbps和28 Gbps数据速率下,使用单端信号的并行接口与差分信号的串行接口的典型眼图,用于分析信号完整性性能。

图2: (a)并行接口与(b)串行接口的眼图

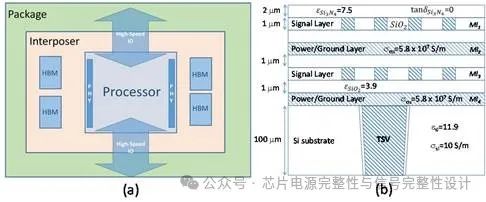

图3: (a)概念系统顶视图;(b)Si interposer的典型物理尺寸与材料特性

图3(a)展示了interposer系统的顶视图,包含一个处理器和四个HBM内存系统。虽然interposer可嵌入电容器或安装底面电容器,但本设计中interposer基板在高速接口两侧布置了芯片侧电容器。如图1所示,多个去耦电容器可放置在Si interposer和封装上靠近高速串行接口的位置。

Si interposer的尺寸通常尽可能小,以降低制造成本并优化高速通道。图3(b)展示了Si interposer的物理尺寸与材料特性,采用单侧四层再分布层(RDL)和TSV。铜导体层的金属厚度为1um,TSV直径为10um,TSV绝缘层厚度为0.5um。

interposer对通道性能的影响

A. 长距离通道(SerDes通道)

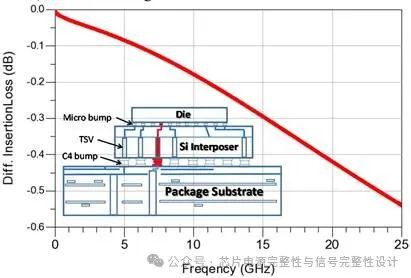

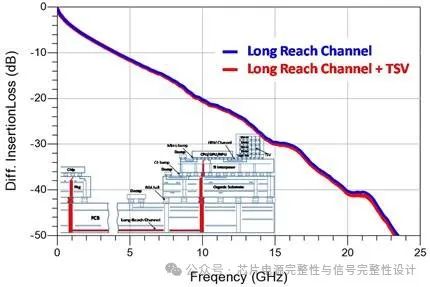

Si interposer对长距离SerDes通道插入损耗的影响可通过全波电磁仿真和频域分析进行评估。由于SerDes通道通常需要穿过interposerTSV、ubump、封装和板级互连,其总长度可达数十厘米。通过将Si interposer的TSV和ubump集成到通道模型中,可量化其对整体通道性能的影响。图4显示了TSV和ubump在25 GHz频段内的损耗小于-0.6 dB。由于Si interposer的低损耗特性,其对长距离SerDes通道(损耗接近-30 dB)插入损耗的影响极小,如图5所示。

图4: Si interposerTSV与ubump的信号损耗在25 GHz内低于-0.6 dB

图5: Si interposer对长距离串行通道插入损耗的影响极小。

B. 超短通道(HBM通道)

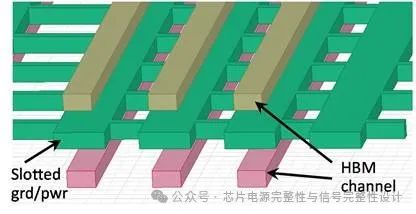

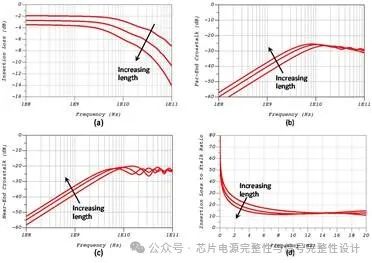

基于图3(b)interposer的物理尺寸与材料特性生成的网络参数,对处理器与HBM之间的HBMinterposer通道进行信号完整性分析。图6展示了采用三层金属化的HBM通道Si interposer互连结构,其中电源/地层采用穿孔平面。通过三维电磁仿真优化interposer走线宽度和间距,计算插入损耗与串扰。图7(a)展示了3 mm、4 mm和5 mm走线长度的HBM(interposer)通道插入损耗。与封装或板级走线不同,interposer走线的直流导体损耗较高,这是由于金属层厚度仅1um且走线宽度较窄。因此,插入损耗在直流和低频段约为2 dB。虽然增加走线宽度可改善导体损耗,但由于处理器与HBM之间的布线空间有限,宽走线设计并不总是可行。

图6: 采用三层金属化的HBM通道Si interposer互连结构

图7: HBMinterposer通道频域响应:(a)插入损耗,(b)远端串扰,(c)近端串扰,(d)3 mm、4 mm和5 mm通道长度的插入损耗与串扰比

图7(b)和(c)分别展示了HBM通道的远端串扰(FEXT)和近端串扰(NEXT)的功率总和。功率总和远端串扰(PSFEXT)和近端串扰(PSNEXT)为所有相邻对串扰贡献的代数和。在中低频段,串扰随通道长度增加而增大;但在高频段,通道损耗衰减耦合信号,串扰不再随频率增加。如图7(b)所示,2 Gbps数据速率下FEXT幅值低于-30 dB。在HBM通道设计中,仅考虑串扰可能产生误导,更相关的指标是插入损耗与串扰比(ICR)。该指标为设计人员提供了权衡设计的重要依据,允许更高的串扰和更低的通道衰减。图7(d)显示,在2 Gbps数据速率内,HBM通道的ICR超过25 dB。

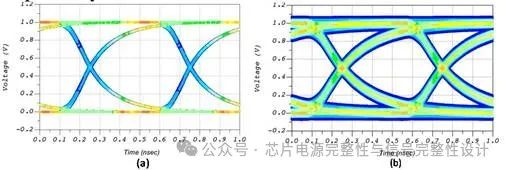

时域仿真结果表明,HBM通道接收端的眼图具有较大的电压和时序裕量。图8(a)和(b)分别展示了无串扰和有串扰时的接收眼图。

图8: Si interposer HBM通道接收眼图:(a)无串扰,(b)有串扰

电感器与interposer

A. 高速链路设计中的螺旋电感器

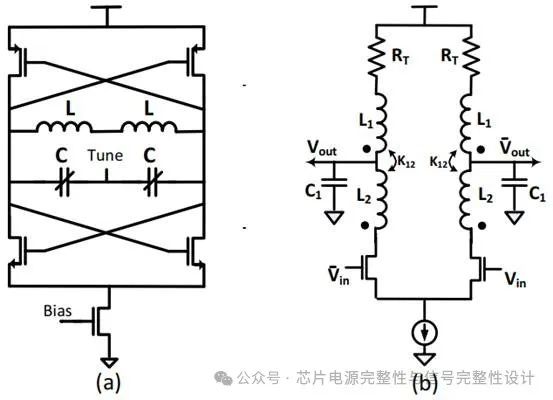

片上电感器是高速链路设计中的重要无源元件,用于实现LC-VCO及提升驱动器和接收器的带宽。图9(a)和(b)展示了电感器的两种典型应用。品质因数Q是LC-VCO设计的关键指标,决定了振荡器的性能、相位噪声和功耗。Q的定义为:

![]()

此外,电感器用于发射器和接收器以实现更好的阻抗匹配和带宽扩展。为最小化回波损耗并扩展带宽,需精确设计T型线圈的电感值。T型线圈设计需首先准确估算负载电容C,并设计电感器以补偿该电容。

图9: 电感器在(a)LC-VCO和(b)T型线圈峰值差分放大器中的简化电路示意图

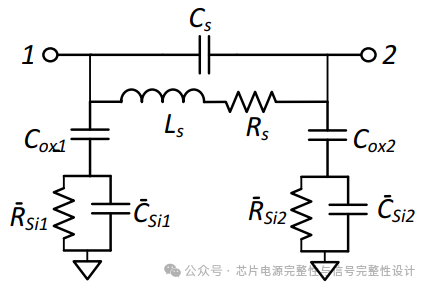

电感器通常采用硅工艺顶层金属层制造,因其介电层和导体更厚,可实现更高的自感。其结构为方形、六边形或八边形螺旋,占用较小芯片面积。图10展示了螺旋电感器的等效电路模型,电路参数通过全波电磁仿真获得。螺旋的电感、串联绕组电阻和馈通电容分别由Ls、Rs和Cs表示。螺旋与CMOS衬底之间的二氧化硅(SiO₂)电容由Cox表示。衬底通常为高掺杂p型材料并接地,其效应由并联的接地电阻Rs和衬底电容Cs表示。该电容增加了电感器的寄生电容,导致高频下电感与衬底的相互作用增强,可能降低电感值和谐振频率。

图10: 存在interposer时对称螺旋电感器的等效电路模型。

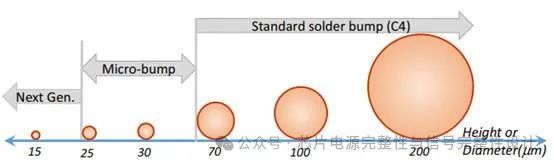

当螺旋电感器靠近硅衬底时,其周围磁场会渗入Si interposer,导致螺旋电感器周围反应场的损耗。时变磁场在衬底中感应出电场,金属层与衬底之间的电容耦合改变衬底电势并产生位移电流。时变磁场穿透衬底引起感性耦合并产生涡流。这两种电流均导致衬底损耗并降低螺旋电感器性能。若芯片与interposer之间的连接高度低至25um(未来可能进一步降低),该效应将更加显著。图11展示了ubump和标准焊料bump(C4)的高度与直径。随着柱状bump的普及,芯片与interposer间距可能进一步缩小,加剧螺旋电感器与Si interposer的相互作用。

图11: 当前工业中ubump与标准焊料bump的高度与直径。

典型Si interposer厚度为100um,最多包含四层金属(如图3(b)所示)。为体现高电阻率Si interposer的影响,螺旋电感器等效电路中需额外添加电容和电阻(CSi和RSi),如图10所示。因此,interposer会增大等效并联电容并降低等效并联电阻。

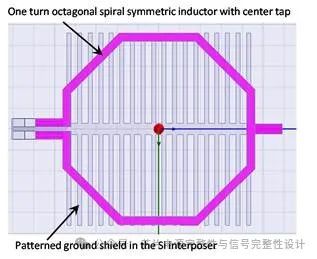

通过降低Si interposer中的路径电阻,可减少螺旋电感器与interposer的相互作用。具体方法是在Si interposer顶层布线层添加地屏蔽(类似芯片衬底中的做法)。地屏蔽可缩短螺旋金属与地之间的有效距离,并减少Si interposer耦合电阻,同时截断衬底中的电场。然而,实心地屏蔽可能适得其反,因为电感器的时变电磁场会感应出涡流。需将屏蔽图案化以切断涡流环路,从而提升品质因数Q。

研究对硅芯片顶层金属层中的单匝八边形螺旋电感器进行建模。该电感器为对称双端口结构,中心抽头。设计中Si interposer的平均电阻率为100 Ω·cm。如图12所示,螺旋电感器与衬底之间设有开槽地屏蔽,以最小化衬底损耗并实现高Q值。

图12: 带图案地屏蔽的螺旋电感器版图。

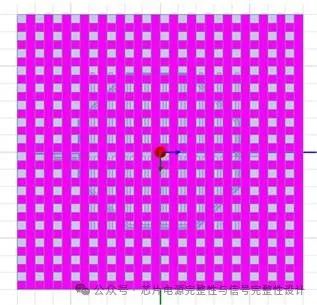

包含四层金属的100um厚Si interposer模型如图13所示。interposer制造设计规则要求金属层具有足够的覆盖率。本研究通过参数化金属层M13和M14的覆盖率来分析其对螺旋电感器L和Q的影响。覆盖率设计规则如下:(a)0%:M13和M14无金属;(b)25%:5um线宽/15um间距;(c)50%:10um线宽/10um间距;(d)75%:15um线宽/5um间距。图13展示了M13(水平线)和M14(垂直线)层上的50%覆盖率网格。

图13: M13(水平线)与M14

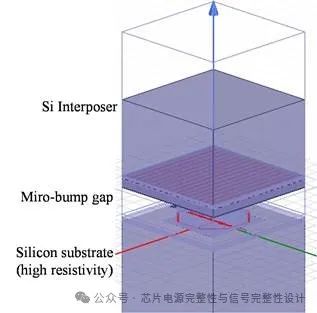

图14展示了包含芯片上螺旋结构和硅中介层的三维全波电磁仿真模型,芯片与中介层通过ubump连接。由于螺旋电感器下方通常不放置bump/ubump,模型中中介层与芯片之间由空气间隔。

图14: 螺旋电感器与中介层有限元模型(含ubump间隙与硅衬底)

为计算电感值L和品质因数Q,需将三维全波电磁仿真获得的S参数转换为Y参数,并基于应用场景选择计算公式:

单端或不平衡电感器(一端接地):

差分或平衡电感器:

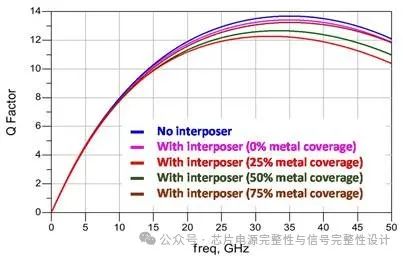

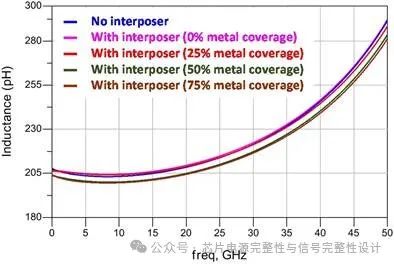

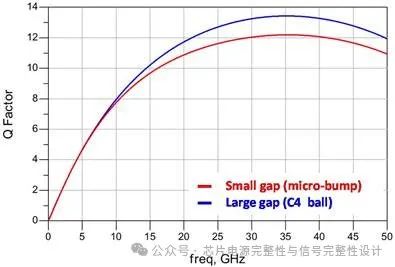

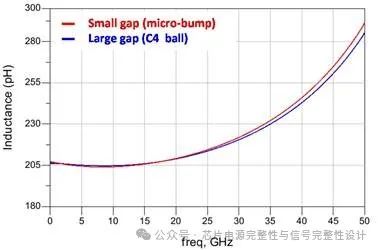

图15和图16分别展示了中介层金属覆盖率对Q因子和电感值LL的影响。无金属覆盖的中介层对Q因子影响最小,但受限于制造规则,实际设计需满足金属覆盖率要求。随着金属覆盖率从25%增至75%,Q因子逐步改善(表1)。此外,增大芯片与中介层间距(例如采用C4焊球替代ubump)可进一步降低中介层对电感器性能的影响(表2)。

图15:不同金属覆盖率下Q因子随频率变化曲线

图16:不同金属覆盖率下电感值L随频率变化曲线

图17:ubump与C4焊球间距对Q因子的影响。

图18:ubump与C4焊球间距对电感值L的影响

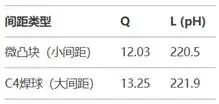

表1:金属覆盖率对Q因子与电感值的影响

表2:间距类型对Q因子与电感值的影响

电源分配网络阻抗分析

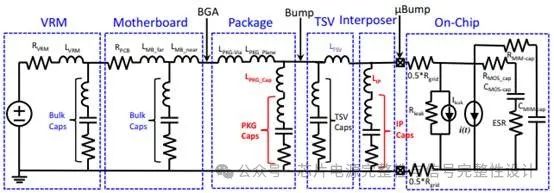

·图19展示了芯片-中介层-封裝-板级的层级式电源分配网络(PDN)模型。PDN阻抗特性主要由封裝电感与芯片电容的并联谐振主导,其峰值频率取决于封裝电感、芯片电容及互连电阻。中介层去耦电容的电阻特性会削弱其对中频噪声的抑制效果。

图19:层级式电源分配网络模型

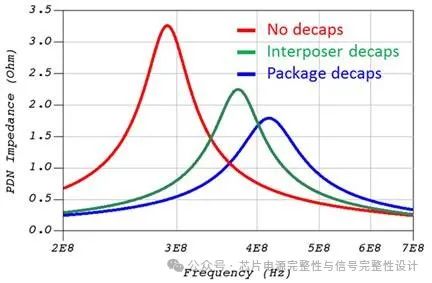

为评估中介层与封裝去耦电容的性能,在高速接口两侧各放置8个电容。仿真结果显示:

1.无去耦电容:PDN阻抗在300 MHz处出现显著峰值。

2.仅封裝去耦电容:峰值阻抗降低约50%,谐振频率移至420 MHz。

3.仅中介层去耦电容:谐振频率移至380 MHz,改善效果有限(图20)。

图20:不同去耦配置下的PDN阻抗对比(无/仅封裝/仅中介层)

时域仿真进一步验证了去耦电容对SSO(同步开关输出)噪声的抑制效果。图21显示,封裝去耦电容可显著缩小SSO噪声引起的眼图闭合,而中介层去耦电容的效果较弱。

图21:HBM通道眼图:(a)无SSO噪声,(b)含SSO噪声,(c)中介层去耦电容抑制SSO噪声,(d)封裝去耦电容抑制SSO噪声

以上通过信号与电源完整性分析,得出以下结论:

1.信号完整性:

o硅中介层对长距离SerDes通道影响可忽略,但HBM通道需优化导体损耗与串扰比(ICR)。

o采用图案化地屏蔽可将螺旋电感器的Q因子降幅控制在5%以内。

2.电源完整性:

o封裝去耦电容因低电感路径更有效,可将PDN阻抗峰值降低50%。

o中介层去耦电容受互连电阻限制,抑制中频噪声效果较弱。

3.系统性能:

o封裝去耦电容显著改善HBM通道的眼图裕量,支持更高数据速率。

设计建议

- 硅中介层设计需平衡制造规则(如金属覆盖率)与电学性能。

- 高频系统中,建议优先采用封裝去耦电容,并结合中介层电容优化中频阻抗。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?