fpga以太网接口设计,支持udp和tcp协议,纯verilog手写代码,纯逻辑实现udptcp协议,mac层和tcp/ip层模块是分开的,物理接口可根据要求定制,目前的百兆网版本接口为RMII,千兆网版本接口为GMII转RGMII,Gmii和rgmii均下板测试过,tcp模块支持校验和重发功能,可和电脑端进行一对一通信。

可封装为axi接口(axi stream 或 axi lite)。

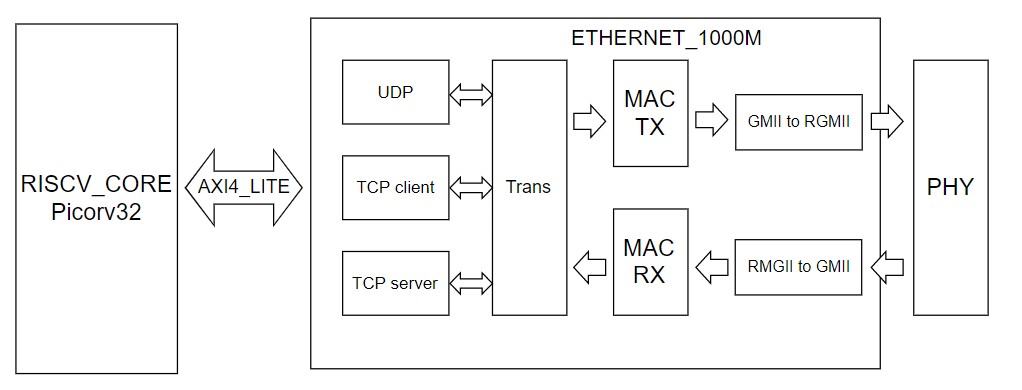

适合简单基础通信和参考学习,工程基于vivado,已有代码框图如下,其中图三为soc版本,网口为从机,riscv核为主机,通过axi interconnect桥接,也可灵活增加其他从设备。

非soc版本就只有网口的硬件代码,如图四。

可以和网络调试助手和python或c的socket通信。

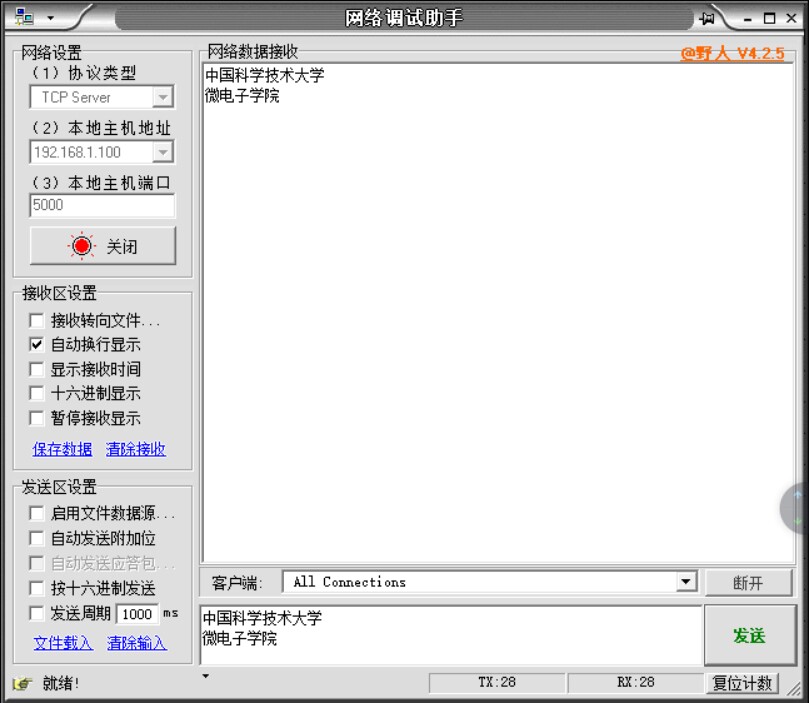

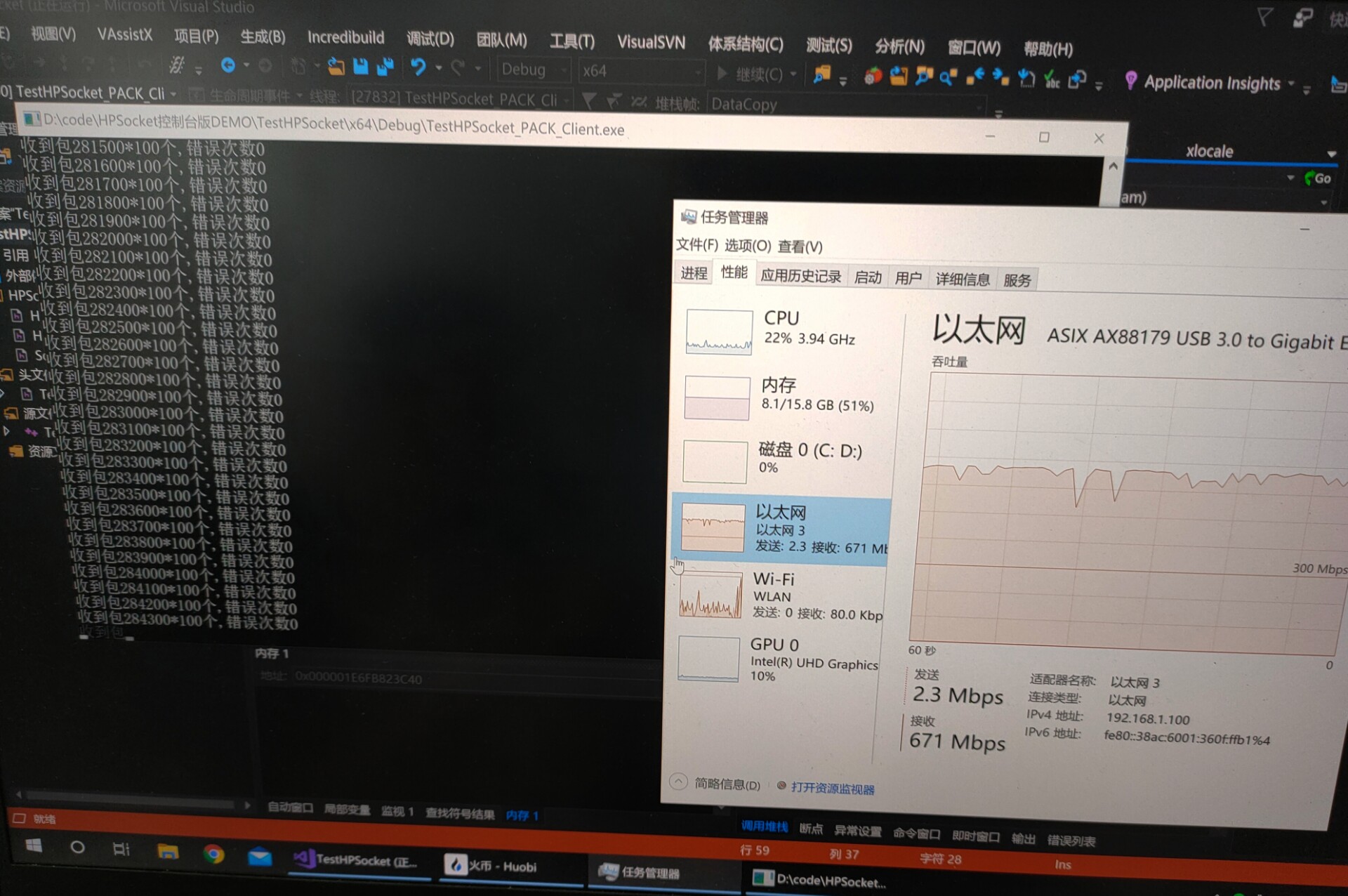

通信截图如图五。

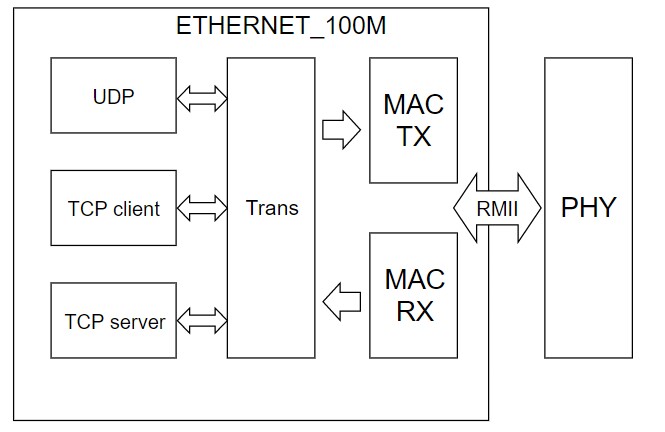

图六为百兆网版本框图。

注:资源消耗将近2000lut(xilinx fpga)

百兆版本在nexys4 ddr 开发板测试,千兆版本在黑金artix7 200t开发板和xilinx kc705开发板测试。

附带四份文档,1为抓包实测的文档说明,2为以太网协议介绍的ppt,3为tcp实现的代码说明,4为报文基本概念

ID:691000624388382769

云赐记

FPGA以太网接口设计

在计算机网络领域中,以太网一直扮演着重要的角色。为了满足不同需求,人们针对以太网接口进行了各种设计和创新。本文将围绕FPGA以太网接口设计展开讨论,重点关注其对UDP和TCP协议的支持,并以纯Verilog手写代码的方式实现。

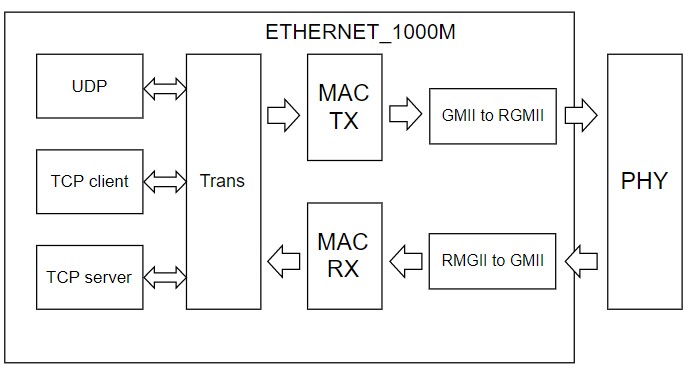

首先,我们了解一下FPGA以太网接口设计的一般特点。该设计包括MAC层和TCP/IP层模块,两者相互分离。物理接口可根据需求进行定制,目前百兆网版本采用的接口为RMII,千兆网版本采用GMII转RGMII接口。这两种接口均经过下板测试,能够确保其正常工作。另外,TCP模块支持校验和重发功能,从而提升通信的可靠性。此外,该设计可封装为AXI接口,可以选择AXI Stream或AXI Lite。

FPGA以太网接口设计适用于简单的基础通信和学习参考。在工程实现中,我们基于Vivado进行开发,并已经拥有一套完整的代码框图。其中,图三展示了SOC版本的设计,网口作为从机,RISC-V核作为主机,通过AXI Interconnect进行桥接。除此之外,我们还可以根据需求灵活增加其他从设备。

如果不需要SOC版本,只需考虑网口的硬件代码,如图四所示。这种设计可以与网络调试助手、Python或C的Socket进行通信。图五展示了通信截图。

对于百兆网版本的设计,我们提供了详细的框图,如图六所示。需要注意的是,这种设计消耗的资源接近2000 LUT(Xilinx FPGA)。

我们在Nexys4 DDR开发板上测试了百兆版本,而千兆版本则在黑金Artix-7 200T开发板和Xilinx KC705开发板上进行了测试。为了更好地理解FPGA以太网接口设计的实际应用,并对其性能进行评估,我们提供了四份附加文档。第一份文档说明了抓包实测的结果,第二份文档是以太网协议介绍的PPT,第三份文档解释了TCP的实现代码,第四份文档则介绍了报文的基本概念。

综上所述,FPGA以太网接口设计在满足不同需求的同时,还能提供高效可靠的通信。它的设计特点包括对UDP和TCP协议的支持、纯Verilog手写代码的实现、分离的MAC层和TCP/IP层模块、灵活定制的物理接口、支持校验和重发功能以及可封装为AXI接口等。通过在不同开发板上进行测试,并提供相关文档,我们可以看到FPGA以太网接口设计的实际应用和性能表现。这一设计不仅适用于简单的基础通信,还为学习者提供了宝贵的参考资料。

相关的代码,程序地址如下:http://imgcs.cn/624388382769.html

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?