目录

1. 模块界面与功能介绍

1.1 测试环境

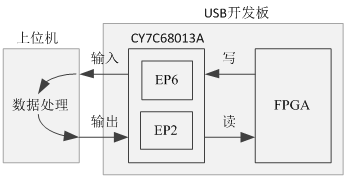

图1为上位机的硬件测试环境,USB芯片CY7C68013A被设置为SlaveFIFO工作模式,分别使用EP6和EP2作为上位机的输入和输出端点,端点的大小为512byte,端点缓存大小为2Kbyte。EP6带有一个满标志位,EP2带有一个空标志位,FPGA通过判断端点的状态标志位来控制数据的读和写。

下环路测试中,FPGA为主端,上位机为从端,FPGA首先向USB写数据并判断EP6是否写满,写满后就停止写操作并切换至读操作,当EP2被读空时,就进行下一个写操作。上位机端不断的从EP6接收数据,当接收数据的数量达到指定值时,将指定数量的数据输出至EP2中。

订阅专栏 解锁全文

订阅专栏 解锁全文

2391

2391

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?