FSM OneHot

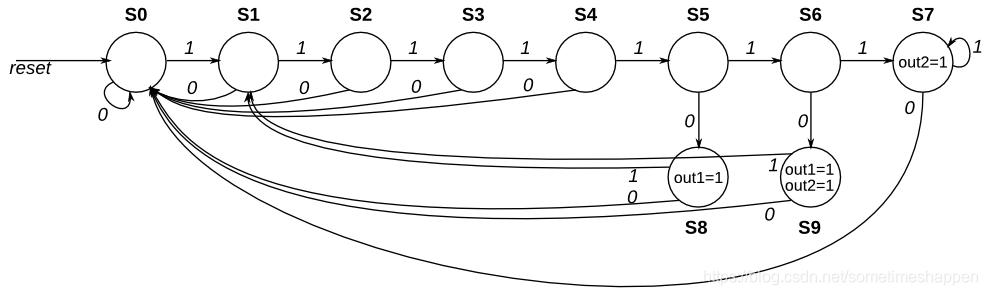

Question:Given the following state machine with 1 input and 2 outputs:

Suppose this state machine uses one-hot encoding, where state[0] through state[9] correspond to the states S0 though S9, respectively. The outputs are zero unless otherwise specified.

Implement the state transition logic and output logic portions of the state machine (but not the state flip-flops). You are given the current state in state[9:0] and must produce next_state[9:0] and the two outputs. Derive the logic equations by inspection assuming a one-hot encoding. (The testbench will test with non-one hot inputs to make sure you’re not trying to do something more complicated).

分析:对于one-hot类型的题,一般是将state分成1bit的形式分别进行考虑,若是用always块+case来进行分类的话会使得问题复杂化。

module top_module(

input in,

input [9:0] state,

output [9:0] next_state,

output out1,

output out2);

assign next_state[0] = !in&(state[0]|state[1]|state[2]|state[3]|state[4]|state[7]|state[8]|state[9]);

assign next_state[1] = in&(state[0]|state[8]|state[9]);

assign next_state[2] = in&state[1];

assign next_state[3] = in&state[2];

assign next_state[4] = in&state[3];

assign next_state[5] = in&state[4];

assign next_state[6] = in&state[5];

assign next_state[7] = in&(state[6]|state[7]);

assign next_state[8] = !in&state[5];

assign next_state[9] = !in&state[6];

assign out1 = state[8]|state[9];

assign out2 = state[9]|state[7];

endmodule

这篇博客讨论了一种使用一热编码(one-hot encoding)实现的有限状态机(FSM)。FSM具有1个输入和2个输出,并且详细给出了next_state和输出的逻辑赋值。通过分析给定的逻辑方程,可以看出每个状态如何根据输入in和当前状态state转换。同时,输出out1和out2的计算也进行了说明。测试 bench 将会验证该实现是否能够处理非一热编码的输入,以确保逻辑的正确性。

这篇博客讨论了一种使用一热编码(one-hot encoding)实现的有限状态机(FSM)。FSM具有1个输入和2个输出,并且详细给出了next_state和输出的逻辑赋值。通过分析给定的逻辑方程,可以看出每个状态如何根据输入in和当前状态state转换。同时,输出out1和out2的计算也进行了说明。测试 bench 将会验证该实现是否能够处理非一热编码的输入,以确保逻辑的正确性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?