AXI Bus相关

AXI Bus整理

本篇并不是详细的整理,只是学习过程中的一点简单的记录,如有什么细节上的问题,可以在评论区留言,我会尽力整理后更新在本帖上。

1. 架构

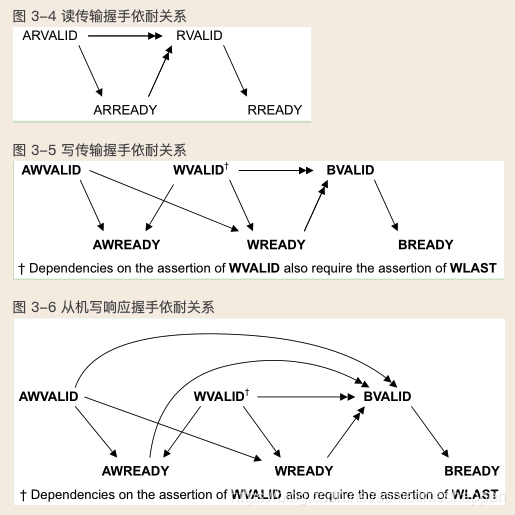

在学习的过程中,感觉AXI大体上和ICB Bus差不多,只是多了一些信号,相对复杂了一点,从2个channel(command&respond)变成了5个channel,读为2个(aadr&data),写为3个(addr&data&respond),分别的依赖关系如下图所示:

除了每个channel都有自己的握手外(valid表示准备好了数据,ready表示可以接收),AXI Bus是基于BURST传输的(多了XLAST、XLEN、XSIZE、INCR等信号)。对于ICB来说,连续读写需要一个地址对应一个数据,而BURST传输相当于将这一过程细化(也可以说是完整化),通过初始地址、数量以及每次地址增量来实现连续传输。

2. 窄传输和非对齐传输

这里具体可以在Reference中其他博主的介绍中查看,写的都比较详细。

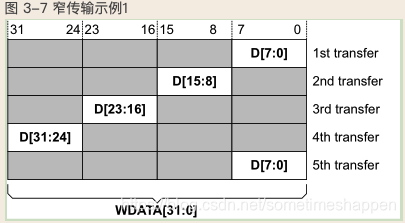

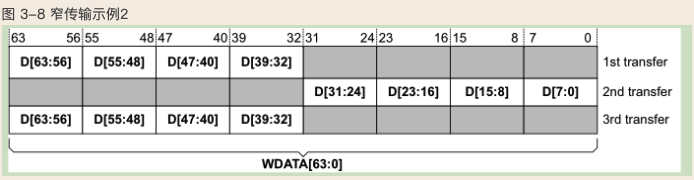

窄传输:

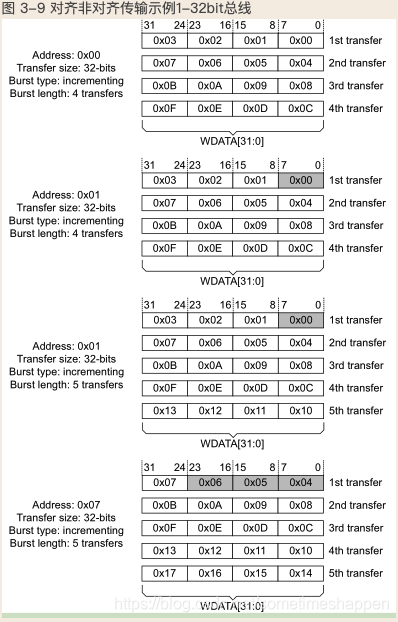

非对齐传输:

3. AXI协议用事务ID tags来处理多地址和乱序传输

具体可见Reference【1】,之前讨论过类似问题,觉得还挺重要的。

3. AXI-Lite/AXI4/AXI-Stream

AXI-Lite:不支持Burst读写,适用于低速外设或控制;

AXI4:支持Burst读写,适用于数据和地址传输;

AXI-Stream:无地址线,是一种连续流接口,适合做实时信号处理;

实践时遇到的相关问题

(目前还没有,有待更新)

Reference

[1] https://www.cnblogs.com/mikewolf2002/p/10322532.html

[2] https://www.cnblogs.com/gujiangtaoFuture/articles/10137170.html

[3] https://wenku.baidu.com/view/7c424c17e3bd960590c69ec3d5bbfd0a7956d5b9.html

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?