移位运算在诸如浮点数运算、可变长度编码以及位矢量的检索与拼接等数字信号处理中有着广泛的应用。现代数字信号处理器和微处理器中绝大部分都具有专用的移位处理单元或是在其核心运算单元-----ALU中集成有相关的移位电路。典型的移位操作包括算术左移或右移以及循环左、右移位等。移位电路有多种结构形式,但应用最为普遍的是桶型移位器(barrel shifter)电路。

1.移位操作的类型

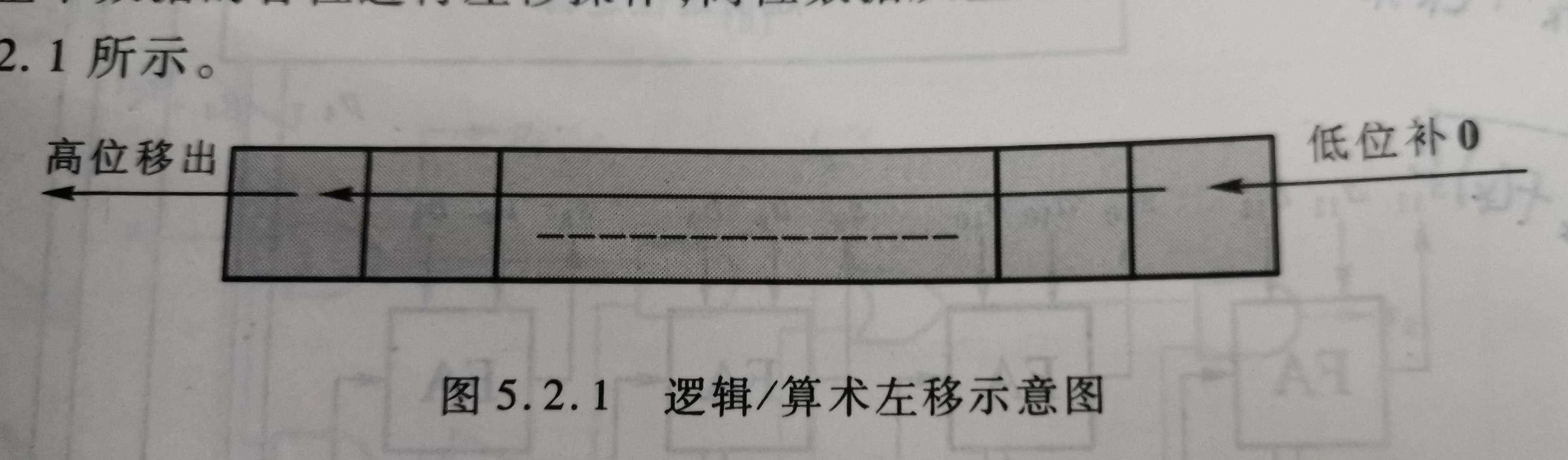

1.逻辑/算术左移

整个数据的各位进行左移操作,高位数据从左边移出,低位数据补零。

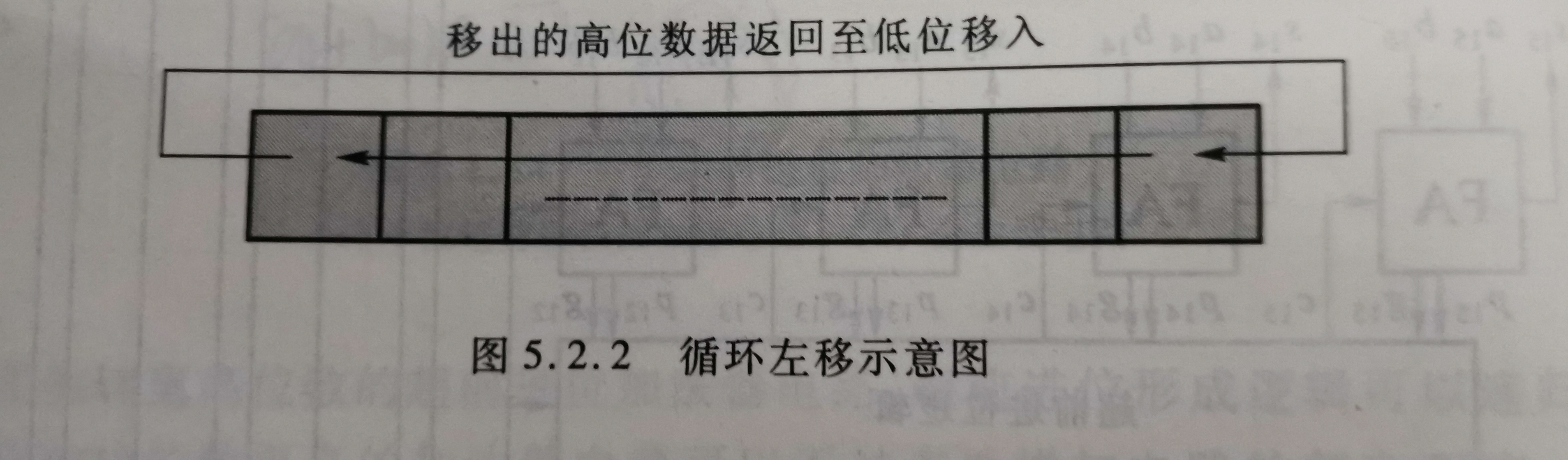

2.循环左移

整个数据的各位进行左移操作,从左边移出的高位数据返回至低位移入。

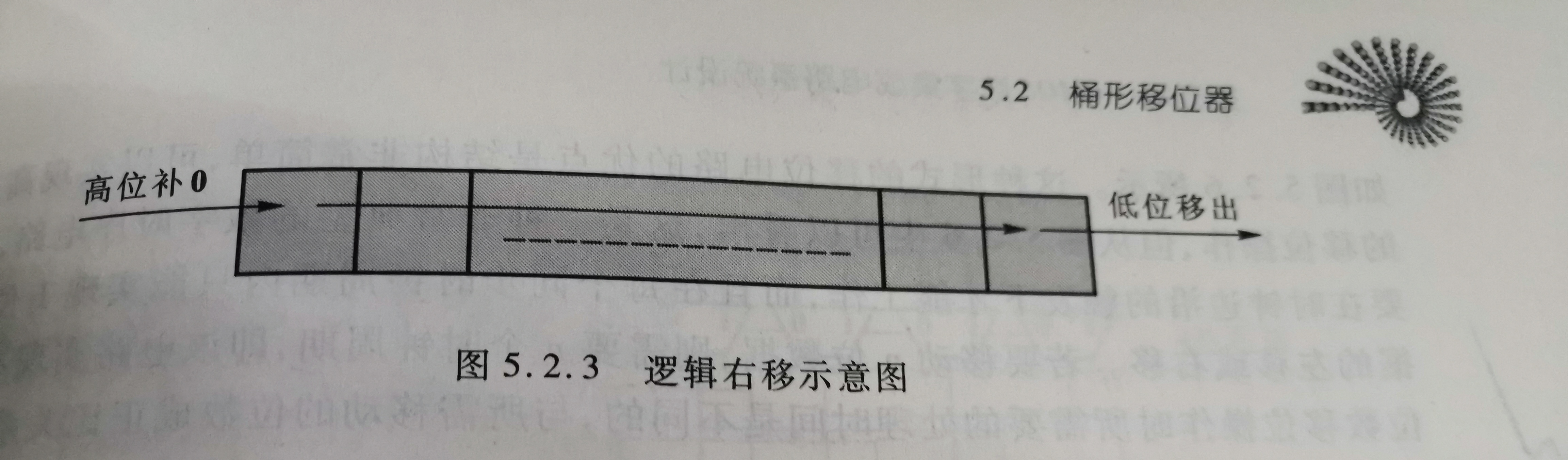

3.逻辑右移

整个数据的各位进行右移操作,低位数据从右边移出,高位的移出位补0

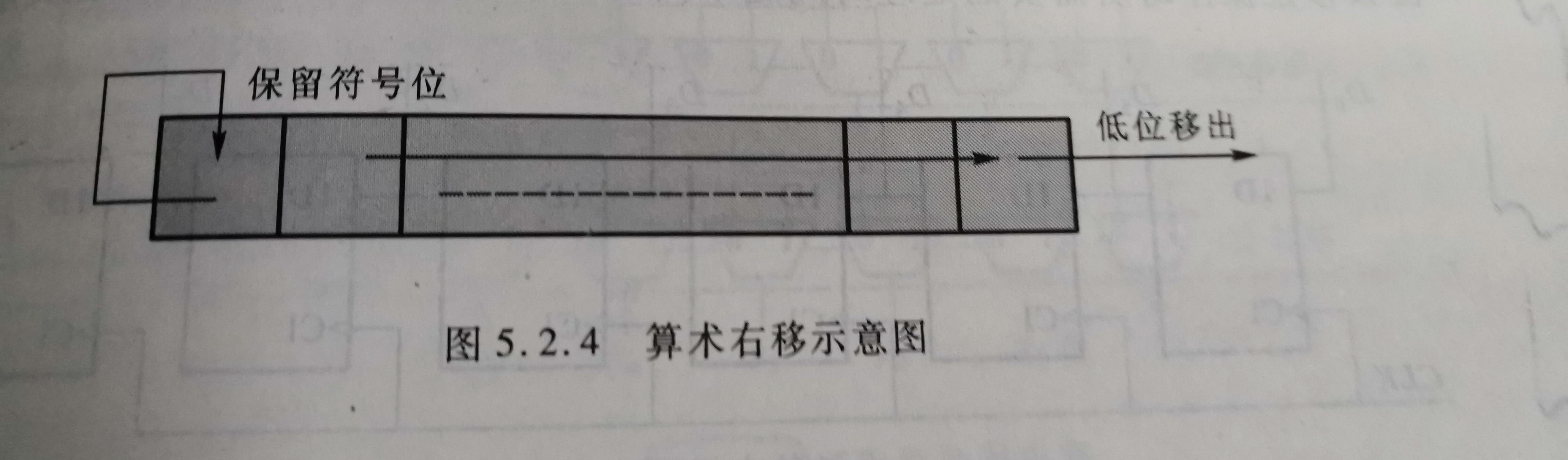

4.算术右移

数据的最高位即符号位在移位过程中始终保持不变,其余各位进行右移操作。

5.循环右移

整个数据的各位进行右移操作,从右边移出的低位数据返回至高位移入。

2.用触发器构成的移位电路

采用触发器构成的移位寄存器电路可以实现移位的功能,其电路结构形式如下图所示。

这种形式的移位电路的优点是结构非常简单,可以实现高速的移位操作。是一个典型的数字时序电路,但是他需要在时钟边沿的触发下才能工作,而且在每个同步时钟周期内只能实现1位数据的左移或右移。若要移动N位数据,则需要N个时钟周期,因此其移位效率低。

桶型移位器电路

桶型移位器是由分级排列的多个数据选择器(2:1MUX)电路构成的,每一级(每行)MUX电路完成的移位操作的位数是2的幂次方或是不做移位而将本级的数据直接送入下一级MUX电路的输入端

如下图所示是一个8位数据输入的逻辑右移桶型移位器电路。

该电路由三级MUX组构成,从上至下每一级MUX组的移位位数分别是4位、2位和1位。每一级是否进行移位由移位控制信号b2b1b0控制。假设需要对输入数据逻辑右移5位,则b2b1b0=101,此时最上一级MUX组将输入数据逻辑右移4位,中间级MUX组不移位而将本级输入数据直接送入下一级的输入端。最低一级的MUX组将本级输入数据逻辑右移1位后将完成移位后的结果输出。

下图为一个8位输入数据的循环右移桶形移位器电路,该电路与上述逻辑右移电路的不同之处在于其每一级MUX组中右移出的数据线被接至其高位的相应数据输入端上。(原先接0)

桶型移位电路完全靠数据选择器组及其数据输入输出端的连线方式来实现各种类型的移位操作,全部电路由组合逻辑电路构成,其移位的速度取决于MUX组分级的层数,与移位操作的位数无关。

5532

5532

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?