带芯片实现的数字秒表电路设计

摘要

本文概述了使用Tanner S‐Edit和L‐Edit设计环境进行秒表电路的设计、仿真与测试。该芯片的构型包含按钮同步器、主计数器单元和七段译码器。芯片的原理图和布局采用Tanner设计套件完成。在制造后,生成了测试向量,并应用于仿真和实际芯片上。通过改进,最终创建出通过测试的黄金设计版本芯片。同时尝试将此设计(包括缺失的模块)实现于定制可编程逻辑器件(CPLD)上。

1. 引言

数字秒表是一种在工业和日常生活中广泛使用的重要计时装置。与传统的机械秒表相比,数字秒表的主要特点是低成本、高精度和高可靠性。本文将从仿真和测试两方面介绍一种数字秒表电路的结构和性能。该设计提供启动、停止和复位功能,通过七段显示器输出,时间分辨率为0.1秒。

数字秒表中的主要组件是主计数器。设计采用4位主计数器,相较于5位设计,可减少空间占用并降低复杂度。主计数器被划分为多个较小的模块,包括不同位数的计数器和一个输出控制单元(OCU)。接下来是芯片设计、仿真和布局。原理图使用Tanner S‐Edit开发,并通过 ModelSim仿真进行测试。当仿真结果证明设计行为符合预期后,在L‐Edit中进行布局。对于制造后测试,采用了多种方法,包括测试向量、仿真、物理芯片测试以及系统测试。

数字定时装置的设计多年来一直被研究。许多设计通过FPGA或CPLD [1]‐[6]实现。基于 FPGA的数字秒表的设计与实现。[1]提出了一种基于Quartus II软件平台,采用VHDL和原理图输入的数字秒表。所设计的电路已在FPGA上实现,并下载到Cyclone EP2C5Q208C8器件进行测试。结果表明,[1]设计了一个实现时间显示、开始和停止、复位以及溢出报警功能的电路。[2]的作者提出了一种数字时钟日历,包含比较器、计数器、多路复用器和解码器等组件。该设计使用VHDL实现,并在Spartan®‐6 FPGA SP605评估套件上完成验证。

本文的其余部分组织如下。第二节简要介绍设计仿真与布局。第三节描述集成。制造后测试在第四节中描述。最后,第五节得出结论。

2. 设计仿真与布局

2.1. 按钮同步器

采用时序逻辑进行设计。根据输入“启动”和“停止”、输出“运行”以及当前状态和下一状态 “Q0”和“QN”建立了逻辑真值表。从真值表中推导出“运行”和“QN”的与和或逻辑表达式。应用德摩根定律对这些表达式进行转换,从而使用与非逻辑。这减少了门数量和复杂性,因为在布局中所需的反相器更少。

2.2. 主计数器

为了简化设计,主计数器的设计过程中,对该模块的整体功能进行了分析,并将其划分为多个模块。这种设计方法也使得主计数器的布局设计更加简便。用于设计主计数器的模块包括:两位计数器、十位计数器、五位计数器以及输出控制单元(OCU)。所有模块均采用时序逻辑进行设计,以实现同步设计,因此整个主计数器为一个同步设计。

主计数器设计中使用的三个计数器模块旨在降低输入时钟频率至正确的时序,以确保四位数字中每一位的输出值都能在正确的时间更新,从而保证主计数器输出的准确性,同时保持完全同步的设计。十位计数器和五位计数器均具有4位二进制输出,每当计数器在其“输入递增”引脚接收到高电平时,就会更新并输出对应位的当前值。十位计数器输出二进制0‐9,五位计数器输出二进制0‐5。当计数器达到最大值时,会在“输出递增”引脚输出高电平,该信号连接至下一个计数器。选择此方法是为了通过每个计数器递增下一个计数器来实现正确的数字序列输出。在主计数器单元的设计中采用的模块化方法在此取得了成功,它使得十位计数器的设计可被两位计数器复用,从而生成了一个二十位计数器,减少了原理图和布局设计时间。

输出控制单元(OCU)被设计用于接收所有计数器的输出值,向显示器输出正确的信号以点亮相应的数字位,并将对应的数字值发送至解码器。输出控制单元(OCU)按顺序依次更新每一位数字,在200赫兹的工作频率下,4位时间值的刷新率为50赫兹。该速度足以使第一位与最后一位数字更新之间的延迟不被察觉。时序逻辑通过构建一个具有四个状态的算法状态机(ASM)来实现,每个状态对应一个待更新的数字位。该设计由两个触发器构成,其输出控制多路复用器(MUXs)和组合逻辑,分别将正确的计数器值发送至解码器并点亮相应的显示器数字位。多路复用器(MUXs)使用组合逻辑设计,随后以类似于按钮同步器的方式转换为与非门结构。

使用System Verilog测试平台验证了主计数器和按钮同步器的功能,这使我们能够观察输出波形并相应地改进设计。

2.3. 七段译码器

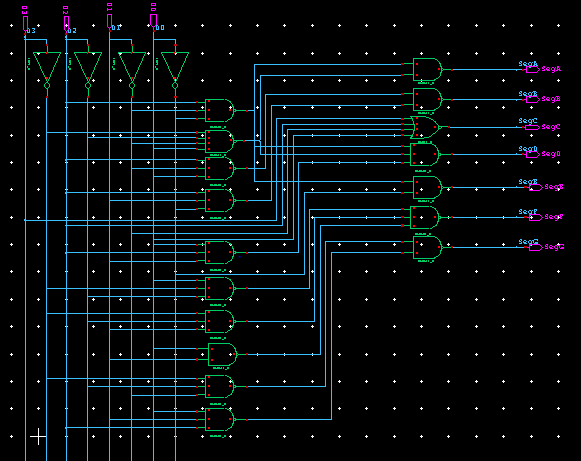

通过分析正确点亮七段显示器所需的连接方式进行设计。由于所选的七段显示器为共阴极类型,当输入到各段的信号为逻辑0时,显示器被点亮。为此建立了逻辑真值表,以显示所有输出的位序列,并利用卡诺图方法推导出七段译码器中每个输出所使用的方程。在最终设计中采用了与非逻辑,从而减少了总门数量以及后续布局设计所需的布线工作量。如图1所示的译码器原理图最终版本中,总共仅有17个门。当在T‐spice中对七段译码器进行仿真时,该模块的输出正确地遵循了逻辑真值表,并输出了所有正确的位来控制七段显示器。

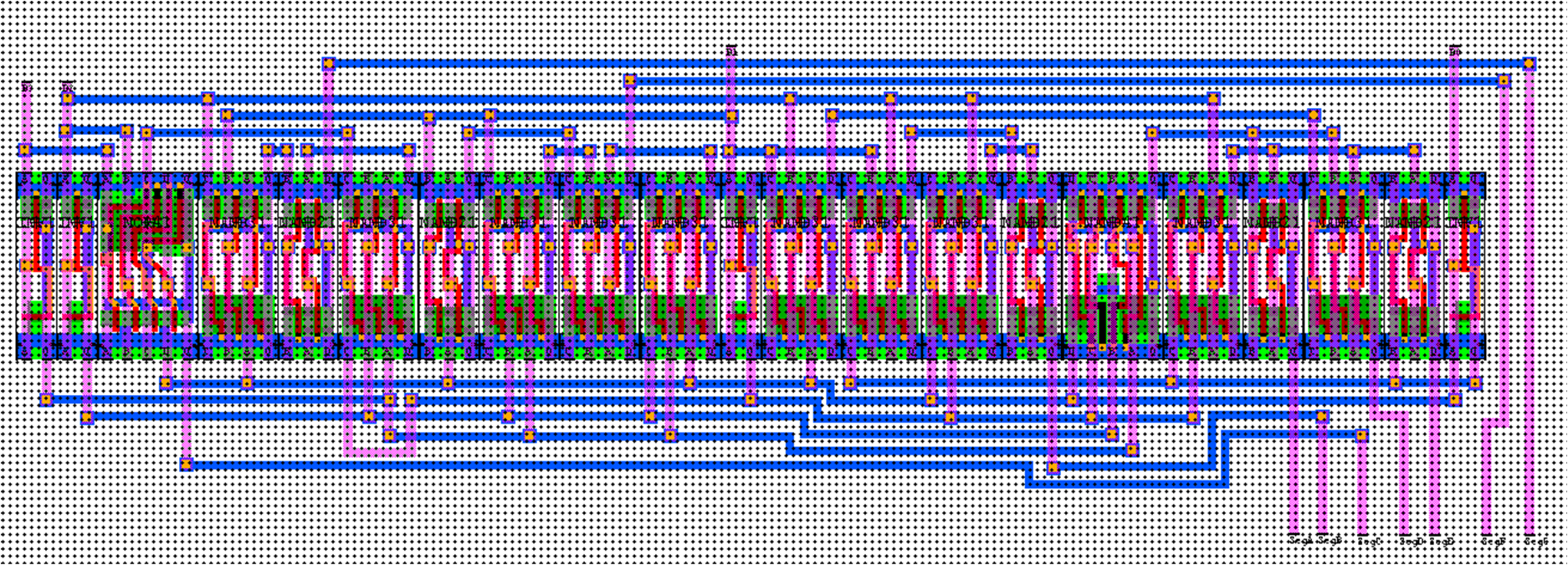

在七段译码器的原始布局中,整个电路被分为两部分,中间由连接导线相连。然而,在全芯片集成过程中发现,由于可用空间不足,该设计无法容纳。因此,对该设计进行了修改以减小尺寸。电路被改为一体式结构,所有逻辑门排列成一条直线。所有输出导线移至电路底部,而输入导线保留在顶部。这不仅降低了布线难度,还最小化了电路尺寸。此外,逻辑门的排列也经过优化,确保了所用导线数量的减少。七段译码器的布局如图2所示。

3. 集成

完成布图和布局后,下一步是将各个独立的电路整合到一个设计中,以便在完成的芯片上进行制造。由于芯片上的可用空间有限,因此首先对所有设计模块的布局进行了审查和修改,以减少它们的尺寸。在集成过程中遇到的主要问题是缺乏足够的空间来放置正确间距的走线,这些走线用于将模块连接到相应的输入/输出连接。尽管尝试了使用芯片两层的不同方法,但仍未能找到解决方案。

为了获得更多的可用空间,主计数器从4位设计缩减为3位设计。然而,布线仍然没有足够的空间。这一更改还意味着主计数器中控制小数点的逻辑必须修改以适应3位设计。在最终集成时,主计数器被从芯片设计中移除,以便为其余模块的正确布线腾出空间。

4. 制造后测试

4.1. 测试向量

由于显示器只能显示0到9的数字,因此开发了测试向量来测试该模块的功能。测试向量用于检查系统在遍历从0到9的二进制值时的响应情况,并观察输出。通过遍历这些二进制值,可对所有输入和输出引脚进行检测,以发现卡在0和卡在1的故障。

测试按钮同步器相对简单。第一版侧重于对该模块的功能测试,通过参考真值表并为每一行生成测试向量来完成。生成这些向量后,发现其中已覆盖了大量固定为1和固定为0的故障。由于该同步器仅包含一个触发器和少量逻辑门,因此只需13个向量即可对输入和输出上的所有固定为1和固定为0故障进行穷尽测试。

主计数器具有输入A13、A14、A18以及输出Q7到Q16。A13为主计数器的时钟,A14为复位信号,A18为使能信号。Q7到Q11是控制第1位到第5位七段显示器更新的输出信号,在本设计中Q11(即第5位)未被使用,应始终保持为0。第一位显示秒表的分钟,第二位和第三位表示秒,第四位表示十分之一秒。Q12是七段显示器的小数点信号。根据要求,第一和第三位的小数点在计数过程中应始终点亮,以指示不同单位之间的分隔。Q13到Q16是七段显示器上所需数字的二进制输出,这些信号同时也是七段译码器的输入。测试向量为功能测试向量,因其覆盖了输入和输出上的卡在1和卡在0的故障,从而减少了进行全面综合测试的需求。第一组测试向量用于复位主计数器,此时不施加“Clock”或“RunIn”信号。其余测试向量则侧重于观察当输入“RunIn”施加时4位主计数器的输出情况。

4.2. 仿真

将S‐Edit原理图导出为Verilog文件后,我们可以在ModelSim中使用相应的测试平台对每个模块进行测试。通过使用ModelSim作为我们的仿真平台,可以观察测试向量应用到模块时产生的错误,以及每个模块的输入和输出生成的波形。

使用导出的Verilog测试平台,对所有模块进行了测试,以检查模块或测试向量是否存在错误。当将测试向量应用于提交的按钮同步器设计时,通过ModelSim仿真发现了输出中的错误。结果发现该按钮同步器未能按预期工作。当输入信号Go和Stop同时施加时,Stop输入应覆盖Go输入,从而使输出Run不被置位。然而实际发现,在Stop之后断言Go时,Run仍被置位。经过进一步测试,发现该错误的原因是两个输入可以相互覆盖。一旦发现此错误,便修正了按钮同步器的原理图,并将此修改应用到黄金设计中。其余用于测试其他模块的测试向量均按预期正常工作。在包含前述修复后,完整的1236个测试向量的统一集合也如期通过了测试。

4.3. 芯片测试

在手表测试中,使用了三个带上拉或下拉电阻的按键,分别用于复位、启动和开始,并连接到芯片上相应的输入引脚。七段显示器已通电,并与芯片的输出引脚相连。该秒表的测试设置如图3所示。两个七段显示器的A至G及Di端口在面包板上连接,以从另一芯片测试5位320Hz秒表。通过另一芯片中的主计数器来测试电路的功能。第一个七段数码管的第4位用作秒表的第一位数字,其余第2到第5位则使用第二个七段数码管显示器上的4位数字。由于七段译码器与主计数器之间没有内部连接,因此需手动连线。当按下启动按钮时,秒表开始运行。按下停止按钮时,成功保持七段显示器上的数值并暂停秒表,而复位按钮则使秒表重新从“00.00.0”开始计时。

另一个测试使用了另一芯片的3位版本。由于只需要显示3位数字,因此移除了第一个七段显示器。将位置开关切换到相应数字并设置时钟频率为160赫兹(3位秒表所需的频率)后,按下启动按钮,秒表开始工作。注意到当达到99.9秒的最大值时会发生溢出,显示的数字会返回到00.0并继续计数。两个秒表均表现出精确计时,在1%精度范围内。由于该设计在芯片上缺少主计数器,因此需要一个CPLD,并加载由本设计生成的完整Verilog代码,以验证秒表是否正常工作。

用于测试的CPLD是Il Bagatto Max V 5M240Z100CT。通过Quartus软件,将S‐Edit生成的整个设计的Verilog代码转换为.svf格式文件,以便能够加载到CPLD [2]中。Il Bagatto上的引脚排列已设置编译后引脚会随机分配。在引脚配置步骤中,需要对部分引脚进行重新排列,如附录E所示。重新排列后,整个Verilog文件被编译并下载到CPLD上。该电路工作正常。

5. 结论

本文描述了一个完整的带有芯片实现的数字秒表电路。该芯片的设计原理图较为理想,仅在按钮同步器部分存在一处错误,已在最终黄金设计中得到修正。然而,在实现各个电路的物理布局时,发现无法将所有模块放入芯片的分配空间内。因此,用于制造的最终设计排除了数字秒表电路中的主序列器模块。制造后测试的结果更为成功。统一测试向量识别出芯片存在一个关于按钮同步器在同时按下启动和停止时响应的问题,该问题已在最终黄金设计提交中修复。

我们尝试将黄金设计实现到一块复杂可编程逻辑器件(CPLD)上,以验证我们的秒表不仅能 在仿真中运行,也能在物理硬件上正常工作。总体而言,该设计为数字秒表设备提供了一种可靠且具有成本效益的解决方案。未来改进方面,可进一步优化设计以延长最大计时长度,或将精度提升至0.001秒。

208

208

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?