一、概述

在完成布局规划、布图规划、时钟树综合以及布线等步骤之后,芯片设计的物理实现部分已经基本确定。将在ECO阶段对时序以及DRC等部分的违例进行进一步的修复。

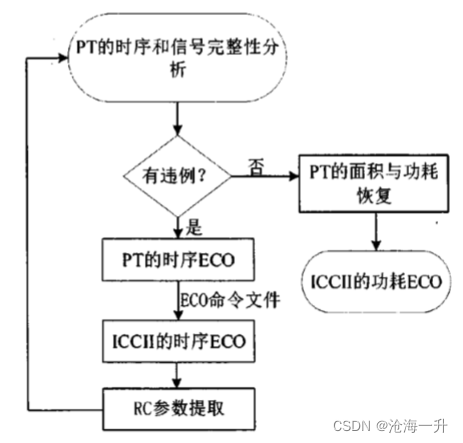

ECO(Engineering Change Order)是指在设计后期,由设计人员根据静态时序分析和后仿真中所暴露出来的问题,对电路和标准单元布局进行小范围调整,保持原设计布局布线结果基本不变的前提下做小规模优化,修复芯片的剩余违例,最终达到芯片的签核标准。在ECO阶段,不能通过后端布局布线的流程来修复违例(重新走一遍流程太费时了。。),而要通过ECO的流程来进行时序、DRC、 DRV以及功耗等优化,ECO流程如下图所示:

上图主要说明的是流片前的ECO过程。

二、ECO分类

1、按时间节点

根据时间节点分类,ECO主要可以分为流片(Tape out)前的ECO,流片过程中的ECO,流片后的ECO。

1)流片前的ECO

对于一个完整的数字IC设计,从设计规格RTL编码 一直到后端的物理验证结束,一般一个项目都会规定哪个阶段在哪个时间点必须停止,比如在某个时间点RTL必须停止,这个时候不会也不允许再更新RTL 代码,即使后面仿真验证有漏洞。因为此时数字后端工程师可能都做好布局布线, 时序己经没什么大问题了,或者都准备开始修时序了。此时如果发布新的RTL, 那就意味着需要重新跑整个流程,从综合到P&R,再到修时序,一方面会严重影响整个项目的流片时间,从而影响芯片上市的时间。因此,此时数字前端负责写代码的工程师只能在最后RTL的基础上,通过写ECO脚本的方式来实现功能上的ECO。

2)流片过程的ECO

对于数字后端实现后的设计,时序己经符合了签核(sign off)标准,DRC违例已经干净,LVS已经过了,电压降、形式验证等都己经通过。但是数字前端设计工程师还没来得及做完大部case的后仿,而且芯片又面临着投放市场的压力。此时,不得不开始传GDSII文件给工艺厂开始流片了。前一周左右工艺厂会先做底层的加工。只要后期仿真发现的问题不需要再添加额外的单元,就不耽误之前的流片。即使发现需要新加几个单元,这个时候仍然可以通过替换后端实现过程中所加的备用单元(spare cell)来实现。

我们往往在做版图设计的时候在在设计中插入1%左右的spare cell,就是以防流片时和流片后需要进行eco。

3)流片后的ECO

当芯片流片回来,在测试过程中发现了漏洞,而且此漏洞又必须修复掉,此时就需要通过ECO来解决。这个时候做ECO的代价相对前面两种大很多,而且最产的芯片会面临巨大压力。改动少的可能就改几层金属层,多的可能就需要动十几层金属.甚至需要重新流片。做ECO之前,数字前端设计工程师会出一个ECO方案,同时让后端工程师进行评估。主要评估需要改动的层数,时序是否能快速收敛等方面的风险。

2、按网表是否改变

ECO依据是否需要改变网表可以分为功能ECO和时序ECO。

1)功能ECO

功能ECO指在ECO的过程中存在逻辑上的问题,需要对网表进行更改。首先前端设计人员会进行RTL代码的修改,修复设计中存在的问题,然后将修改后的代码进行重新综合产生新的网表。修改逻辑之后的综合网表不需要重新做一遍后端设计, 只需要在之前的版图设计的基础上修改逻辑,即通过功能ECO来对布局和布线做局部的更新,从而修复设计中的逻辑问题。做完功能ECO要确保功能的一致性,需要进行验证。通过将修改之后的网表与功能ECO之后的网表进行对比,从而确保最终的版图与RTL保持功能的一致性。

2)时序ECO

是指普通的ECO,不需要对网表进行修改,只是对于违例进行局部的优化。主要的违例种类如下: (1) PV (Physical Verification,物理验证)& LEC (Logic Equivalence Check,逻辑一致性检查)(2) DRV(Design Rule Violation)。

三、ECO处理内容

ECO阶段主要清理芯片的残余违例,通过后端设计修复方式清理芯片内部时序违例、设计规则违例(DRV)和物理规则违例,使芯片符合设计要求和流片要求。ECO 阶段将进行多轮迭代,修复芯片违例并在下轮迭代时更新相应的分析结果加以检验, 最终实现芯片的时序、DRV、物理规则收敛,完整芯片的整体物理状态符合签核要求,能够流片生产。

- 设计规则违例

设计规则违例(Design Rule Violation, DRV)是ECO阶段需要清理的违例内容,时序路径不仅要满足setup和hold的时序要求外,还需要满足设计规则要求。DRV包括最大转换时间(max transition)、最大电容负载(max cap)、噪声(noise)、长连线(long net)等影响芯片稳定的条目。 DRV违例本身可能并不引起时序违例,但是由于工艺及芯片的自身特点, 修复DRV能够提高芯片稳定性,优化时序、功耗,提升芯片的抗干扰能力。

PrimeTime将检测所有违例条目,输出报告文件,根据违例报告手动修复所有DRV违例 。

DRV违例 条目虽然繁多,但是修复方式相对单一大致分为三类:(1)提升标准单元驱动力,(2)插入法,(3) 分割法

1)提升标准单元驱动力

每种标准单元的驱动能力都是有限,当负载超过每种标准单元的驱动范围时,电流强度减小,引起信号转换时间增加,抗干扰能力降低等问题。

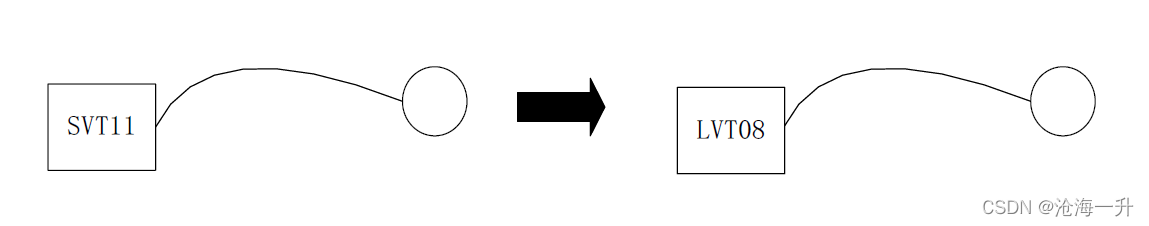

以7nm工艺为例,工艺库中标准单元的阈值类型分别为SVT(Standard VT)、LVT(Low VT)和 ULT(Ultra Low VT),沟道长度类型分为08和11。阈值电压关系为 SVT>LVT>ULT, 相应驱动能力为 SVT<LVT<ULT,沟长08的驱动能力大于沟长11的标准单元 。如果驱动单元的阈值为SVT 或者沟长为 11 时,可以优先考虑更换阈值电压和沟长,增加单元的驱动能力。

如上图所示,使用命令 size_cell 将标准单元更换为目标类型。如果只改的阈值和沟长,标准单元面积不会发生改变,不需要考虑周围物理空间是否充足,修复风险最低。 ULT单元的驱动能力最强, 泄漏电流最大,虽然具有较强的驱动能力,但不利于芯片整体功耗的优化,在时序较为宽松的设计中,不允许使用 ULT单元,仅在时序极难收敛的情况下 允许适量替换,对ULT单元所占数量比例有严格的限制 。

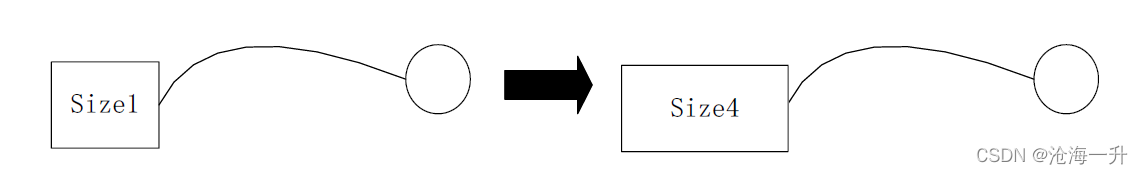

如果单元类型已是LVT08,可以采用增加标准单元尺寸提高单元驱动能 ,使用 命令 size_cell 将单元替换为更大尺寸的库类型 。普通标准单元增加面积尺寸能够显著提高单元驱动能力 ,延迟单元( delay cell)增加单元尺寸将减小驱动力,增加单元延迟,如果违例级驱动为可以加单元延迟,如果违例级驱动为延迟单元,可以尝试替换为缓冲器提升驱动能力 。如下图所示:

使用增加标准单元尺寸时需要检查目标单元周围是否有充足空间用以增加单元面积, 如果空间不够,增加面积后标准单元将会发生重叠, 规则化时将被 EDA工具摆放至邻近的合法位置,可能起额外的违例;此外,增加违例单元面积对于违例级的前级而言负载变大,如果前级驱动能力处于零界范围,增加面积也有可能引起前级出现时序违例,具有一定风险。

2)插入法

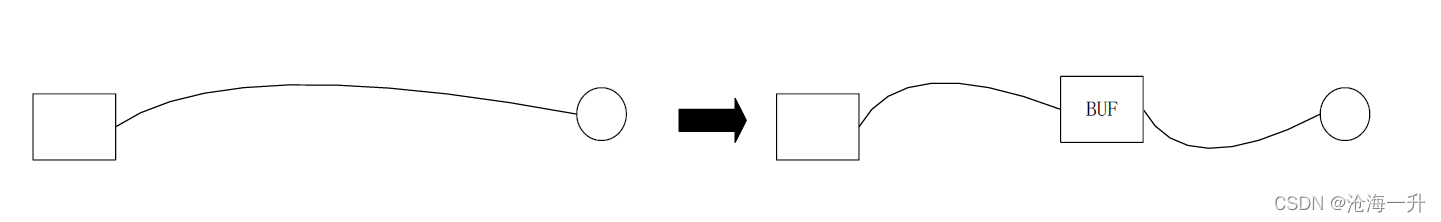

插入法用于修复连线过长引起的DRV 违例。过长的金属连线将会带来巨大的寄生电阻,在7nm 工艺下,库类型HDBLVT08_BUF_4 的缓冲器一拖一时平均能够驱动55μm 的标准单元,如果连线长度和单元驱动力不匹配将会引起DRV 违例。

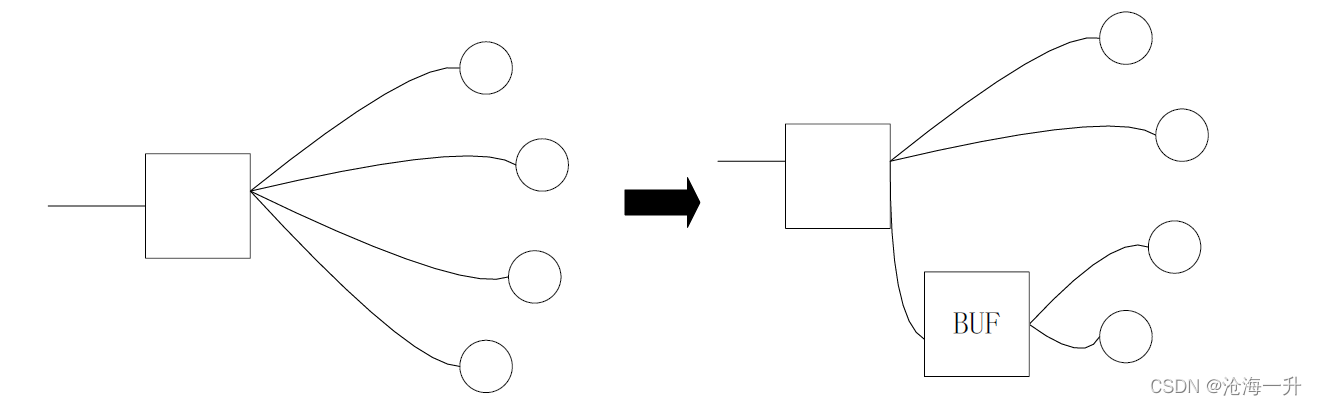

如果无法通过提升单元驱动力修复违例,可以尝试使用命令add_buffer_on_route 在连线适当位置插入缓冲器,插入的缓冲器将长连线分割为两段,能够减小连线长度,并在中途插入缓冲器恢复电位,提高电流的驱动能力,如下图所示:

插入法能够有效解决连线过长引起的DRV 违例,插入后将在时序路径上增加额外的缓冲单元延时,但是,连线的整体延时得到改善,最终修复效果取决于减少的连线延时和插入单元的单元延时数值关系。如果违例单元在时钟路径上,插入缓冲器将会改变时钟树结构,具有较高风险,需要确认下级时序路径是否有足够余量,并做好备份工作。

3)分割法

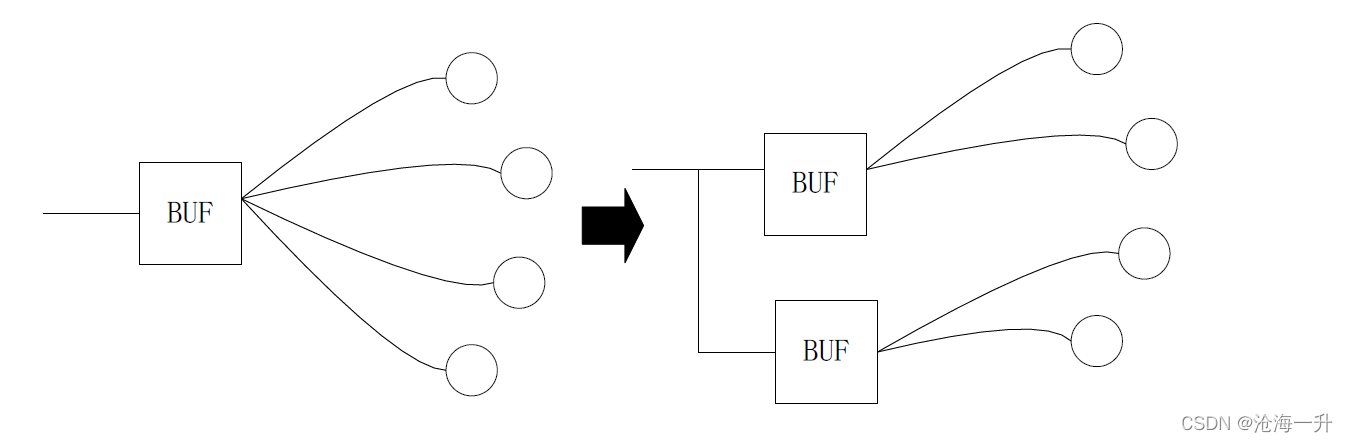

分割法多用于负载数目过多引起的DRV 违例,当负载数量超过标准单元的驱动能力时,过大的寄生电阻引起信号转换时间过长。使用命令create_cell 创建一个缓冲器并指定适当的物理位置, 将一定数量的负载引脚通过命令 connect_pins 连接至缓冲器的输出端,缓冲器输入端连接至原驱动单元的输出端。

分割法能够分割一定数量的负载至插入缓冲器级,减小违例级的扇出数量,同时,新插入的缓冲器能够恢复电位,增强电流驱动能力,达到修复违例的效果。

分割法插入缓冲器的支路将引入额外的缓冲单元延时,如果时序路径余量较少或是违例发生在时钟树上,可能引起额外违例,风险较大。采用下图所示的分割方式:

创建一个和驱动单元类型相同的单元,将分割的负载并联接入时序路径,新插入的单元级数和原路径相同,不会引入额外的单元延时;负载均分至新的驱动单元,如果负载数量过多,可以并入多个单元均分违例负载,直至违例修复。

- 时序违例

ECO阶段的时序违例和布局布线阶段大致相同,需要额外考虑信号完整性(Signal Integrity,SI)对时序状态的影响。随着工艺越来越先进,工艺特征尺寸减小,布线密度加大,使得金属连线宽度、连线间距进一步减小,极大地增加布线的复杂程度,较高的工作频率使得器件在充放电过程产生较多的噪声源,随着工作电压降低,电路的噪声容限也随之变小,串扰效应的影响越来越大。

信号完整性对所有场景都有影响,主要表现在延迟、串扰、时序等几个方面,随着器件工作频率的升高,信号完整性的影响尤为突出,容易导致芯片的稳定性问题,甚至不能正常工作,需要将SI和非SI的时序违例全部修复。

1)修复setup违例

(1)调整单元位置。负载和驱动不合理容易造成连线过长,导致负载和连线延时变大,可以通过适量调整负载或驱动的位置减小连线长度达到优化时序的效果。 在深纳米工艺下,由于单元密度( cell density)较高,手动调整单元位置不但影响工作效率,改动后可能产生与单元相连路径的额外违例,通常不推荐使用,仅当违例值仅当违例值很小时可以适当使用 。

(2)增加单元驱动力 。以7nm工艺为例,其所采用的多阈值电压方案将单元阈值分为SVT、 LVT和 ULT,不同阈值对应的驱动能力等尺寸下ULT驱动能力最强。当驱动单元驱能力不足时可以通过更改序路径上标准的类型增加电流, 也可增大单元尺寸改善时序。

(3)插入缓冲器。对于连线过长的违例路径,连线越长,寄生效应越发明显。在互联线合适位置插入缓冲单元,提高电流驱动能力够缓解长互连线带来的 巨大负载和串扰问题 。过长连线容易引起 DRV违例,可以优先 修复芯片内部 DRV违例 ,待违例数量较小时集中修复芯片内部时序。

(4)时钟有用偏斜 (useful skew)。当违例数据路径无法再进行优化 ,可以过调整时钟树结构改善偏斜修复违例 ,增加违例路径捕捉级 Tcapture的延时 ,延长要求时间 ,这种 方式将使后级时序整体后移, 如果后级路径没有足够的余量, 将在后 级引发新的 setup违例,因此使用前需要查询后级 路径 余量 ,通过占用后级余量的方式修复 setup违例。

2)修复hold违例

通常采用插缓冲器的方式延长数据路径,增加信号路径,增加信号的到达时间。 只要芯片内部物理空间足够,hold违例都能够修复。如果空间不足, 可以尝试减小时序路径标准单元的驱动能力、手动延长单元的摆放位置增加信号时等方式进行修复。

如果违例路径只在 SI报告中产生,在非SI报告中没有违例,除上述修复方式外可以尝试在时序报告中寻找违例路径互连串扰较大的线,对这些添加屏蔽阻挡SI效应,减少对信号的干扰,可以修复由 SI 效应引起的时序违例 。

3、物理规则违例

物理版图的检查主要由工具(如Calibre)辅助完成, 包括 LVS、ERC、DRC、MiniEDRC、 DFM等物理检查, EDA工具根据设计规则对版图形进行检查,报告存在违例的部分。 DRC违例关乎物理版图能否成功制造,所有DRC违例都需要按照设计规则要求进行修复。

深纳米工艺下,标准单元数目较多,摆放位置不均匀,对电源网络的消耗程度也有较大差异。 逻辑功能复杂的标准单元集中于局部区域,对电源网络消耗较大,造成电压分布不均匀。如果局部电压低于阈值时, 则称为电压降 (IR-drop)违例。电压降违例会降低器件性能,影响芯片的稳定。通常在电源规划时 将以最坏情况的参数库文件为参考调整电源网络,牺牲一些布线资源,对电源板网络进行额外优化,使网络尽可能满足电压降约束要求 。

ECO阶段时,通过 IR、EM分析检测芯片内部存在电压降违例的位置,对路径在电压降违例的位置,对路径进行相应调整。若违例原因为局部区域单元数量过多,可以尝试降低驱动能力减小负载所分电压, 或者将过于集中的标准单元分散摆放, 达到减小局部电压消耗的效果。

电迁移违例( electro migration violation)为电迁移现象超过连线额定值,达到影响电路稳定性的程度。其成因大致可分为三类:连线负载过大、单元驱动能力强和互连线过窄。长的金属和多扇出数量都会造成负载大而需要大电流进行驱动, 引起电迁移违例 。若违例发生在数据路径上,可以通过插入缓冲器和分隔负载的方式减小连线电流; 若违例发生在时钟路径上,修复时要尽量避免改动时钟延时而引起序违例,通常采用复制驱动分割的方式减少负载,降低连线电流; 采用减小单元驱动能力, 降低驱动电流的修复方式,具有潜在引起 DRV或者时序违例的风险 。

四、金属ECO

芯片经过多轮 ECO修复后,整体物理状态已趋于平稳,违例数目较少。如果剩余违例可以在不改动 base层的前提下进行修复,ECO将进入base层冻结(base freeze)阶段。 base层指物理版图金属层M0以下的部分,包括阱、有源区、场区等 ,base层冻结后的ECO称作金属ECO(metal ECO),金属ECO不能改动base层的内容,只能对芯片的金属连线进行修改。

金属ECO能够使用的修复方式更加局限, base阶段使用的更换标准单元类型、 插入缓冲器等改动操作均不再允许使用。芯片内部预留一定数量DCAP_ECO单元,DCAP_ECO单元的版图结构对称,默认状态下用作 decap 单元(去耦电容), 减小芯片内部的浪涌现象。

通过改变DCAP_ECO单元的物理连接方式,可以将其用作缓冲器。 相比同等尺寸下缓冲器的单元,DCAP_ECO单元的驱动能力更低,所占面积大,不适合修复较大的时序违例。

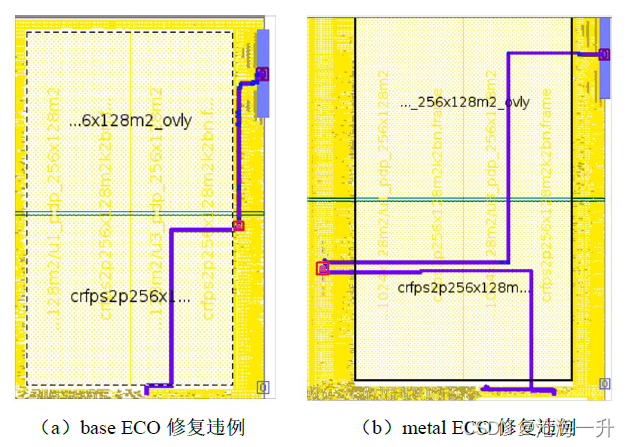

此外,DCAP_ECO单元物理位置为 base ECO阶段预先设置,不易选到近邻的物理位修复违例。 如下图所示:

图(a)为base ECO修复违例的物理图形,金属连线整体长度较小; 图 (b)为 metal ECO修复违例的物理图形,由于近邻位置没有 DCAP_ECO单元, 所选插入位置使整体金属连线较为曲折,修复效果不如 base ECO。

因此,违例需要尽量在 base ECO阶段修复, metal ECO阶段可用资源极少,修复方式十分有限,过大的违例都无法在 在 metal ECO阶段进行修复。

此时,base层冻结的芯片则进入物理检查和验证环节,着手各项指标是否符合设计要求。如果项目时间紧迫,可以选择将检查好的 base层物理版图先行送至工艺厂商进行流片,制作 base层的掩模板,待芯片设计全部完成后,再制作后续金属层的图案 ,能够大幅缩减工程周期,提高生产效率 。

由于base层冻结后芯片不再改动 base层物理版图,必须保证芯片会出现致命问题导流片失败。在芯片设计中, hold违例与时钟周期无关, 如果最终无法修复 ,整个芯片的逻辑功能将面临巨大风险,无法通过其他方式补救 ;DRC影响芯片的生产质量,保证芯片的元器件能够正常制造 ,如果金属 ECO阶段无法修复,将会导致芯片制造失败;如果金属 ECO阶段存在无法修复的setup违例,可以选择 违降低芯片整体的时钟频率 补救,虽然牺牲了芯片性能,但够减小风险、保证正常工作。因此在芯片的后端设计中, hold 违例和 DRC违例需要进行重点检查。

————————————————

版权声明:本文为CSDN博主「沧海一升」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_21842097/article/details/121717450

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?