课程设计五:单总线CPU设计(一)

一、课程设计目的

(一)第1关:MIPS指令译码器设计

- 帮助学生理解指令译码的基本概念,能将32位MIPS指令字译码成不同的指令译码信号。

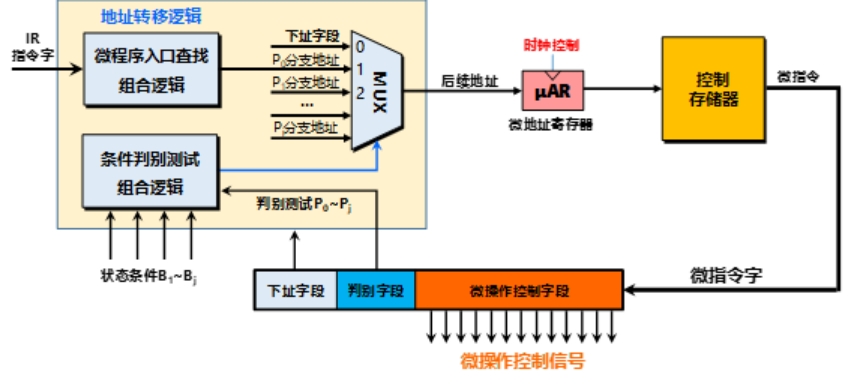

(二)第2、3关:单总线CPU微程序入口查找/条件判别测试逻辑

- 了解微程序控制器中微程序分支的基本原理,要求能设计微程序入口查找逻辑以及判别测试逻辑。

(三)第4关:单总线CPU微程序控制器设计

- 帮助学生理解微程序控制器基本原理,要求学生能够设计微程序控制器。

(四)第5关:采用微程序的单总线CPU设计

- 帮助学生理解单总线结构CPU基本原理,能设计基于微程序控制器的单总线CPU,使得MIPS程序能在单总线结构上运行,最终能运行简单的排序程序sort-5.hex。

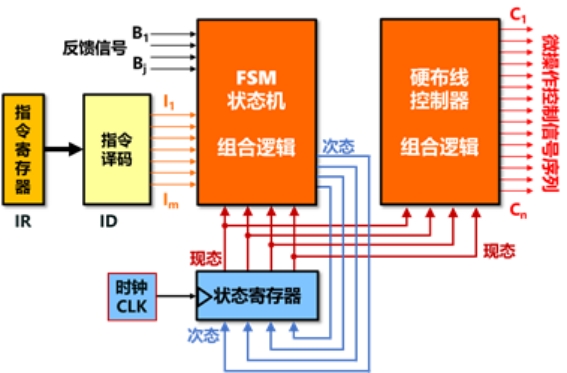

(五)第6关:现代时序硬布线控制器状态机设计

- 帮助学生理解现代时序系统中硬布线控制器设计的基本原理,学生能设计硬布线控制器核心部件状态机模块。

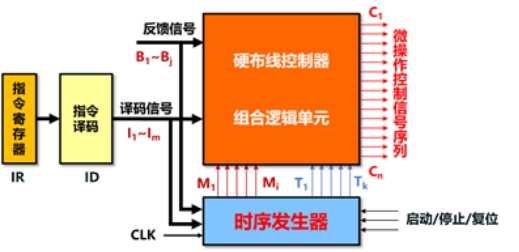

(六)第7关:现代时序硬布线控制器设计

- 帮助学生理解现代时序系统中硬布线控制器的设计原理。

二、课程设计内容

(一)第1关:MIPS指令译码器设计

- 利用比较器等功能模块将32位MIPS 指令字译码生成LW、SW、BEQ、SLT、ADDI、OtherInstr信号:

- 指令译码器是控制器核心功能部件,负责将指令字翻译成一根根的指令译码信号,每一根指令译码信号代表一条具体的指令,如上图中的I

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5779

5779

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?