关于 MIPS 体系:

MIPS 体系结构 是20世纪80年代初发明的一款 RISC(精简指令系统计算机)体系架构。MIPS是一个双关语,它既是 Microcomputer without Interlocked Pipeline Stages 的缩写, 同时又是 Millions of Instructions Per Second 的缩写。相比 Intel x86 的 CISC (复杂指令系统计算机)架构, MIPS 是一种非常优雅,简洁,高效的 RISC 体系架构,非常适合于教学研究,我国的龙芯处理器就是基于MIPS指令系统的。最初MIPS是为32位系统设计的,后来又发展出了64位MIPS,但依然对32位模式向下兼容。

关于指令译码器:

指令译码器(Instruction Decoder,ID) 是控制器中的主要部件之一。计算机能且只能执行“指令”。指令由操作码和地址码组成。操作码表示要执行的操作性质,即执行什么操作,或做什么;地址码是操作码执行时的操作对象的地址。计算机执行一条指定的指令时,必须首先分析这条指令的操作码是什么,以决定操作的性质和方法,然后才能控制计算机其他各部件协同完成指令表达的功能。这个分析工作由指令译码器来完成。

实验目的:

理解指令译码的基本概念,能将32位MIPS指令字译码成不同的指令译码信号。

实验内容:

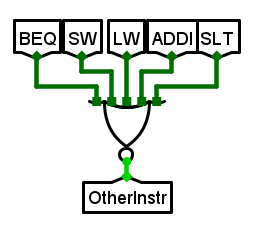

利用比较器等功能模块将32位MIPS 指令字译码生成 LW、SW、BEQ、SLT、ADDI、OtherInstr信号:

| 信号 | 位宽 | 功能描述 |

|---|---|---|

| IR | 32 | MIPS指令字IR |

| LW | 1 | 当前指令为lw指令时输出为1 |

| SW | 1 | 当前指令为sw指令时输出为1 |

| BEQ | 1 | 当前指令为beq指令时输出为1 |

| ADD | 1 | 当前指令为addi指令时输出为1 |

| SLT | 1 | 当前指令为slt指令时输出为1 |

| OtherInstr | 1 | 当前指令为其他指令时输出为1 |

理解指令译码的基本概念,能将32位MIP指令字译码成不同的指令译码信号。

指令译码器是控制器核心功能部件,负责将指令字翻译成一根根的指令译码信号,每一根指令译码信号代表一条具体的指令,如上图中的 I1…Im 。

实验步骤

相关指令的规格通过参考MIPS英文指令手册进行查询。

查询MIPS英文指令手册可以得知,各指令的高六位分别为:

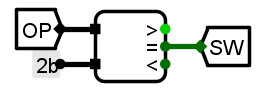

Sw:101011; 换算成16进制为:2B;

Lw:100011; 换算成16进制为:23;

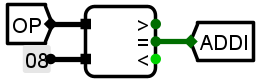

Addi:001000; 换算成16进制为:08;

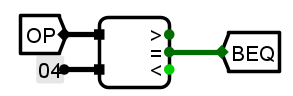

Beq:000100; 换算成16进制为:04;

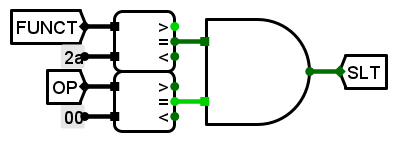

SLT 指令需要和低六位 FUNCT 一起判断:

OP:000000; 换算成16进制为:00;

FUNCT:101010;换算成16进制为:2A;

最后用逻辑或非门总结到 OtherInstr:

电路完成图:

测试为:

预期输入:

Cnt IR LW SW BEQ ADDI SLT OtherI

0000 2010ffff 0 0 0 1 0 0

0001 20110000 0 0 0 1 0 0

0002 ae300200 0 1 0 0 0 0

0003 22100001 0 0 0 1 0 0

0004 22310004 0 0 0 1 0

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2831

2831

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?