RISC-V异常处理流程概述(1):异常处理基本介绍

-

- 一、中断和异常简介

- 二、M模式的CSRs

-

- 1.1 mcause (Machine Cause Register)

- 1.2 mtvec(Machine Trap-Vector Base-Address Register)

- 1.3 mepc (Machine Exception Program Counter)

- 1.4 mie (Machine Interrupt Enable)

- 1.5 mip (Machine Interrupt-Pending)

- 1.6 mstatus (Machine Status Registers)

- 1.7 mtval (Machine Trap Value Register)

- 1.8 mscratch ( Machine Scratch Register)

- 1.9 mret (Trap-Return Instructions)

- 1.10 medeleg (Machine Exception Delegation)和 mideleg (Machine Interrupt Delegation)

- 三、S模式的CSRs

-

- 3.1 sstatus (Supervisor Status Register)

- 3.2 stvec (Supervisor Trap Vector Base Address Register)

- 3.3 sepc (Supervisor Exception Program Counter)

- 3.4 scause (Supervisor Cause Register)

- 3.5 stval (Supervisor Trap Value)

- 3.6 sie (Supervisor Interrupt Eable)和 sip (Supervisor Interrupt Pending)

- 3.7 sscratch (Supervisor Exception Program Counter)

- 四、参考资料

一、中断和异常简介

1.1 RISC-V的异常、中断和陷入

在不同架构中,对于中断、异常、陷入的定义可能会有所不同。在RISC-V中:

- 异常(Exception):异常是指在指令执行期间发生的一种错误或非正常情况,异常通常是由程序内部的错误或不恰当的操作引起的,比如除零错误、内存访问越界。

- 中断(Interrupt):中断是指收到外部设备或源的信号,要求处理器终止当前正在执行的任务,处理完中断后继续原来的工作,是异步事件。

- 陷入(Trap):指的是中断或异常导致的控制流转移,这时控制流会转移至trap handler。

异常(Exception)和中断(Interrupt)都属于陷入(Trap),异常是同步操作,中断是异步操作。

注:在本质上讲,中断和异常并没有区别,都是处理器的一个处理过程。当中断和异常发生时,处理器都会暂停当前的执行程序,转而执行中断或异常处理程序,处理完后视情况恢复执行之前被暂停的程序。

1.2 RISC-V中trap的分类

在RISC-V的spec中,将RISC-V的trap分为下面几类:

- Contained Trap:这类 trap 对程序执行环境内的软件可见,并且由这些软件进行处理。例如:

- 在 U 模式下执行 ECALL 指令主动触发 trap,会使当前 hart 切换到 S 模式下的 trap 处理程序。

- 运行在 U 模式下的 hart 发生中断时,该 hart 会切换到 S 模式的 trap 处理程序进行处理。

- Request Trap:这类 trap 是由对执行环境的显示调用引起的同步异常,例如系统调用。

- Invisible Trap:这类 trap 由执行环境进行处理。运行在执行环境内的软件察觉不到这类 trap 的发生和处理。比如 page fault 的处理。

- Fatal Trap:这类 trap 表示发生了导致执行环境终止的致命错误。

除了Fatal Trap外,其他类型的trap都需要由执行环境进行处理,当发生Fatal Trap时,直接会导致崩溃等一系列问题。

1.3 RISC-V中的权限模式

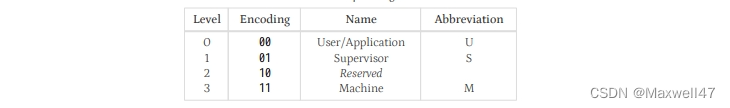

在任何时候,RISC-V 硬件线程 (hart) 都以某个权限级别运行,该权限级别编码为一个或多个 CSR(控制和状态寄存器)中的模式。目前定义了三个 RISC-V 权限级别,如下表所示:

权限模式用于在软件堆栈的不同组件之间提供保护,尝试执行当前权限模型不允许的操作讲导致引发异常。

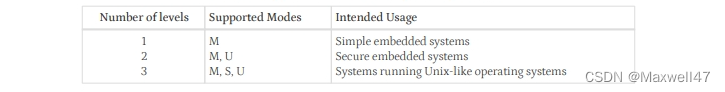

计算机级别具有最高权限,M模式是 RISC-V 硬件平台的唯一强制性权限级别,不同的模式组合如下表。在机器模式(M 模式)下运行的代码通常本质上是可信的,因为它对机器实现具有低级访问权限。M模式可用于管理RISC-V上的安全执行环境。用户模式(U 模式)和管理引擎模式(S 模式)分别用于常规应用程序和操作系统。

二、M模式的CSRs

RISC-V中M模式的异常处理主要依靠CSRs,主要关注以下的状态控制寄存器:

1.1 mcause (Machine Cause Register)

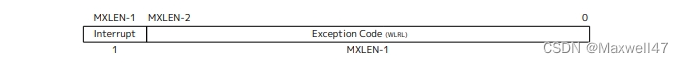

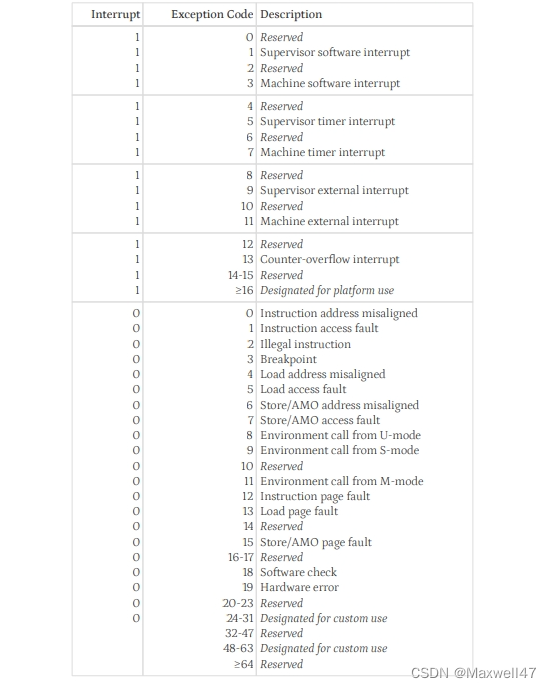

机器模式异常原因寄存器,记录发生异常的原因,首位 Interrupt 置 1 时是中断,0 时为异常。Exception Code 域记录异常发生的原因编码。下面列出可能导致异常的编码:

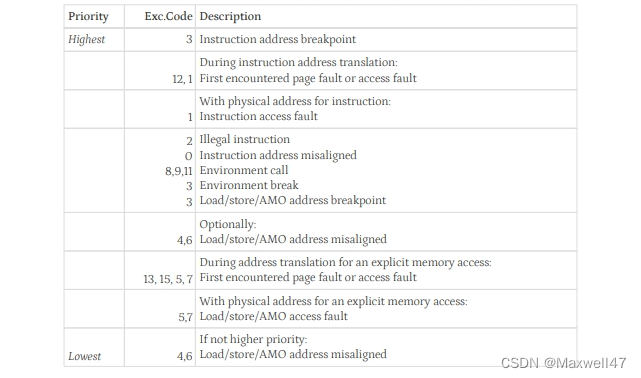

异常优先级如下图所示,优先级递减排序:

1.2 mtvec(Machine Trap-Vector Base-Address Register)

机器模式异常入口基地址寄存器,保存发生异常时处理器需要跳转到的地址,实际上就是异常处理程序的入口地址。该寄存器包含基地址 BASE 以及模式 MODE 两个域,其中 MODE 域表示异常处理程序入口地址的寻址方式。基地址BAES中的值必须四字节对齐,当计算异常处理程序的入口地址时,需要将MODE中的两位恒置为0。

本文详细介绍了RISC-V处理器的异常处理机制,包括异常处理准备工作,如设置CSR_MTVEC寄存器和异常栈的构建。在Linux环境中,OpenSBI的trap_handler函数扮演关键角色,处理不同类型的mcause异常,特别是系统调用。通过sbi_ecall_handler,OpenSBI查找并执行已注册的回调函数来响应系统调用。同时,文章还阐述了OpenSBI中系统调用的注册过程,涉及sbi_ecall_init和sbi_ecall_register_extension函数。

本文详细介绍了RISC-V处理器的异常处理机制,包括异常处理准备工作,如设置CSR_MTVEC寄存器和异常栈的构建。在Linux环境中,OpenSBI的trap_handler函数扮演关键角色,处理不同类型的mcause异常,特别是系统调用。通过sbi_ecall_handler,OpenSBI查找并执行已注册的回调函数来响应系统调用。同时,文章还阐述了OpenSBI中系统调用的注册过程,涉及sbi_ecall_init和sbi_ecall_register_extension函数。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

613

613

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?