| 龙芯是中科院下属的计算机所研发的自主产权国产处理器,现在已经由中科龙芯公司商业化,再过几天他们又要发布新一代龙芯处理器——龙芯3A4000系列了,这是在现有的龙芯3A3000系列上的改进版。

根据之前的消息,龙芯3A4000处理器依然是28nm工艺,频率从龙芯3A3000的1.5GHz提升到了2.0GHz,架构升级为GS464V,搭配的芯片组也升级到了龙芯7A2000,28nm工艺。

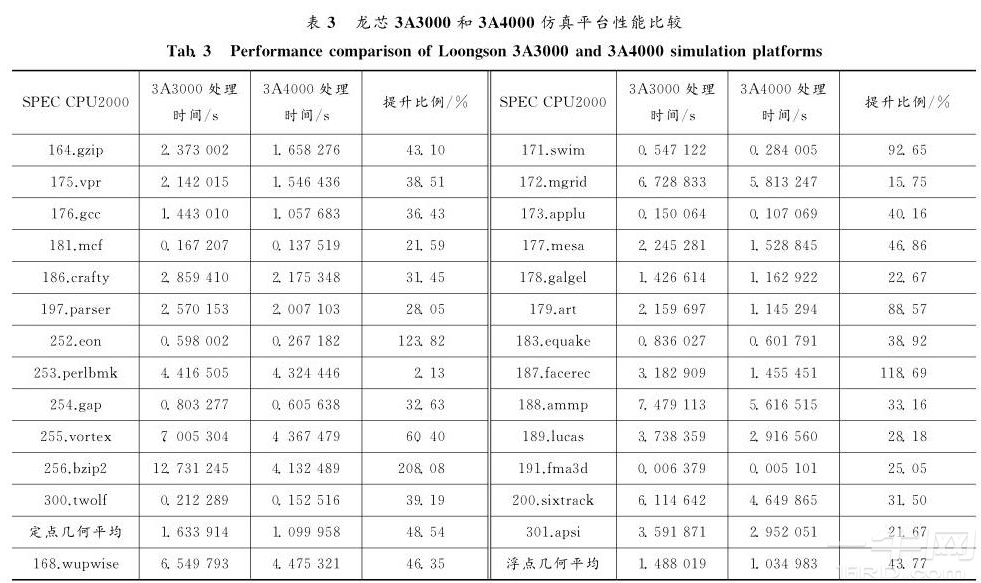

那么龙芯3A4000处理器小幅改进之后的性能提升有多大呢?事实上龙芯官方很早也公布该龙芯3A4000的性能水平了,龙芯首席架构师胡伟武博士在今年初的期刊下介绍过龙芯3A4000处理器的性能测试,测试是在FPGA仿真平台上进行的,模拟3A4000和3A3000的主频均为1GHz,内存控制器频率均为500 MHz,结果如下:

从结果来看,在相同主频下,龙芯3A4000比3A3000的定点性能高48.54%,浮点性能高43.77%,而且部分测试中性能提升幅度超过了100%。

需要注意的是,上述测试还没有考虑到龙芯3A4000处理器支持的246位向量优化,根据X86平台上的性能测试,编译器自动向量化优化可将 SPECCPU 的定点性能提高约5%,浮点性能提高约15%。

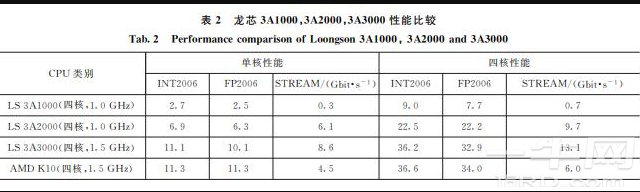

那龙芯3A3000的性能水平优势如何呢?胡伟武博士还对比过1.5GHz下的AMD K10处理器的性能,同频率下单核、四核性能跟K10基本是一个水平的。换句话说,龙芯3A4000处理器的IPC性能已经超过了AMD的K10处理器的50%左右,不过AMD K10处理器的实际频率很高,这方面国产处理器依然有较大的差距,工艺性能是最大的瓶颈。

此外,上述测试还是在同频1.5GHz下对比的,实际上龙芯3A4000使用3A3000的28nm工艺,通过优化设计将主频从1.5GHz提升到2.0GHz。在相同的工艺条件下,龙芯3A4000性能为3A3000的2倍。 胡伟武博士表示,在此基础上,若使用更先进的工艺技术将主频提高到2.5~3.0GHz,则龙芯CPU的通用处理性能可达到国际主流CPU的水平。

|

龙芯3A4000处理器实测:28nm工艺不变,性能可提升100%以上

最新推荐文章于 2023-02-03 10:34:09 发布

6861

6861

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?