1.为什么需要时钟?

时钟是为时序电路提供时钟信号的。我们各个嵌入式系统都离不开一个时钟。为什么需要时钟呢?我们从一个例子来说明。

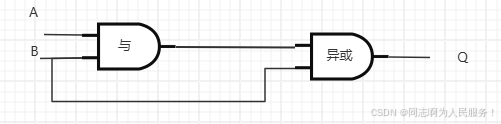

如图所示的电路,输入信号A和B通过逻辑门来决定着 异或门输出信号Q。

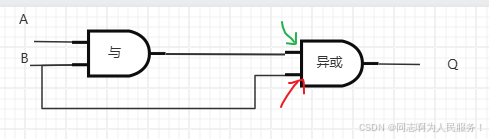

1.当A=1,B=1时,Q=0

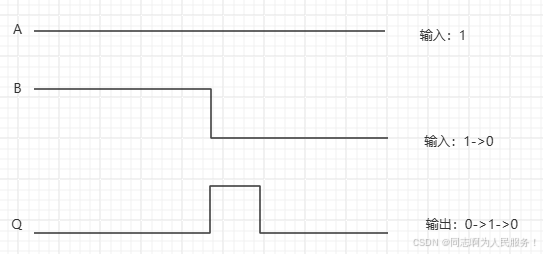

2.在1的前提下,当B从1变为0时,由于B作为异或门的直接输入,异或门的这个输入(图中红色箭头所示)会立马感受到0,而异或门的另一个输入(图中绿色箭头所示)因为要经过逻辑门与门的运算,需要过一小段时间,才会由1变化为0,就导致异或门的输出Q产生如下变化:

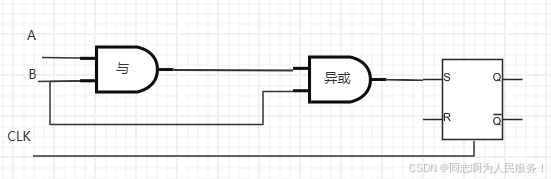

如何消除这种变化呢?可以在异或门的输出端放置一个边沿触发器,如图所示,只有当CLK端的输入从0变化为1时,数据端S的的输入才会影响 边缘触发器的输出Q。这样就可以把传播时延导致的变化消除。而CLK这个输入就是我们所说的时钟信号。

2.STM32有哪些时钟?

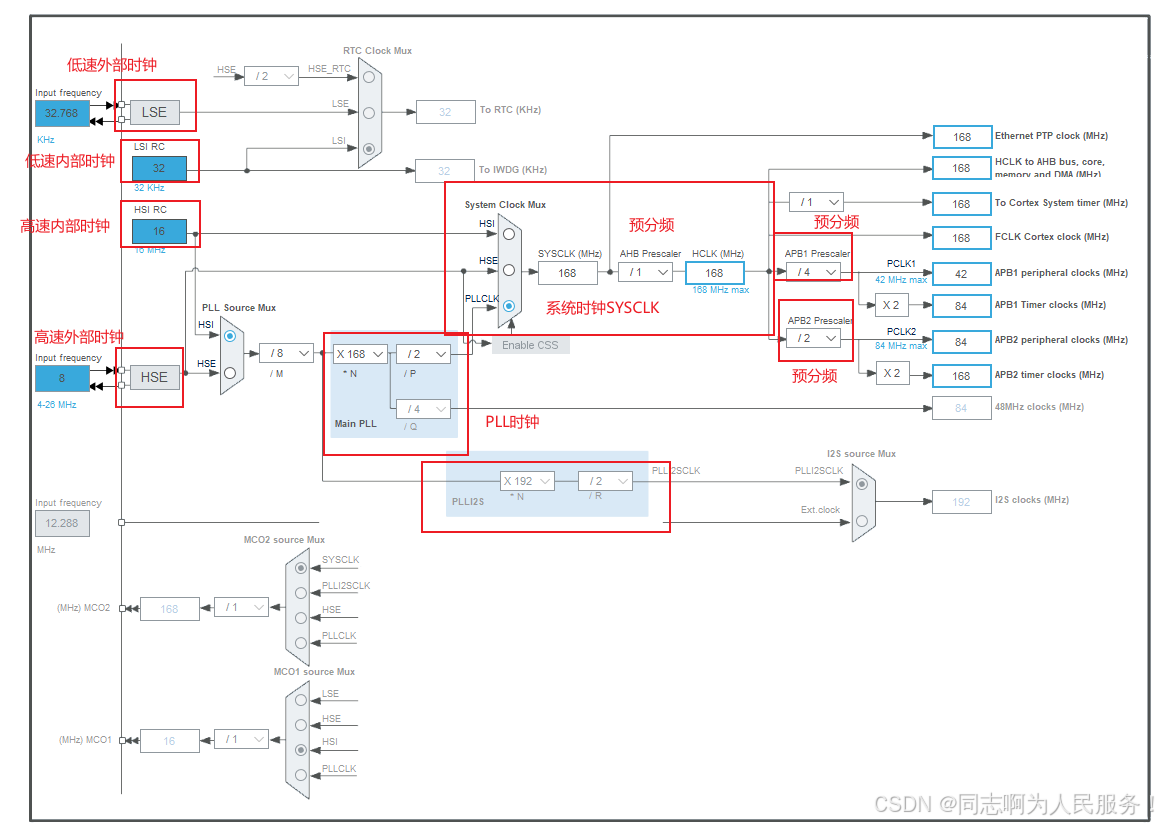

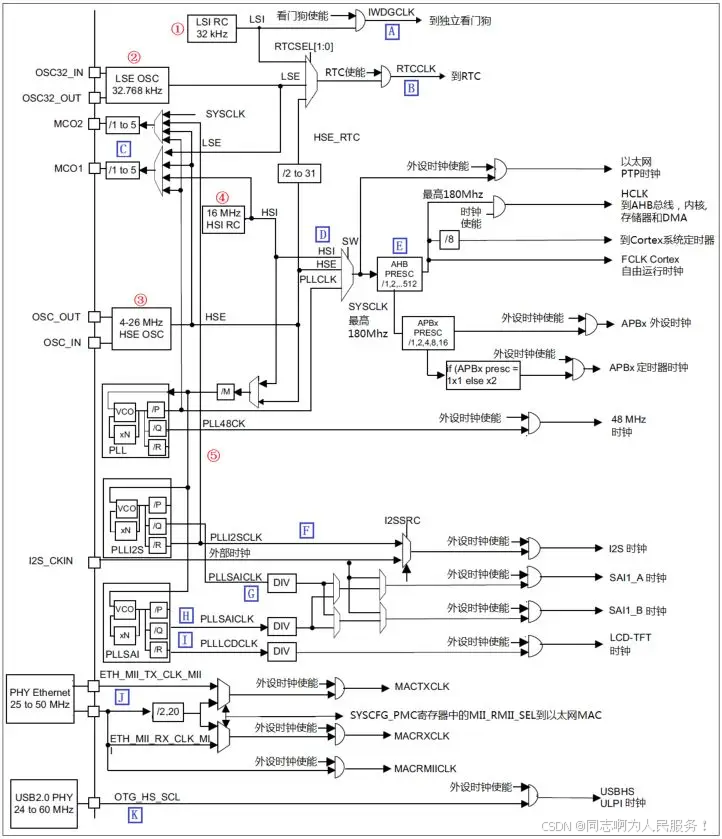

下面我们以STM32 40X为例,讲一下STM32 40X的时钟系统。

嵌入式常见的时钟源:高速外部时钟(HSE)、低速外部时钟(LSE)、高速内部时钟(HSI)和低速内部时钟(LSI):

HSE:High speed external 高速外部时钟

HSI: High speed internal 高速内部时钟

LSE: Low Speed external 低速外部时钟

LSI: Low Speed Internal 低速内部时钟

下面这两个时钟树图看哪一个都可以。

其中,LSE为低速外部时钟,HSE为高速外部时钟,它们的时钟源可以是晶振。再往PLL时钟看去,可以看到PLL时钟的时钟源是高速内部时钟HSI和高速外部时钟HSE。往系统时钟看去,PLL时钟,高速内部时钟HSI,高速外部时钟HSE都可以作为系统时钟SYSCLK的时钟源。而系统时钟SYSCLK又经过AHB预分频变为HCLK,HCLK再分别经过APB1和APB2预分频分别变为PCLK1和PCLK2. 需要注意它们的分频因子。

其中:

AHB:Advanced High-performance Bus 即高性能总线,使用的时钟 HCLK 是系统时钟SYSCLK经过AHB预分频器 分频之后得到。

APB: 高级外设总线(Advanced Peripheral Bus),分为APB1和APB2。

APB1: low speed APB 低速外围总线, 使用的时钟HCLK1 是 HCLK经过 低速APB1预分频器 分频之后得到。

APB2: high speed APB 高速外围总线, 使用的时钟HCLK2 是 HCLK经过 高速APB2预分频器 分频之后得到。

ASB :Advanced System Bus 系统总线 ASB是AHB的一种替代方案。

PPB: Private Peripheral Bus 专用外设总线

为什么要搞分频呢?

1.要知道,时钟频率越高,时钟周期越小,即单位时间内执行的指令越多(关于时钟周期,机器周期,指令周期,请参见一文搞懂指令周期,机器周期和时钟周期)。

2.一个功能庞大的系统,需要的时钟模块就越多。不同的时钟模块提供不同的时钟频率。一个高时钟可以通过分频提供更小的不同的时钟选择。

3.时钟频率越高,相应功耗越大。有些功能,完全不需要那么高的时钟频率,比如看门狗时钟(关于时钟频率和时钟精度请参见)。时钟树在设计时,不同的模块提供不同的时钟选择,STM32有很多外设,可以用时钟来作为这些外设的功能开关,服务于低功耗设计。

603

603

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?