2.8 多输出逻辑函数的化简

在化简多输出逻辑函数的过程中,我们发现,如果不是孤立地分别对每一个输出函数进行化简,而是从整体上综合考虑进行化简,有时会获得更加简单的化简结果,使所用门电路的数目和所有门电路总的输入端数目均为最少。例如有下面的一组多输出逻辑函数需要化简:

𝑌1(𝐴,𝐵,𝐶,𝐷)=∑(1,4,5,6,7,10,11,12,13,14,15)Y1(A,B,C,D)=∑(1,4,5,6,7,10,11,12,13,14,15) 𝑌2(𝐴,𝐵,𝐶,𝐷)=∑(1,3,4,5,6,7,12,14)Y2(A,B,C,D)=∑(1,3,4,5,6,7,12,14) 𝑌3(𝐴,𝐵,𝐶,𝐷)=∑(3,7,10,11)Y3(A,B,C,D)=∑(3,7,10,11)

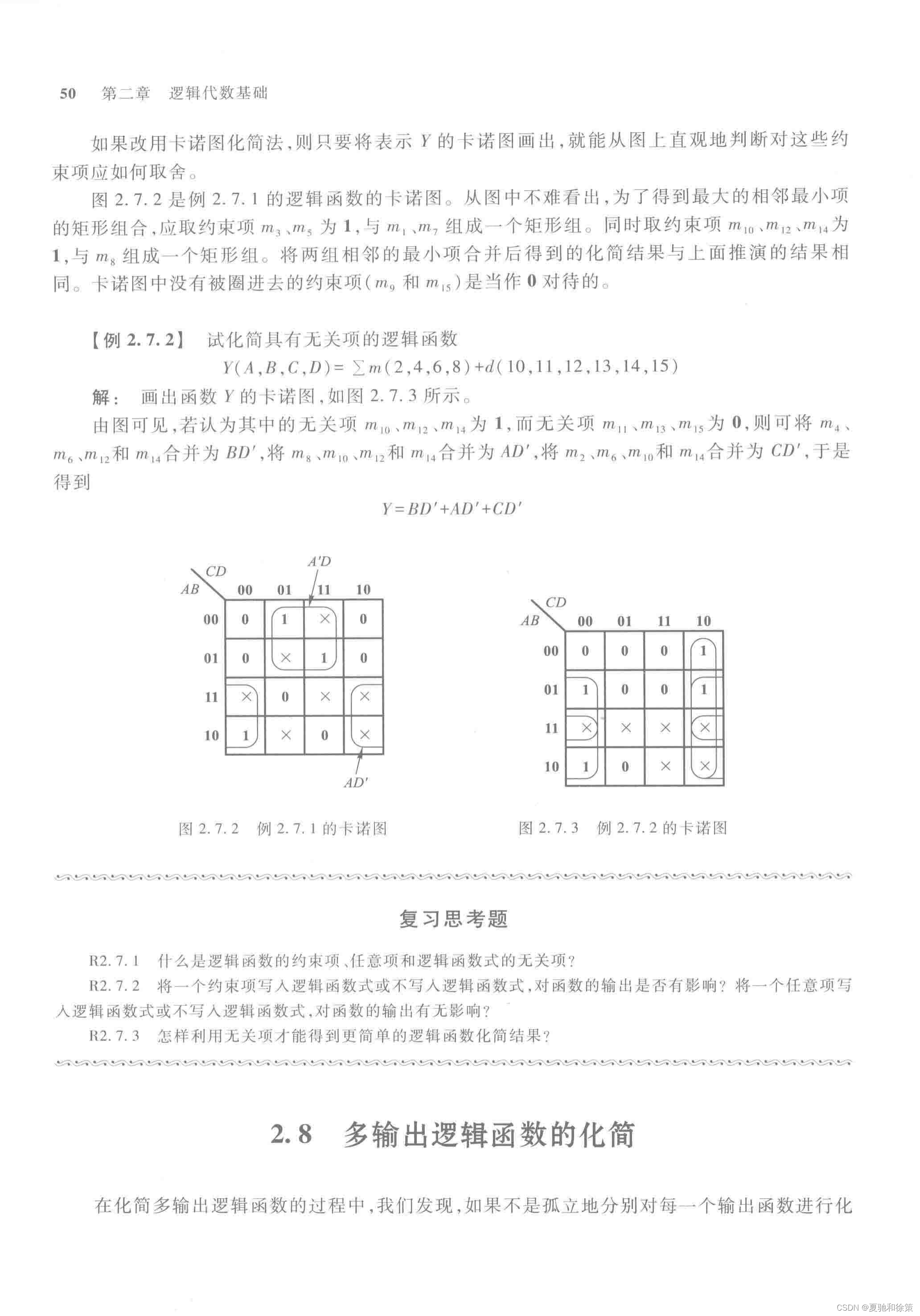

如果用卡诺图分别化简每一个函数,并按图 2.8.1 所示合并最小项,就可得到如下的化简结果:

𝑌1(𝐴,𝐵,𝐶,𝐷)=𝐵+𝐴𝐶+𝐴′𝐶𝐷Y1(A,B,C,D)=B+AC+A′CD 𝑌2(𝐴,𝐵,𝐶,𝐷)=𝐴′𝐷+𝐵𝐷′Y2(A,B,C,D)=A′D+BD′ 𝑌3(𝐴,𝐵,𝐶,𝐷)=𝐴′𝐶𝐷+𝐴𝐵′𝐶Y3(A,B,C,D)=A′CD+AB′C

根据式 (2.8.2) 画出的逻辑图如图 2.8.2 所示。

图 2.8.1 用于化简式 (2.8.1) 逻辑函数的卡诺图

CD

AB

00

00

0

01

1

11

0

10

0

CD

AB

00

00

0

01

1

11

1

10

0

CD

AB

00

00

0

01

1

11

0

10

0

Y1 = B + AC + A'CD

Y2 = A'D + BD'

图 2.8.2 根据式 (2.8.2) 得到的逻辑电路图

A'

B

B'

C

C'

D

D'

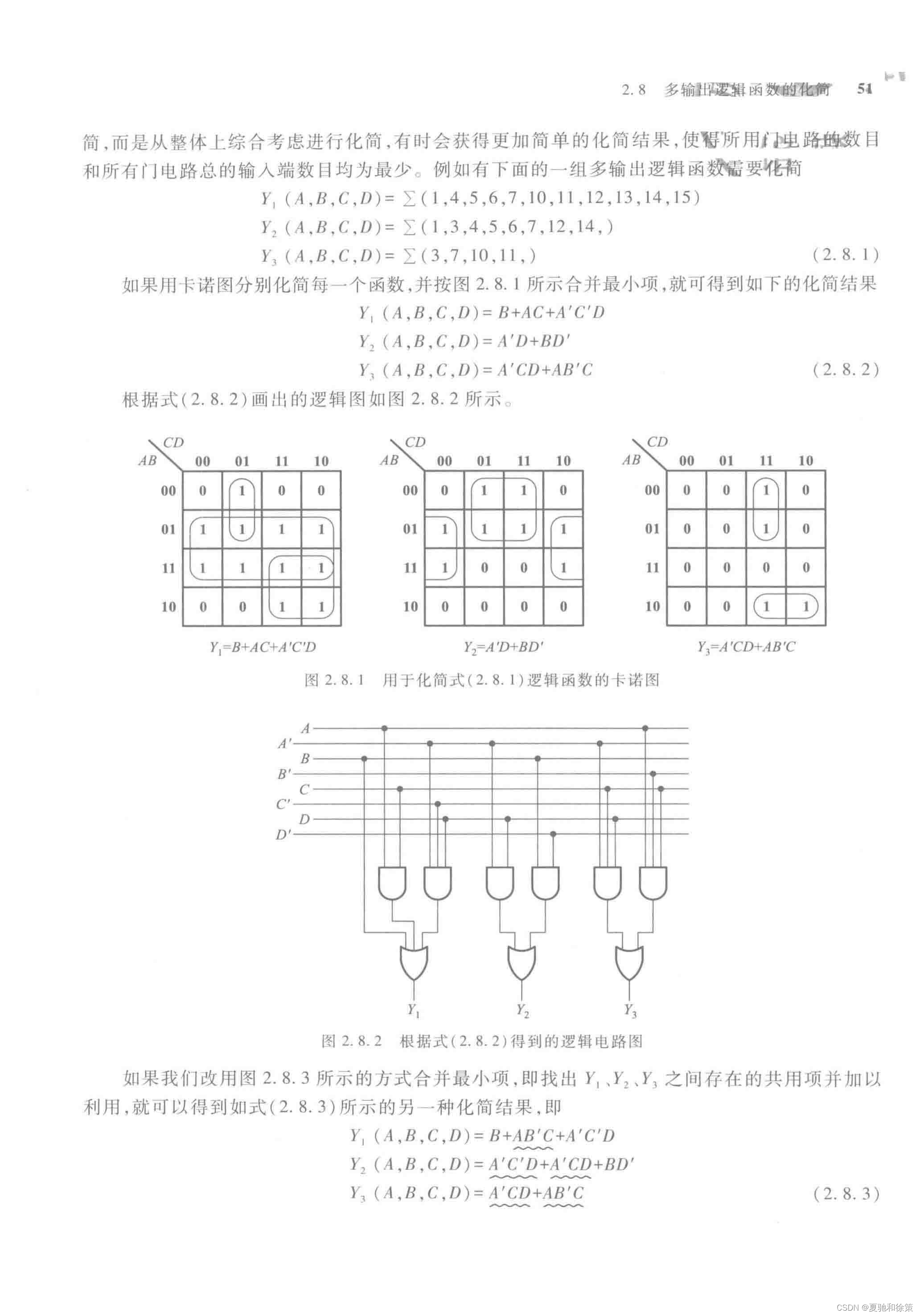

如果我们改用图 2.8.3 所示的方式合并最小项,即找出 𝑌1,𝑌2,𝑌3Y1,Y2,Y3 之间存在的共用项并加以利用,就可以得到如式 (2.8.3) 所示的另一种化简结果,即:

𝑌1(𝐴,𝐵,𝐶,𝐷)=𝐵+𝐴𝐵′𝐶+𝐴′𝐶𝐷Y1(A,B,C,D)=B+AB′C+A′CD 𝑌2(𝐴,𝐵,𝐶,𝐷)=𝐴′𝐶𝐷+𝐴′𝐶𝐷+𝐵𝐷′Y2(A,B,C,D)=A′CD+A′CD+BD′ 𝑌3(𝐴,𝐵,𝐶,𝐷)=𝐴′𝐶𝐷+𝐴𝐵′𝐶Y3(A,B,C,D)=A′CD+AB′C

图 2.8.3 利用公共项化简式 (2.8.1) 逻辑函数的卡诺图

CD

AB

00

00

0

01

1

11

1

10

0

CD

AB

00

00

0

01

1

11

1

10

0

CD

AB

00

00

0

01

1

11

1

10

0

Y1 = B + ABC + ACD

Y2 = ACD + ACD + BD

Y3 = ACD + ABC

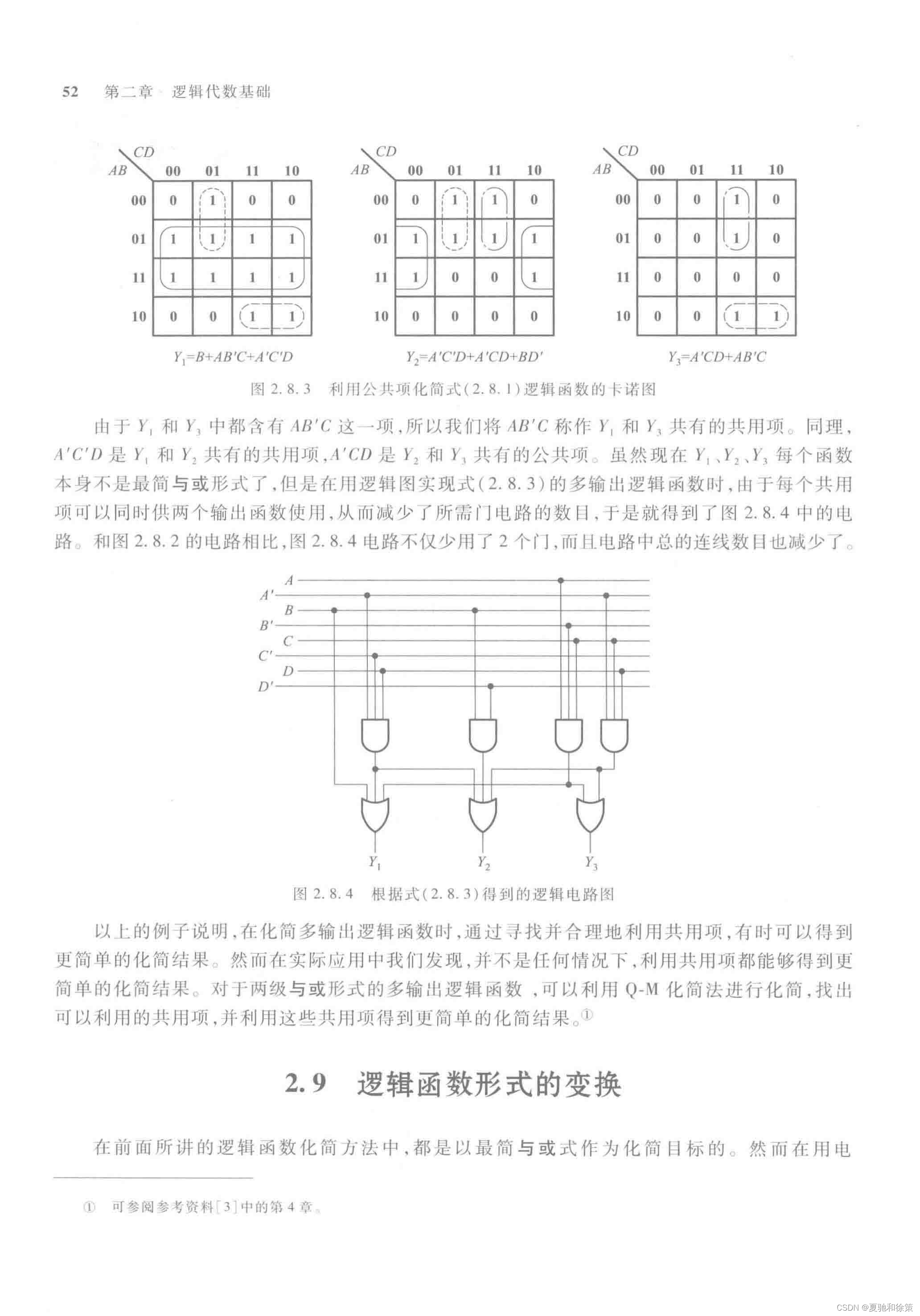

由于 𝑌1Y1 和 𝑌2Y2 中都含有 𝐴𝐵′𝐶AB′C 这一项,所以我们将 𝐴𝐵′𝐶AB′C 称作 𝑌1Y1 和 𝑌2Y2 共有的共用项。同理,𝐴′𝐶𝐷A′CD 是 𝑌2Y2 和 𝑌3Y3 共有的共用项,𝐴′𝐶𝐷A′CD 是 𝑌2Y2 和 𝑌3Y3 共有的公共项。虽然现在 𝑌1,𝑌2,𝑌3Y1,Y2,Y3 每个函数本身不是最简与或形式了,但是在用逻辑图实现式 (2.8.3) 的多输出逻辑函数时,由于每个共用项可以同时供两个输出函数使用,从而减少了所需门电路的数目,于是就得到了图 2.8.4 中的电路。和图 2.8.2 的电路相比,图 2.8.4 电路不仅少用了 2 个门,而且电路中总的连线数目也减少了。

图 2.8.4 根据式 (2.8.3) 得到的逻辑电路图

A'

B

B'

C

C'

D

D'

以上的例子说明,在化简多输出逻辑函数时,通过寻找并合理地利用共用项,有时可以得到更简单的化简结果。然而在实际应用中我们发现,并不是任何情况下,利用共用项都能够得到更简单的化简结果。对于两级与或形式的多输出逻辑函数,可以利用 Q-M 化简法进行化简,找出可以利用的共用项,并利用这些共用项得到更简单的化简结果。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?