0. 引言

之前有段时间时间做过Dram的统计工作,学习了一点Dram的基础知识,写了一篇简单的学习笔记 Dram学习笔记(1) Dram相关基础知识。

后来觉得有些东西还是理解的不是很透彻,比如很简单的例子,当burst = 1, mask burst=1的时候,真实的带宽是多少?以前觉得是burst包含了mask burst,后来和我们的dram controller的设计者请教了一下才发现不是这样的。

由此感觉自己掌握的自己基础知识太少了,所以想找资料看看。

网上的资料参差不齐,很难成体系,很幸运最后找到了一本书《终极内存技术指南》,这本打印出来看的,但是在网上找到的2个版本都是带水印的,“存储时代”水印或者“电脑高手”水印,也并没有找到正式出版的书籍,pdf资源我放在这里。

书有一点老,DDR3之后的就没怎么介绍,不过没关系,基础原理都是一样的,无非是升频率和加prefetch,如果后面用了什么特殊的技术,我相信一般人(包括我也是)也不需要理解。毕竟不是专门做Dram控制器的。

还看到一本推荐 《memory system cache dram disk》,这本还没看,算是一本教科书式的文档了吧,等我有空拜读完再跟大家分享。

我觉得比较好的记忆方式就是自己能动态的想像出来一次burst的流程,数据是怎么读写拼接起来的。

脑海里有一副动画在跑。

1. Dram 名词解释

刚开始的时候必须理解一些基本名词,不然很多文看不懂,毕竟大家都是使用简写的。

有些名词说实话还是挺绕的,A位宽B位宽C频率D频率的。

还是要搞搞清楚。

我把一些很容易混淆的名词放在一起,做个比较。

-

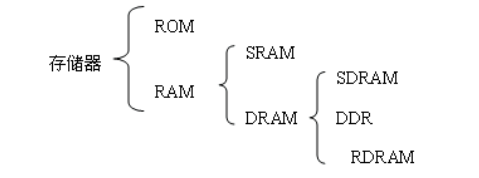

SRAM 、DRAM、SDRAM、DDR

- SRAM

- DRAM

- SDRAM

synchrous Dynamic Random Access Memory, 同步动态随机存储器。

内部的时钟频率和CPU前端总线的系统时钟频率相同。 - DDR

-

SDRAM、DDR、DDR2、DDR3、DDR4

引用一段

- SDR时代:在最古老的SDR(Single Data Rate SDRAM)年代里,一个时钟脉冲只能在脉冲上沿时传输数据,所以也叫单倍数据传输率内存。这个时期内存的提升方法就是提升内存电路的核心频率。

- DDR时代:但是内存制造商们发现核心频率到了200MHz再提升的话,难度就很大了。所以在电路时钟周期内预取2bit,输出的时候就在上升期和下降期各传输一次数据。所以核心频率不变的情况下,Speed(等效频率)就翻倍了。

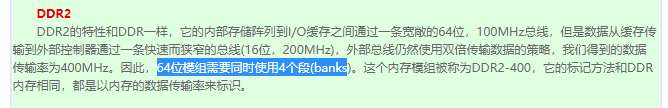

- DDR2时代:同样是在上下沿各传一次数据,但将Prefech提升为4,每个电路周期一次读取4bit。所以DDR2的Speed(等效频率)就达到了核心频率的4倍。

- DDR3时代:同样也是上下沿各传一次数据,进一步将Prefect提升为8。所以DDR3的等效频率可以达到核心频率的8倍。

- DDR4时代:这时预取的提升已经非常困难,所以和DDR3一样,Prefech仍然为8。内存制造商们又另辟蹊径,提出了Bank Group设计。允许各个Bank Group具备独立启动操作读、写等动作特性。所以等效频率可以提升到核心频率的16倍。

-

DDR vs LPDDR

应用场景不同,内部技术也不同。如果论性能的话,DDR的性能始终是高于同代的LPDDR内存的性能的。LPDDR的功耗低于同代的DDR。

LPDDR和DDR之间的关系非常密切,简单来说,LPDDR就是在DDR的基础上面演化而来的。

LPDDR2实在DDR2的基础上演化而来的,

LPDDR3则实在DDR3的基础上面演化而来的,

但是从第四代开始,两者之间有了差别或者说走上了不同的发展,主要因为DDR内存主要是通过提高核心频率从而提升性能,而LPDDR则是通过提高Prefetch预读取位数而提高使用体验。

拿LPDDR4和DDR4来说,LPDDR4是用两个16位通道组成32位总线,而DDR4却具备原生64位通道,LPDDR4的Prefetch预读取位数为16bit,而DDR4为8bit。以后DDR和LPDDR的区别会越来越大。

-

核心频率、工作频率、IO频率、等效频率

简单列个常见表,

- 核心频率是指真正读写内存颗粒的频率,是内存颗粒自有属性,一般是133,166,200 Mhz三类。

这个频率比较难以提升,这也是为什么后面出现了prefetch等技术,出现了不同的发展方向。 - 对于DDR来说,内存工作频率=内存颗粒核心频率x2,因为时钟上下边沿都会读数。

- 等效频率就是对外宣称的频率,加上了预存取功能。

简单总结一下,对于一个DDR,核心频率=A、工作频率=B、IO频率=C、等效频率=D。

则满足

A = 133或者166 或者 200

B = A * 2

C = A * prefetch数

D = A * 2 * prefetch数

- 核心频率是指真正读写内存颗粒的频率,是内存颗粒自有属性,一般是133,166,200 Mhz三类。

-

P-Bank

P-Bank其实就是一组内存芯片的集合,这个集合的容量不限,但这个集合的总位宽必须与CPU数据位宽相符。

内存控制器一次读/写P-Bank位宽的数据

P-Bank是SDRAM及以前传统内存家族的特有概念,现在一般说通道(Channel),因为现在多为并发式多通道DDR。也就是我们看到的主板上面有多个内存条。一般两根内存是一个通道。但是,不排除一根内存一个通道,或多个根内存一个通道。 -

L-Bank

L-Bank是可以并行工作的 -

SIMM / DIMM

Singe / Double In-line Memory Module 。

“simm”即单列直插存储模块,它有30线和70线之分,不过目前30线的simm内存条已经十分少见了,它主要使用在早期的486上,现在较多一些的是72线的simm内存条,这种simm在高档486和早期的586上比较常用。“dimm”即双列直插存储模块,它的引脚有168个,所以也叫做168线内存。

这两种内存的识别方法十分简单,dimm内存采用了直接插入的边缘连接方式,而且dimm内存比较长,simm内存在尺寸上比dimm短许多,安装时必须倾斜插入内存插槽中,再用力扶正,simm两端有两个孔,当simm安装到位时,插槽两端的簧片会嵌入孔中,以固定内存。 -

内存颗粒

其实就是内存芯片,内存晶片,各地叫法不一样。chip。 -

芯片位宽

每个内存芯片有自己的位宽,即每个传输周期能提供的数据量。我理解就是连接芯片的数据线数量。 -

P-Bank位宽

内存总线的数据位宽等同于CPU数据总线的位宽,而这个位宽就称之为物理Bank(Physical Bank,下文简称P-Bank)的位宽。

2. 一些流程步骤的梳理

理解完上面的一堆名词,然后来看读写步骤。

时序图就不看了,跳过了。相关的一些CL,tRCD,tRP 等概念就跳过了。

2.1 内存结构

不能免俗。

2.2 一次burst的实现

假设一个场景,比如SDRAM(不考虑prefetch),CPU位宽64bit,chip位宽16bit,所以1个p-bank是4个chip组成,每个chip里是8个L-bank。

当进行burst的时候,一次burst length一般是4,8。即相当于连续读取4个或者8个cell的数据

2.3 一次mask burst的实现

这块也是不懂,就是开头问同事的部分,感觉不同芯片实现的方式可能不一样?

3. 不懂的地方

3.1 数据在内存里是怎么存放的?

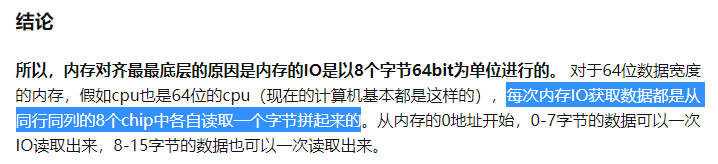

OK,到了这里,我们也弄懂了内存的各种参数,内存读取的方式和流程。

但是还是不明白,数据在内存里是怎么存放的呢?

以前觉得就是图这样的,内存是一大块连续资源,一个个格子,每个格子8bit就是1byte。

用的时候malloc出来一块。

如果内存不够了就再加一块,就串在后面了。

实际上,完!全!不!对!

这个看起来了L bank有点像,但是肯定不是这么存的,不然读写的时候同时选通多个存储芯片的Lbank是做什么的呢,假设CPI位宽64位,L-bank 16位,那每次就要同时选中4个L bank,每个L bank传16bit 。

真实的存储方式见尾部参考链接3,

2021.3.12 补记,这篇文章的图画错了,请忘记它。 应该是多个chip来读,而不是单个chip上的多个bank。作者很认真的画了这张说明图,同时这张图流传的很广,但是实际上是错的。

不过这边文章感觉也有问题,这里作者写64位数据是8个bank,每个bank出8bit来拼成的。

但是位扩展不应该是8个chip拼接,每个chip出8bit,组成64bit吗?

为什么作者这里是写8个bank(我理解就是单个chip中的L-bank)拼接呢?

但是作者最后的结论又感觉是对的。

所以上面那张图是错的,

对的应该是这样的:

3.2 prefetch是怎么实现的?

prefetch是同一时间读取很多位,然后并转串对外输出。

prefetch读取的这个"很多位",是从哪里来的?

是依然读取一个存储单元格,一个cell,但是这个cell扩大了。

还是一次读取多个L-bank的多个cell,单个cell的容量不变?

感觉我在网上找的资料,两种说法都有,很不解。个人认为第一种是对的。

3.2.1 第一种说法:扩大单个cell的容量

这里也是这么说。

3.2.2 第二种说法:同时读取多个bank

这里的bank是指 L-bank 还是 P-bank?

3.2.3 总结

从我个人而言,我比较认可第一种说法。

3.3 为什么DDR1 到 DDR3不停地提高prefetch,DDR4却不能再提高,只能提高核心频率?

在这里找到了答案。

3.4 多个chip是为了做位扩展,使Dram的位宽和cpu cache的位宽保持一致,那多个L-bank 是为了什么?

在 这里 找到了一些解释。

说实话现在找稍微深入一点的解释太难了,CSDN上的文章都是大家抄来抄去(虽然我也是)。

很多东西说的不明不白,甚至还有个人感觉写进来直接带偏……

这篇还好,直接翻译的外文书。

感觉就是提速,换行的时候不用再预充电,那不同L-bank之间的关系是什么?存储的数据内容是什么关系?

这部分还没找到资料,希望有朋友可以告知。

3.5 prefetch和brust length 有关系吗

burst length是可以在控制器里配置的,比如可以选择4或者8。

prefetch是固定的。

不是一个东西。

prefetch是每个cell中间放了几个 chip位宽的数据。

burst length是一次burst去读几个cell。

参考链接

这一篇的参考链接不是介绍一些入门知识,而是解决我的一些理解上的疑惑,所以我列在这里了。

- 论坛资料下载

- 2片16bit的芯片拼一个32bit的芯片

- 参考3 - 实际存储的样子 — 但是觉得有问题,数据拼接应该是多个chip拼接做位扩展?— 确实有错,别看了。看这篇图是对的.正确图–很有意思,发现居然是同一个作者写的。

- 参考4 - 开发内功修炼

- 参考5.1 - 老狼内存系列一:快速读懂内存条标签

参考5.2 - 内存系列二:深入理解硬件原理

参考5.3 - 内存系列三:内存初始化浅析

参考5.4 - 内存系列四:DDR3 vs DDR4

1215

1215

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?